实验时间:9.21

软件版本:Quartus II 9.0sp2 Web Edition

目录

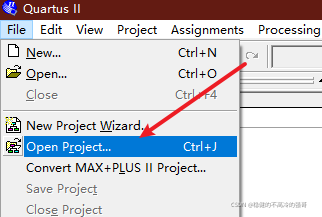

新建项目

FILE——NEW——NEW Quartus II Project 建立工程

working directory(工作目录)自行选择

Project Name 输入DFLOP(最好不要包含空格和中文)

Toplevel Name 也为DFLOP

新建原理图BDF文件

FILE——NEW——Design Files中的Block Diagram 建立原理图

单击工具栏上“与门”图标——添加器件(在Name中可搜索)

Processing——Start Compliation

选择保存为demo.bdf,扩展名不必输入,系统自动给定。

文件名与项目名相同的为,主编译界面,已与后续封装区分

仿真波形VW文件

工程编译完成后,设计结果是否满足设计要求,可以通过时序仿真来分析;

FILE——NEW——Verification Files中的Vector Waveform 建立波形文件

到左边窗格——单击鼠标右键——选快捷菜单中的INSERT

——Insert Node or Bus——弹出Node Finder对话框

添加输入输出节点

单击list按钮——单击〉〉按钮(添加所有节点)

赋予输入随机值

更改仿真模式

将Simulation Mode更改为Functional

单击右侧的按钮“Generate Functional Simulation Netlist” (一定要点,否则出错)

开始仿真

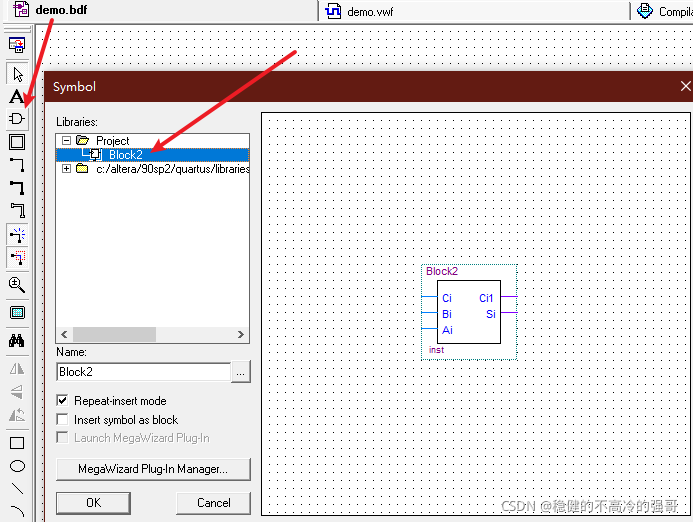

封装组件BSF文件

先new一个项目,测试电路图,逻辑完全正确后,再在新的项目中封装。

先new一个新项目,在newBDF文件,然后将电路图复制粘贴进去。

Ctrl + S保存,不要与项目名相同,创建bsf文件。

封装的BDF,BSF文件都不可以删除!!!!

封装完成后,即可在项目名同名的BDF文件中使用了。

总线输入/输出

总线代表输入输出多个数据。

打开之前的项目QPF文件