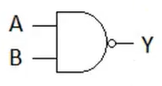

与非门符号:

与非门真值表

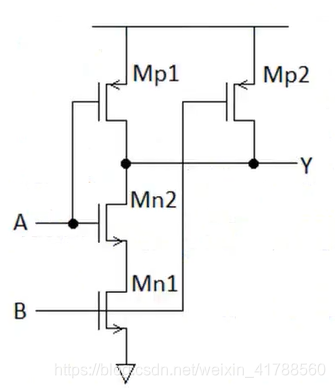

与非门电路原理图

与非门Verilog代码:

`timescale 1ns/10ps

module nand_gate(

A,

B,

Y

);

input A;

input B;

output Y;

assign Y=~(A&B); //assign组合逻辑赋值语句

//先与后非,与非操作,Verilog位操作

endmodule测试代码testbench

//-----testbench of nand_gate

module nand_gate_tb;

reg aa,bb;

wire yy;

//异名例化

nand_gate nand_gate(

.A(aa),

.B(bb),

.Y(yy)

);

initial begin

aa<=0;bb<=0;//reg型变量赋值用带箭头的等号

#10 aa<=0;bb<=0;

#10 aa<=0;bb<=0;

#10 aa<=0;bb<=0;

#10 $stop;//调用$stop系统任务

end

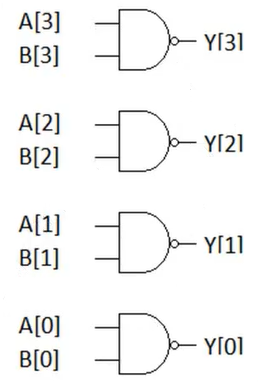

endmodule四位与非门Verilog代码与测试代码

//四位与非门

`timescale 1ns/10ps

module nand_gate_4bits(

A,

B,

Y

);

input[3:0] A;

input[3:0] B;

output[3:0] Y;

assign Y=~(A&B);

endmodule

//-----testbench of nand_gate_4bits

module nand_gate_4bits_tb;

reg[3:0] aa,bb;

wire[3:0] yy;

nand_gate_4bits nand_gate_4bits(

.A(aa),

.B(bb),

.Y(yy)

);

initial begin

aa<=4'b0000;bb<=4'b1111;//表示四位

#10 aa<=4'b0010;bb<=4'b0110;

#10 aa<=4'b0111;bb<=4'b0100;

#10 aa<=4'b0000;bb<=4'b1110;

#10 $stop;

end电路原理图:

版权声明:本文为weixin_41788560原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。