定点数的加减运算

加法运算规则

- [ x + y ] 补 = [ x ] 补 + [ y ] 补 [x+y]_补=[x]_补+[y]_补[x+y]补=[x]补+[y]补

补码加法的特点

- 符号位作为数的一部分一起参加运算

- 在模2 n + 1 2^{n+1}2n+1的意义下相加,即超过模的进位会丢掉,但是不影响结果的准确性

减法补码运算有两个等式

- [ − y ] 补 = ! ( ∣ y ∣ 补 ) + 1 [-y]_补=!(|y|_补)+1[−y]补=!(∣y∣补)+1

- [ x − y ] 补 = [ x ] 补 − [ y ] 补 = [ x ] 补 + [ − y ] 补 [x-y]_补=[x]_补-[y]_补=[x]_补+[-y]_补[x−y]补=[x]补−[y]补=[x]补+[−y]补

补码的减法运算转换为补码的加法运算来运算

定点加减运算的溢出检测

- 在定点整数机器中,数的表示范围为:∣ x ∣ < 2 n − 1 |x|<2^n-1∣x∣<2n−1,在运算过程中出现大于绝对值的现象

- 上溢表示两个正数相加运算结果超过了机器所能表示的正数的最大范围

- 下溢则为两个负数相加运算结果超过了机器所能表示的负数的最大范围

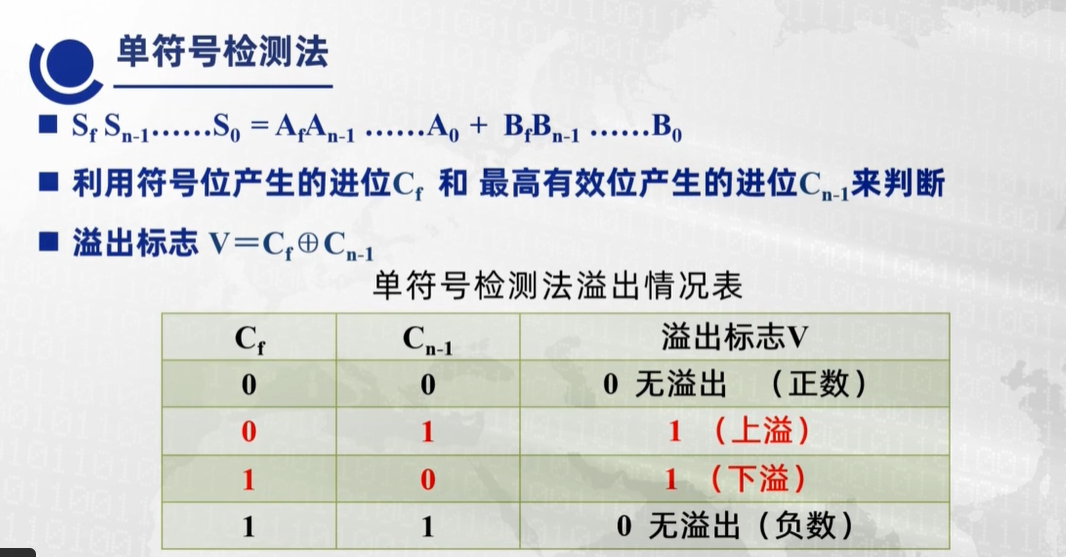

单符号检测法

即当符号位和最高有效位产生的进位异或为1时发生了溢出。

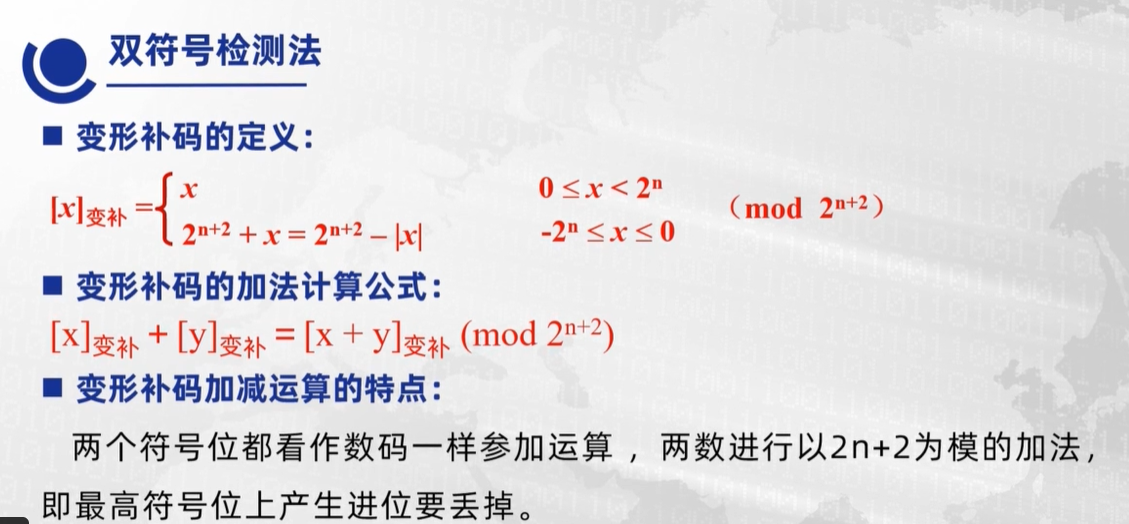

双符号检测法

- 变形补码的定义:

[ x ] 变补 = { 2 n + 2 + x = 2 n + 2 − ∣ x ∣ x [x]_{变补}=\{^{x}_{2^{n+2}+x=2^{n+2}-|x|}[x]变补={2n+2+x=2n+2−∣x∣x

- 加减运算是否溢出要看最高的两个符号位判断,如果异或为1表示发生了溢出

- 无论溢出与否,最高符号位表示正确的符号,不受影响

定点数的加减运算器

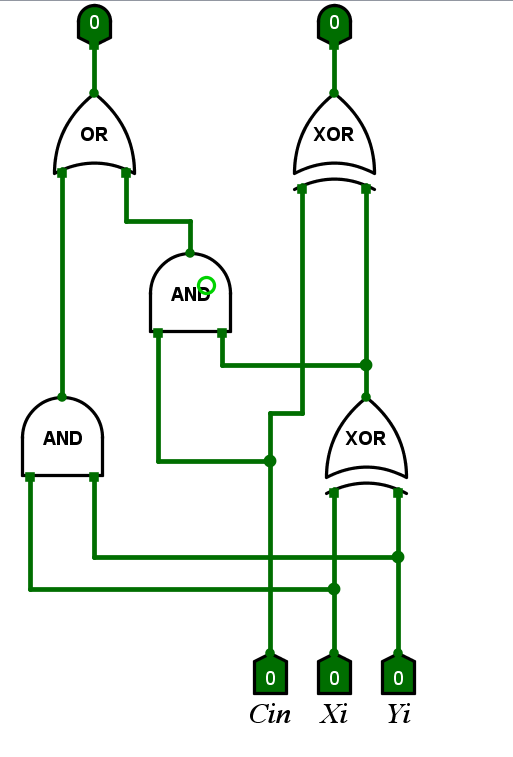

一位全加器

真值表

| A i A_iAi | B i B_iBi | C i C_iCi | S i S_iSi | C i + 1 C_{i+1}Ci+1 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

逻辑表达式

S i = A i ⊕ B i ⊕ C i C i + 1 = A i B i + ( A i ⊕ B i ) C i S_i=A_i\oplus B_i\oplus C_i \\ C_{i+1}=A_iB_i+(A_i\oplus B_i)C_iSi=Ai⊕Bi⊕CiCi+1=AiBi+(Ai⊕Bi)Ci

逻辑电路图

延迟时间

通常采用一个与非门或一个或门来作为延迟时间的度量单位T

一个异或门的延迟时间为3T

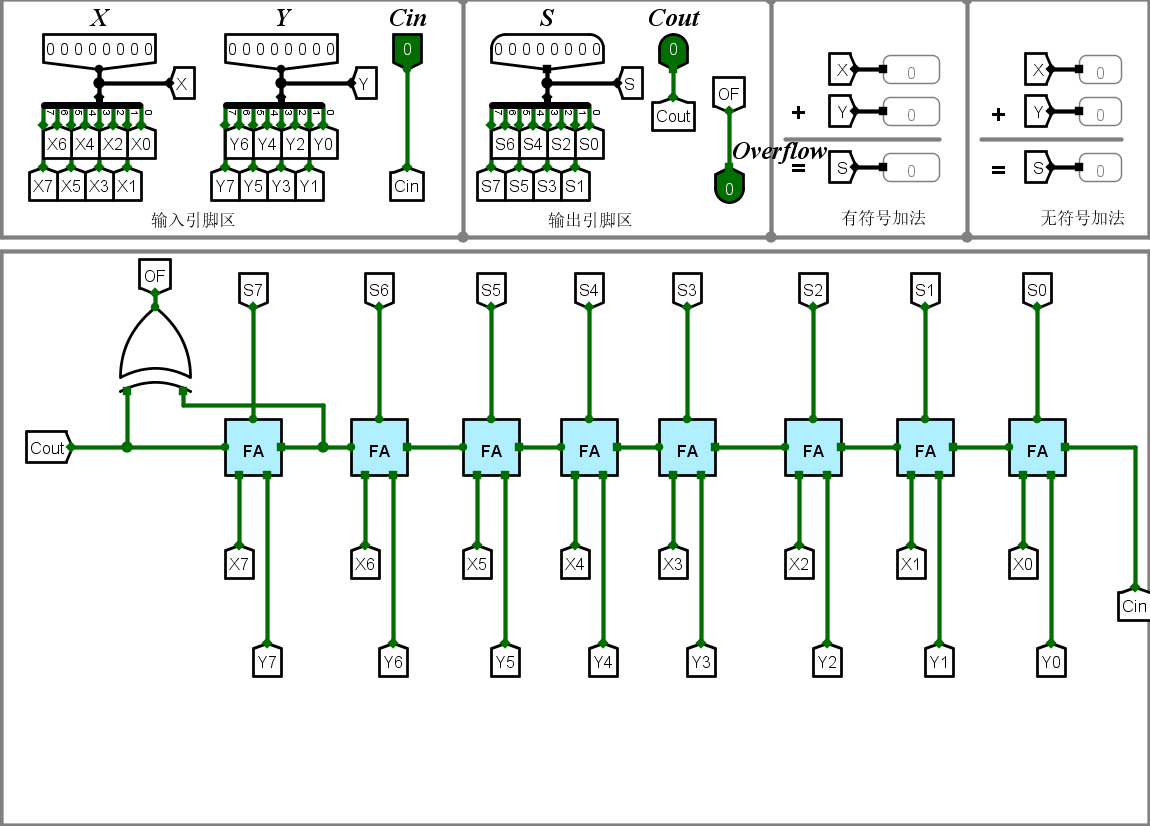

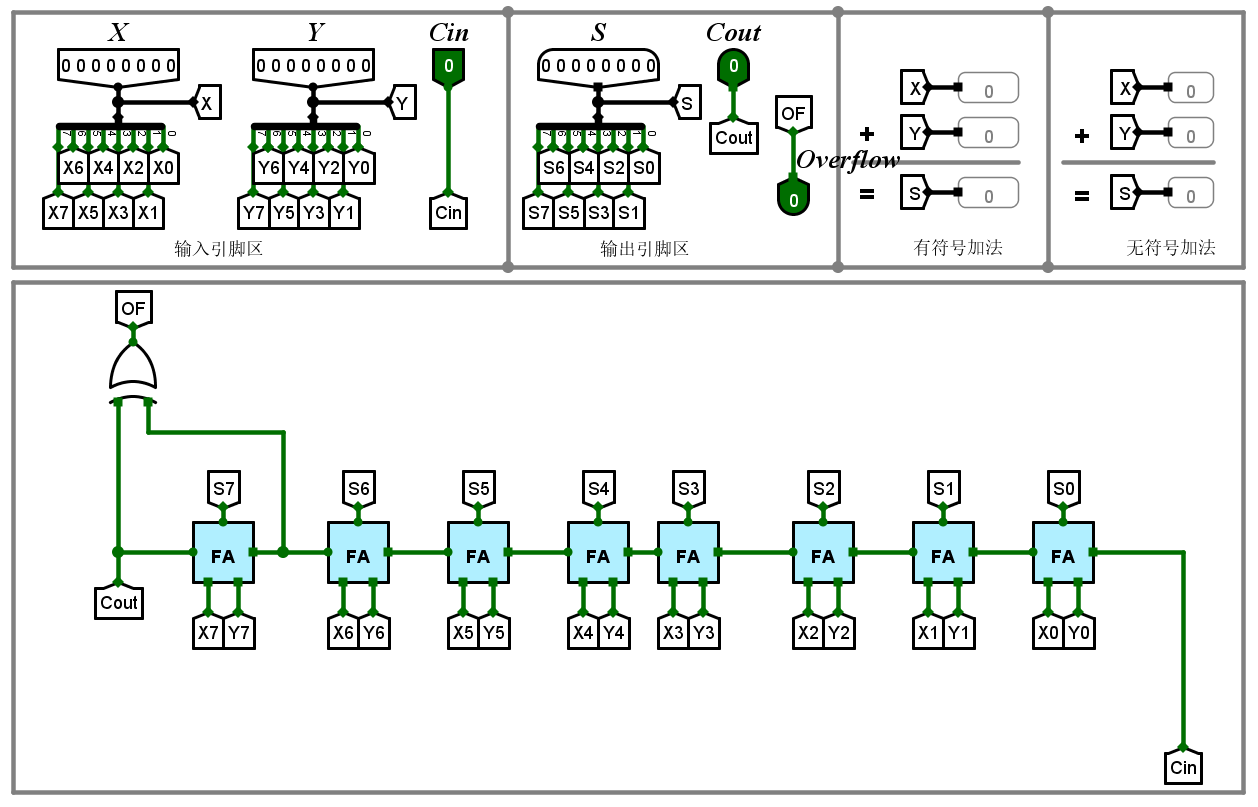

八位串行加法器

八位可控加减法器

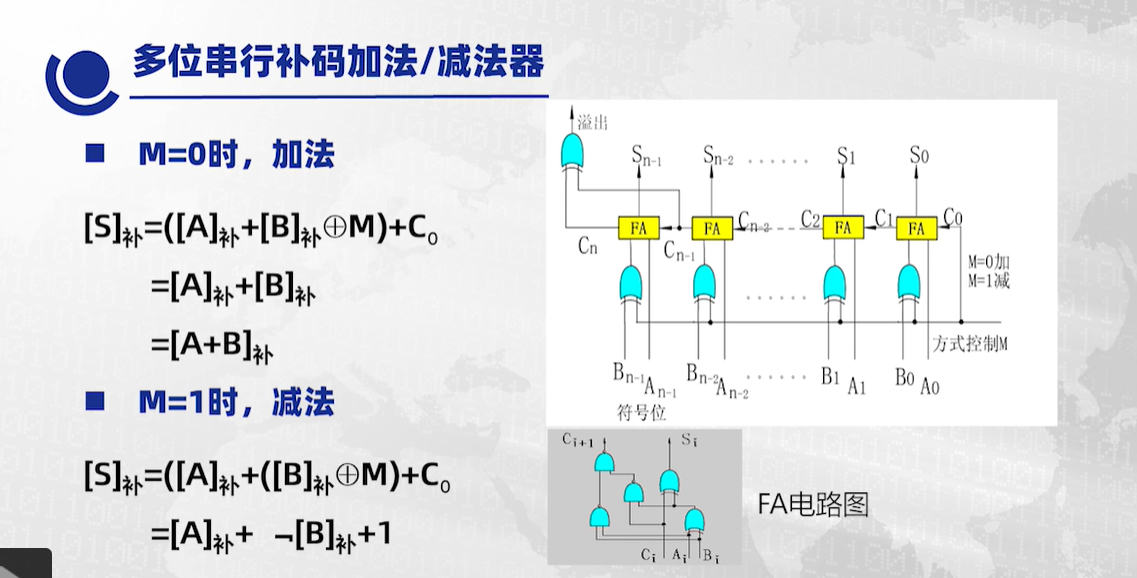

多位串行补码加法减法器

对于溢出检测

V = C n ⊕ C n − 1 V=C_n\oplus C_{n-1}V=Cn⊕Cn−1

C n C_nCn是符号位的进位标志,C n − 1 C_{n-1}Cn−1是最高有效位的进位标志

异或为1表示有溢出

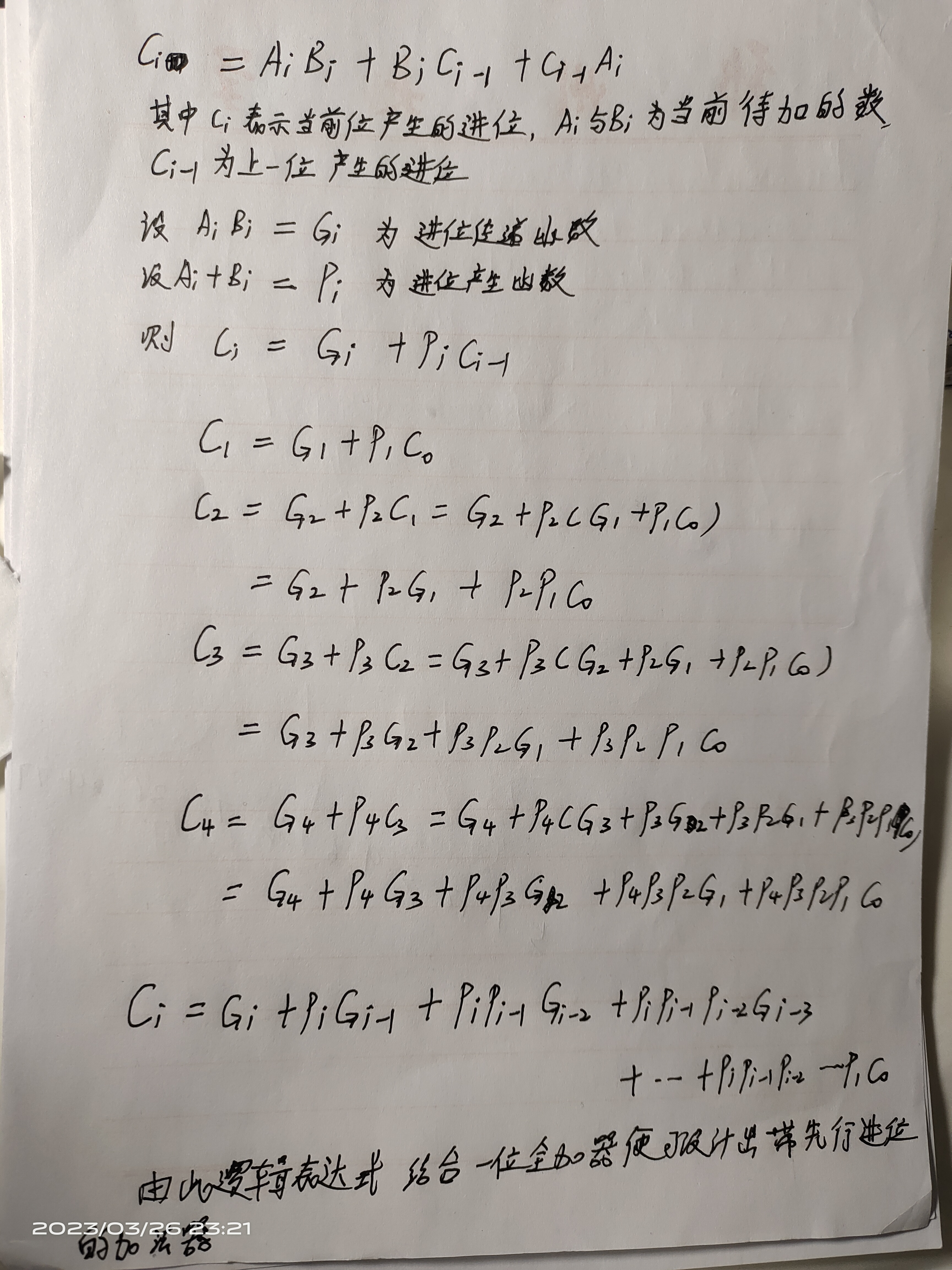

四位先行进位加法器

对于之前的串行加减法计算器,我们由于不知道每一位的进位如何,因此必须由低到高一位一位的进行,在当前位计算完毕后才能够知道下一位的进位,这样产生的时间消耗很长,为了解决这个问题,有了先行进位加法器:

首先,对于一位全加器而言,它所产生的进位位:

C i + 1 = A i B i + B i C i + C i A i C_{i+1}=A_iB_i+B_iC_i+C_iA_iCi+1=AiBi+BiCi+CiAi

我们可以看出,下一位的进位如果知道了当前位的两个加法数和前一位的进位,就能够计算出向下一位的进位

我们做出如下声明:

设 G i = A i B i 为进位传递函数 设 P i = A i + B i 为进位产生函数 那么加法器进位信号就可以表示为: C i + 1 = G i + P i C i 设G_i=A_iB_i 为进位传递函数\\ 设P_i=A_i+B_i为进位产生函数\\ 那么加法器进位信号就可以表示为:\\ C_{i+1}=G_i+P_iC_i设Gi=AiBi为进位传递函数设Pi=Ai+Bi为进位产生函数那么加法器进位信号就可以表示为:Ci+1=Gi+PiCi

由以上得出的递推公式就可以计算出每一位产生的进位

C 1 = G 0 + P 0 C 0 C 2 = G 1 + P 1 ( G 0 + P 0 C 0 ) = G 1 + P 1 G 0 + P 0 P 1 C 0 C_1=G_0+P_0C_0\\ C_2=G_1+P_1(G_0+P_0C_0)\\=G_1+P_1G_0+P_0P_1C_0C1=G0+P0C0C2=G1+P1(G0+P0C0)=G1+P1G0+P0P1C0

由此便可以得出每一位的进位,便可以将串行运算改为并行运算,大大的提高了计算速度。

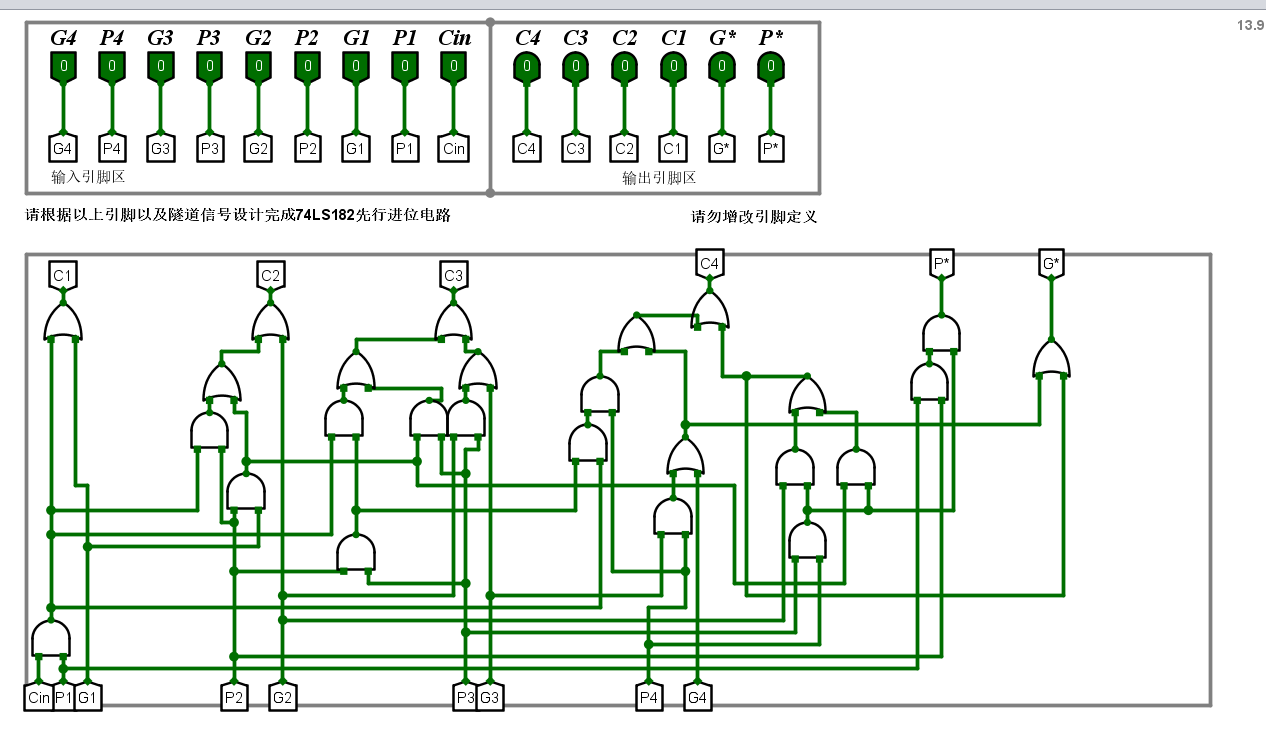

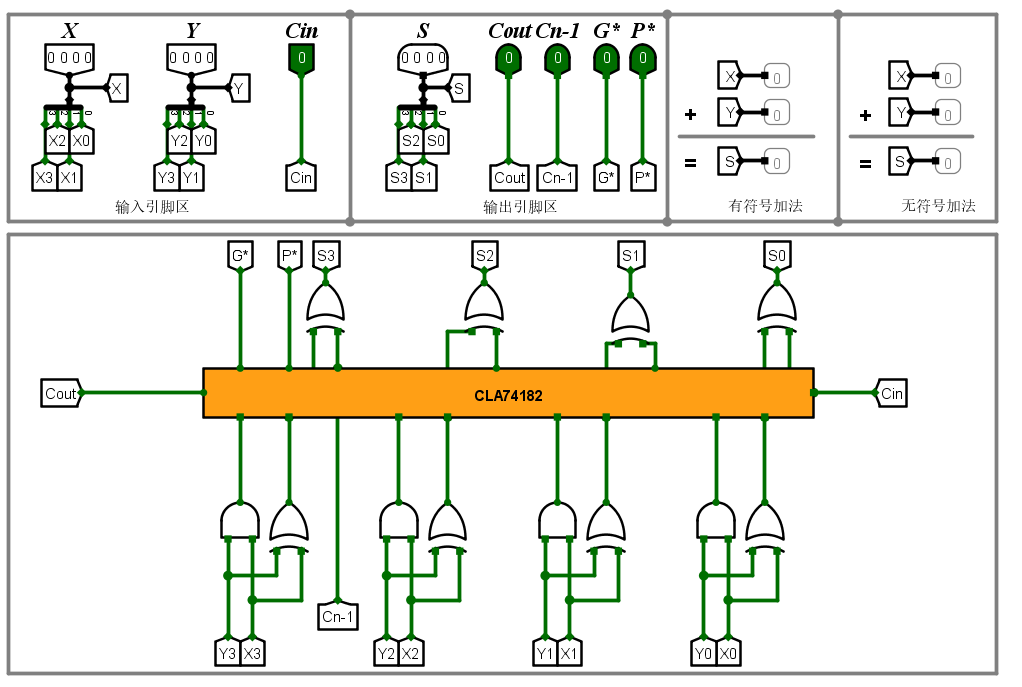

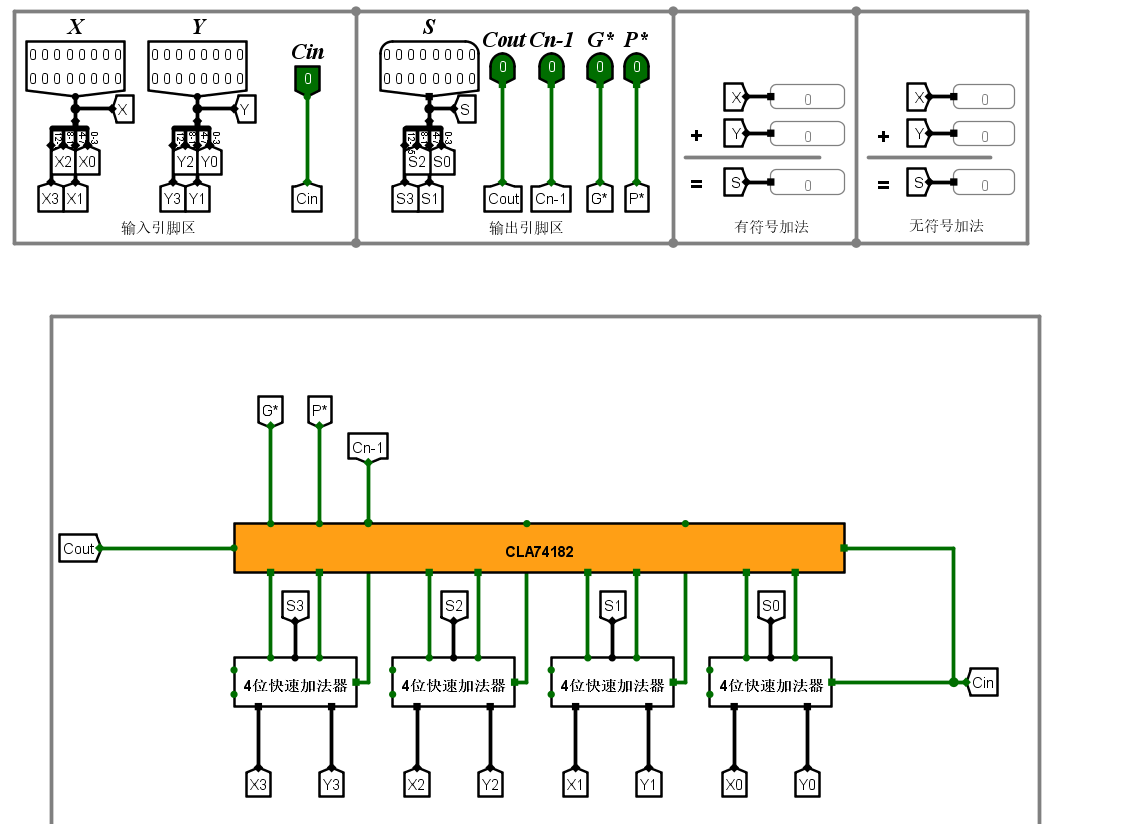

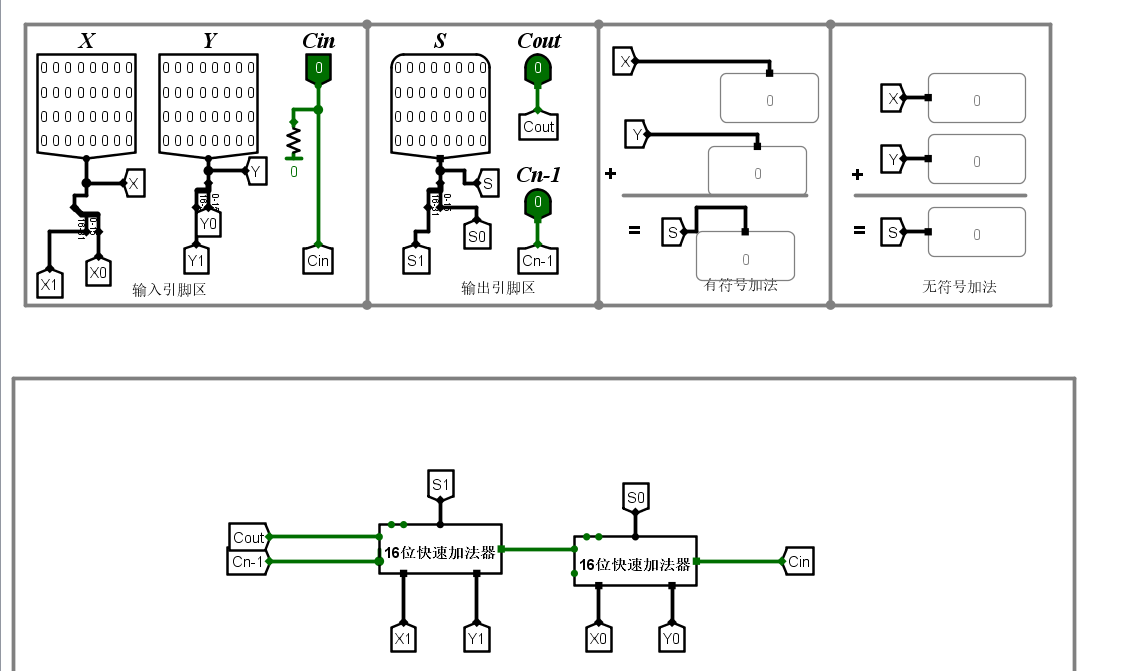

74LS182先行进位电路

四位快速加法器

十六位快速加法器

三十二位快速加法器

定点数的乘法运算及其运算器

计算机中实现乘法运算通常有三种方法

- 软件实现

- 因为在机器中没有设置相应的乘法指令

- 在原有实现的加减运算器的基础上增加一些逻辑线路,令乘除运算变换为累和移位操作

- 也是因为机器中没有相应的乘法指令

- 乘法器

- 机器专门设置一个乘法指令

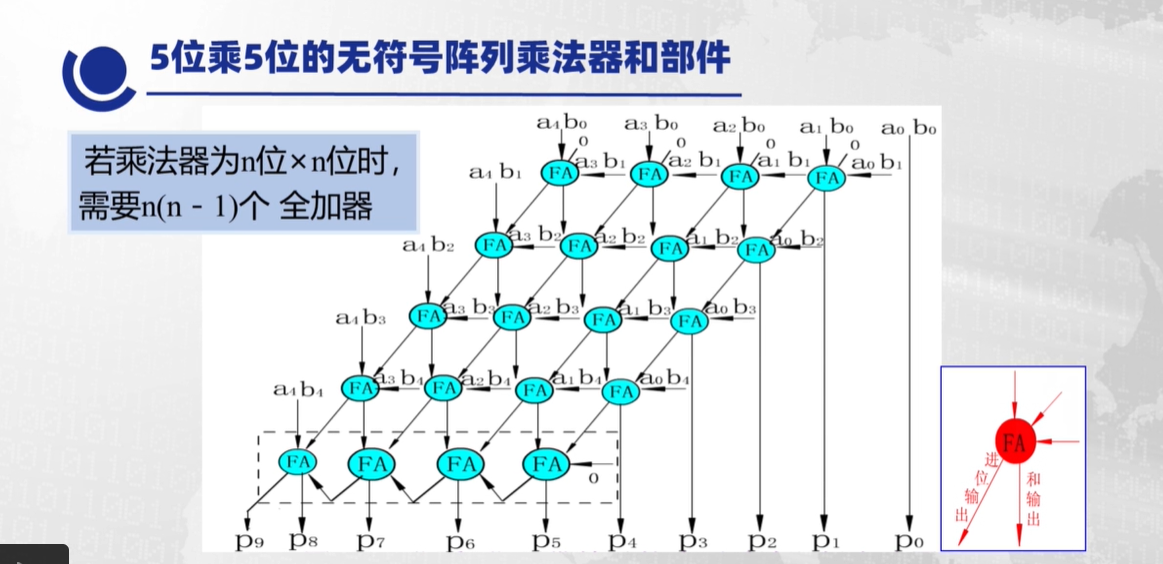

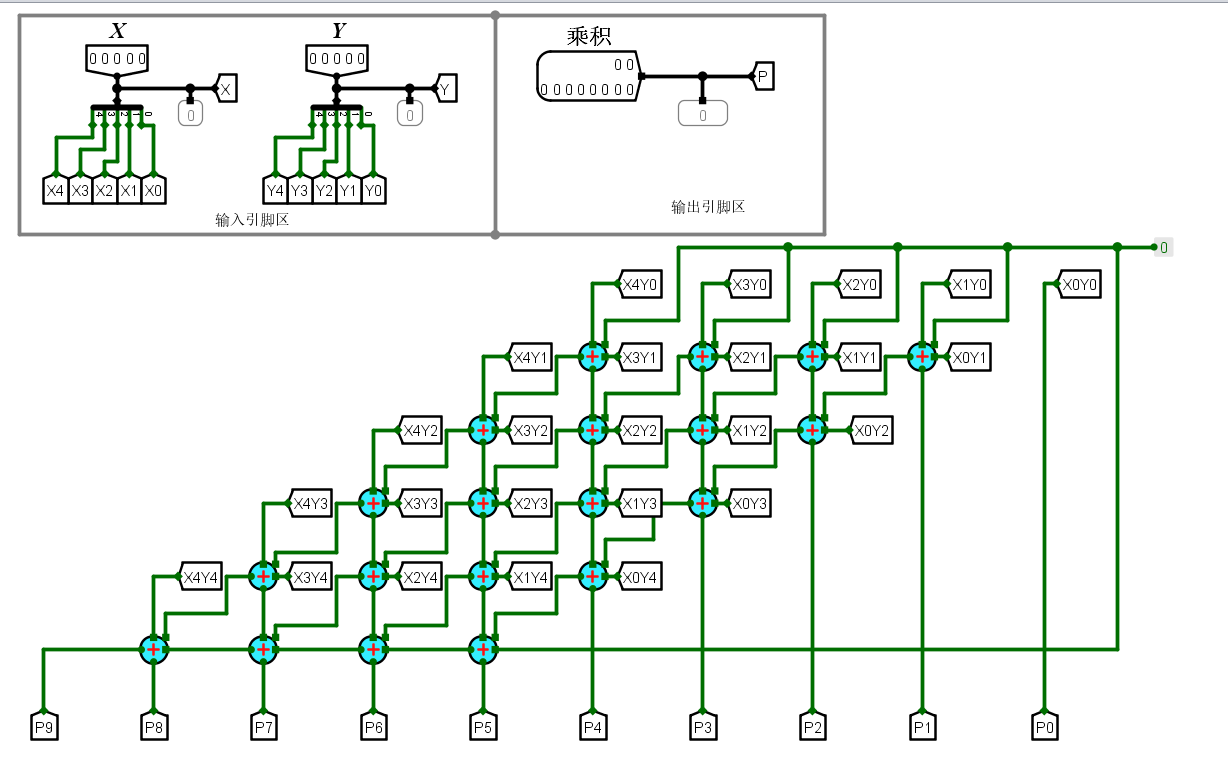

五位阵列乘法器原理图

不带符号的五位阵列乘法器

原码并行乘法器

两个原码表示的数相乘的运算规则:

乘积的符号位由两数的符号位异或得到,而乘积的数值部分则是两个正数的乘积

因此使用一个异或门和一个无符号阵列乘法器就可以完成运算

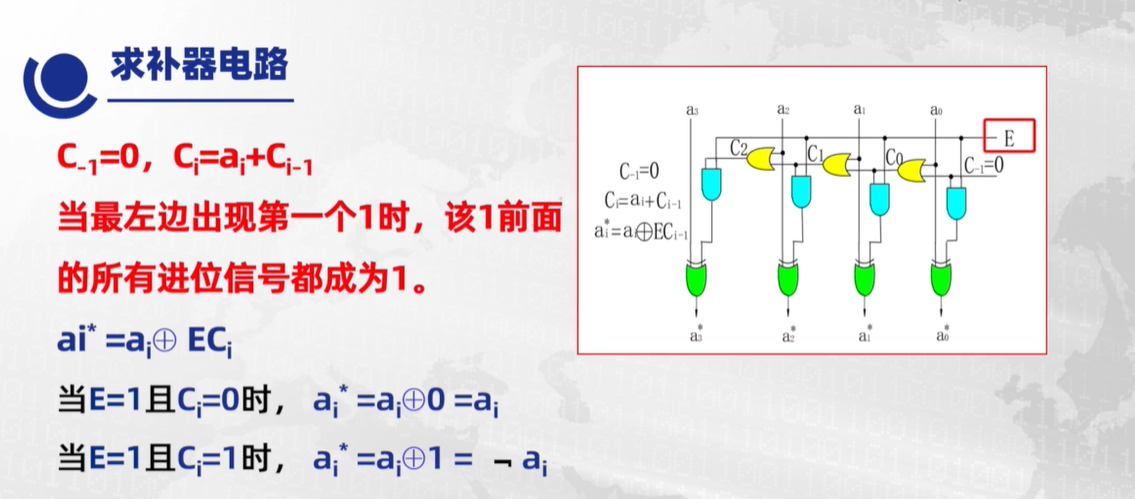

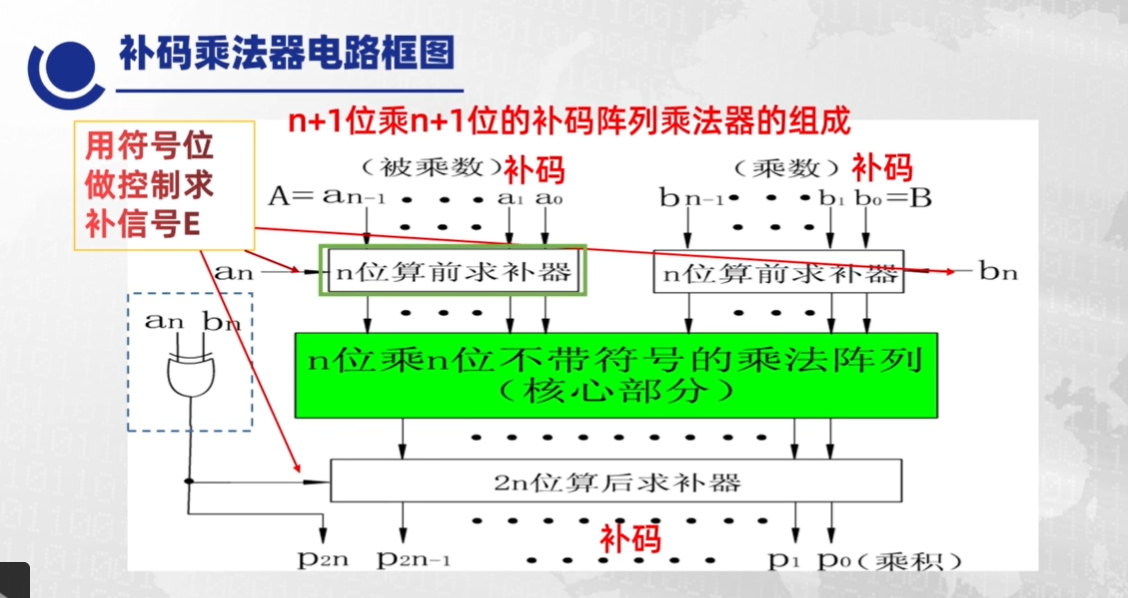

补码阵列乘法器

上图是求补电路,即求补码

原理如下:

当E为1的时实现的逻辑功能是求负数的补:

所有的与门电路一条路线为1,故而输出结果却决于另外一个输入即C i C_iCi

此时若C − 1 C_{-1}C−1为0,那么与门输出一定为0,向下的异或门输出取决于它的另外一个输入即输出a 0 a_0a0,如果a 0 a_0a0为0,那么下一位位输出不变,如果a 0 a_0a0为1,那么下一位的输出取反,而且由于是一系列的或门,因此后面的或门输出全为1,即全取反,由此便完成了取补操作。

如果E为0那么输出不变

原码除法运算原理

商的符号由两数的符号位异或求得,商的数值部分由两数的数值部分相除得到

在定点小数的原码除法运算中:

要求∣ x ∣ < ∣ y ∣ ,保证:商 q = x / y 也是小数 |x|<|y|,保证:商q=x/y也是小数∣x∣<∣y∣,保证:商q=x/y也是小数

首先我们设被除数为x,除数为y,均为二进制表示

然后计算x-y,即x加-y的补码,看余数,如果余数为正,表示够减,由于是二进制,因此商只能够上1或者上0,也就是只有够减一次和不够减两种情况。

如果余数为负则表示不够减,需要余数上0。

此时,如果余数为正,商上了一

设当前的余数为r

r i = x − y > 0 r i + 1 = r − y / 2 = x − y − y / 2 r_i=x-y>0\\ r_{i+1}=r-y/2=x-y-y/2ri=x−y>0ri+1=r−y/2=x−y−y/2

上式符合我们通常的除法运算,如果当前够除了,那么会将除数右移一位然后再对余数进行除法此时,如果余数为负,商上了0

r i = x − y < 0 r_i=x-y<0\\ri=x−y<0

我们知道了此时是不够减的,因此不能够减,按照我们通常的除法运算来讲,上面一步不应该是存在的,而应该是除数右移一位,然后再判断对于当前值是否可除,对于二进制来讲,较为简单,我们只需要右移判断够不够减即可:

r i + 1 = r i + y / 2 = x − y / 2 r_{i+1}=r_i+y/2=x-y/2ri+1=ri+y/2=x−y/2

从上面的式子可以看出,这一步加法和上面的减法合在一起就成为了x减去除数右移一位,这样刚好符合我们的运算方法按照上面的规则重复至小数位算尽或者达到要求即可

并且每一步运算的进位标志与q即商位的值相等

q=0位加,q=1为减,因此可以控制下一步运算的加减

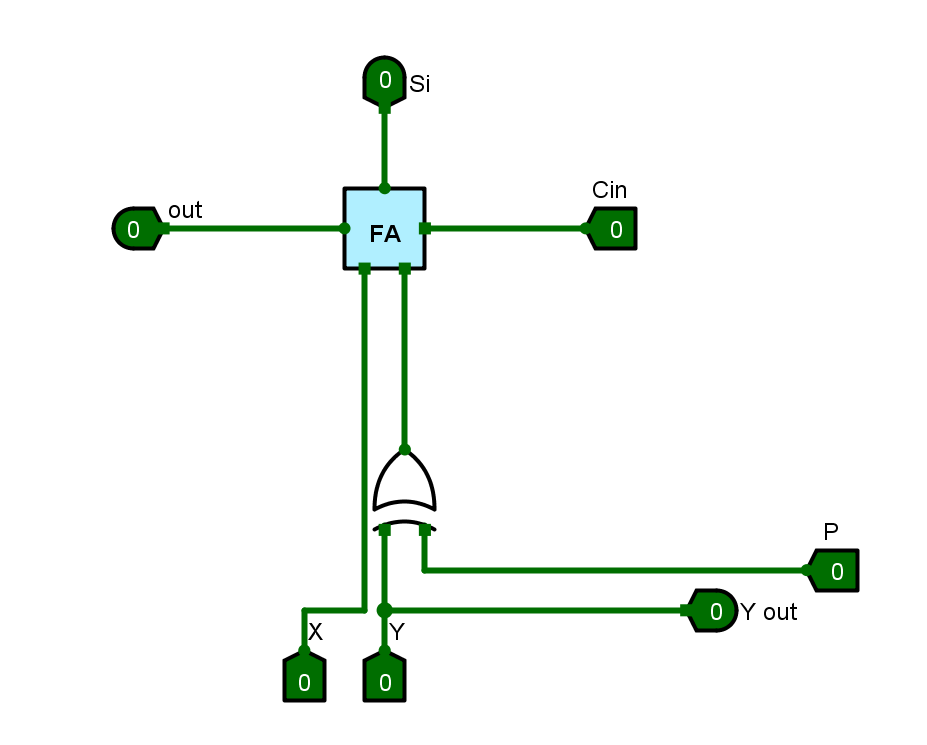

可控加减法逻辑电路

真值表如下

A、B是当前位的运算数据,C是来自上一位的进位或借位,P是控制信号,0时控制做加法,1时控制做减法,S表示计算结果,C I + 1 C_{I+1}CI+1表示向高位的进位

| A | B | C i C_iCi | P | S | C i + 1 C_{i+1}Ci+1 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 0 |

卡诺图

真值表有点长,我们先来画个卡诺图

下面是对于S的卡诺图

| 1 | 1 | ||

|---|---|---|---|

| 1 | 1 | ||

| 1 | 1 | ||

| 1 | 1 |

我们写出他的最简表达式有:

S = A ‾ B C ‾ i + A B ‾ C ‾ i + A ‾ B ‾ C i + A B C i S=\overline A B\overline C_i+A\overline B\overline C_i+\overline A\overline BC_i+ABC_i\\S=ABCi+ABCi+ABCi+ABCi

注

经由上面的真值表运算出最后的逻辑表达式,发现与书中的逻辑表达式一点儿也不相符。最后发现原因如下:

CAS可控加法减法单元不是直接实现加法减法的逻辑单元,而是在P控制信号为0时做FA全加器即带进位的加法运算。而当P为1时,如果来自低位的借位为0,那么运算的是A加上(B的反码),只有当来自低位的借位即C i C_{i}Ci为1时,运算的结果是A + ( B 反 + 1 ) A+(B_反+1)A+(B反+1)即A + ( − B ) 补 A+(-B)_补A+(−B)补即A − B A-BA−B

因此如果要控制CAS单元做加法减法运算需要控制来自低位的进位/借位,当P为1控制做减法时需要来自低位的借位一定为1.

一位可控加减法单元

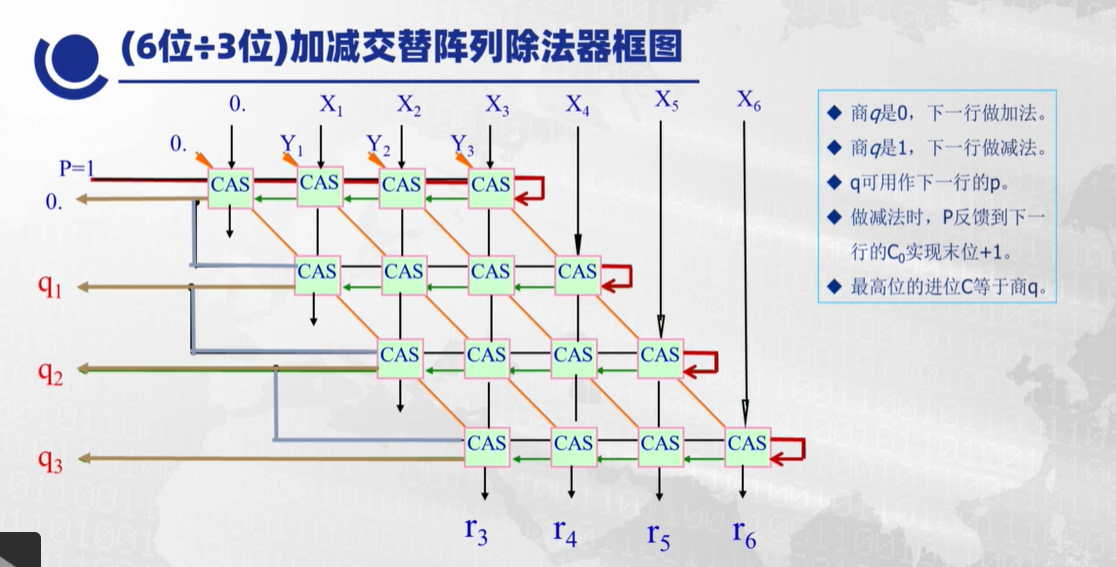

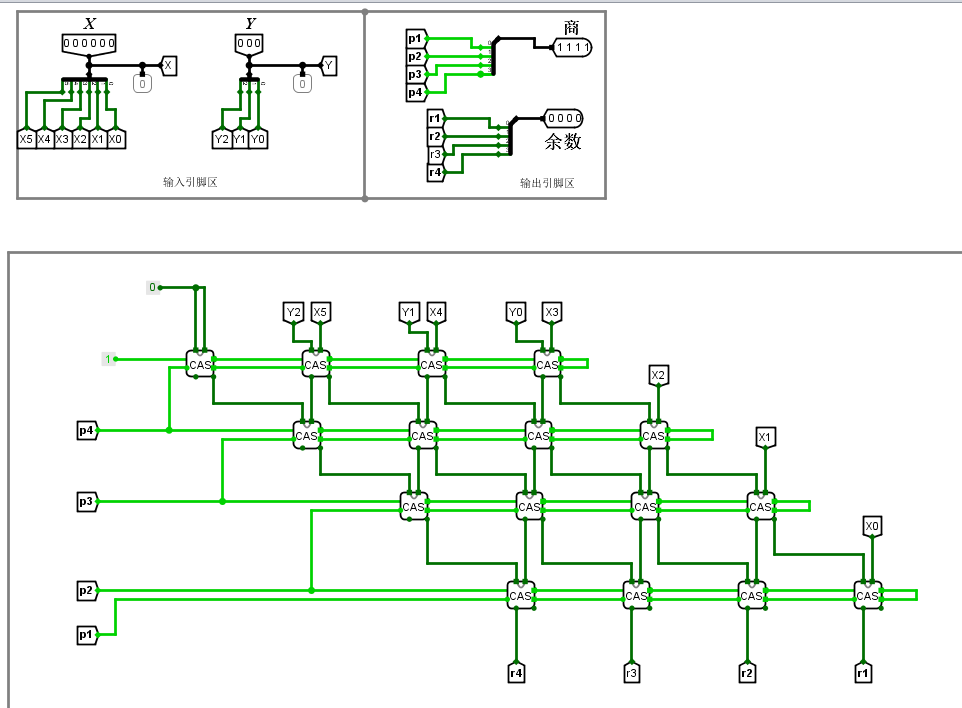

加减交替法阵列除法器

根据上面的逻辑有如下阵列除法器逻辑:

以6/3阵列除法器为例

纯小数的小数点对齐,然后先进行一次减法,即令P为1,然后会得到一个这一行的进位C i C_iCi,如果这个C为0,表示减法运算(即补码加法运算)没有进位,也就是结果为负,符号位为1,商上0,应该控制下一次运算为加法运算,如果这个C为1,表示补码加法运算有了进位,也就是结果为正数,商上1,下一次运算应该为减法运算,这个向高位的进位C刚好可作为控制下一行运算的控制信号,并且可以作为当前位的商值,因此将这个进位输出当作商并且接入下一行作为控制信号。如此往复直到得到指定位数的余数。

不恢复余数的阵列除法器

逻辑运算与移位操作

逻辑数

- 不带符号的二进制数

四种基本逻辑单元

- 逻辑非

- 逻辑加

- 逻辑乘

- 逻辑异或

利用逻辑运算计算机可以进行两个数的比较,或者从某个数中选取某几位等进行操作

逻辑非

对某数进行按位取反,常用变量上方加一横线来表示。

逻辑加

即按位求或运算

逻辑乘

按位求与

逻辑异或

即按位求异或

移位

有左移和右移两种

按照性质划分为逻辑移位、算术移位、循环移位三种

逻辑移位

认为为无符号数或纯逻辑代码

左移右移空位均填0

算术移位

操作对象为带符号数

- 原则

以为后保持数的符号位不变,数值大小发生变化

左移一位相当于该数乘以2,符号位不变其他位左移

右移一位相当于该数除以2,符号位不变其他位右移

原码右移左移均补0,如果左移前最高有效位已经为1,那么左移将溢出

补码右移填充符号位,移出的位一般会保存在CF中

补码左移填0,移位过程中如果符号位发生变化即发生了溢出

循环移位

首尾相连进行移位

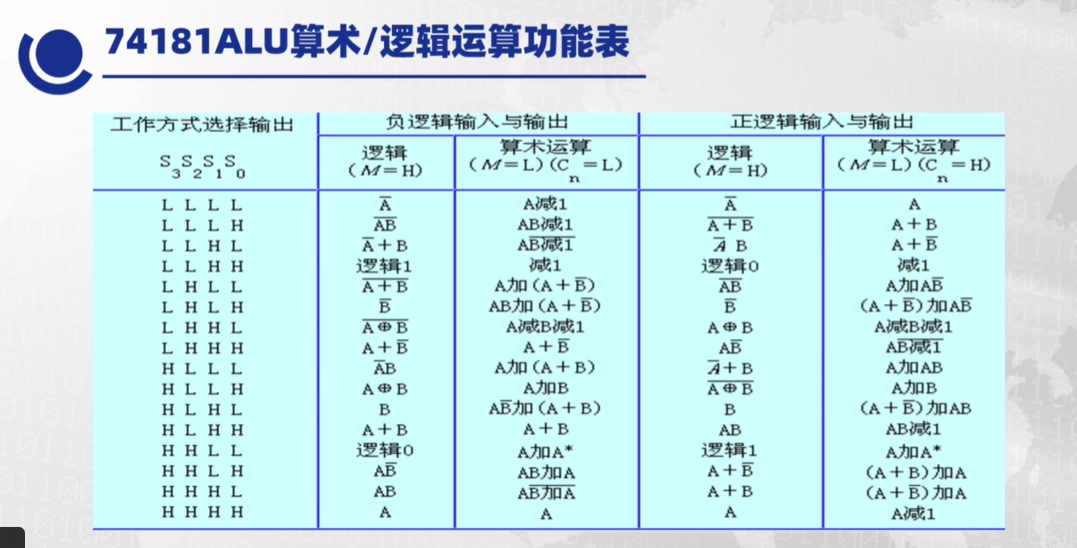

多功能算术/逻辑运算单元(ALU)

我们为了将全加器的功能扩展,设计出多功能算术逻辑运算单元,可以将全加器的输入经由一个特殊的逻辑电路我们称之为函数发生器,然后再接入全加器,这样改变函数发生器的控制信号,就可以改变输入的A和B的值,这样就可以实现多种运算,下面是74LS181的控制参数表即经由函数发生器后A与B的值:

| S 0 S 1 S_0S_1S0S1 | Y i Y_iYi | S 2 S 3 S_2S_3S2S3 | X i X_iXi |

|---|---|---|---|

| 00 | A i ‾ \overline {A_i}Ai | 00 | 1 |

| 01 | A ‾ i B i \overline A_iB_iAiBi | 01 | A ‾ i + B ‾ i \overline A_i+\overline B_iAi+Bi |

| 10 | A i ‾ B ‾ i \overline {A_i} \overline B_iAiBi | 10 | A ‾ i + B i \overline A_i+B_iAi+Bi |

| 11 | 0 | 11 | A i A_iAi |

下图是74LS181ALU算术逻辑运算器的功能表,其中汉字加是算术加即有进位,符号+是逻辑加即按位求或

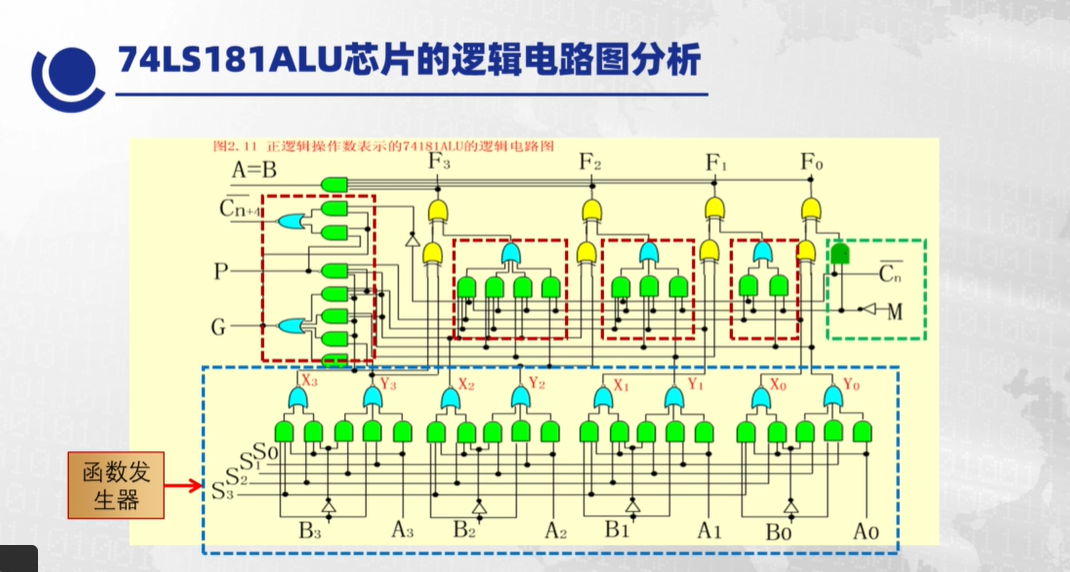

下图是74LS181的逻辑电路图分析,红色区域是全加器的先行进位信号产生器,然后下面的一大坨蓝色是函数发生器,右边的绿色方框是产生最右边全加器进位的电路

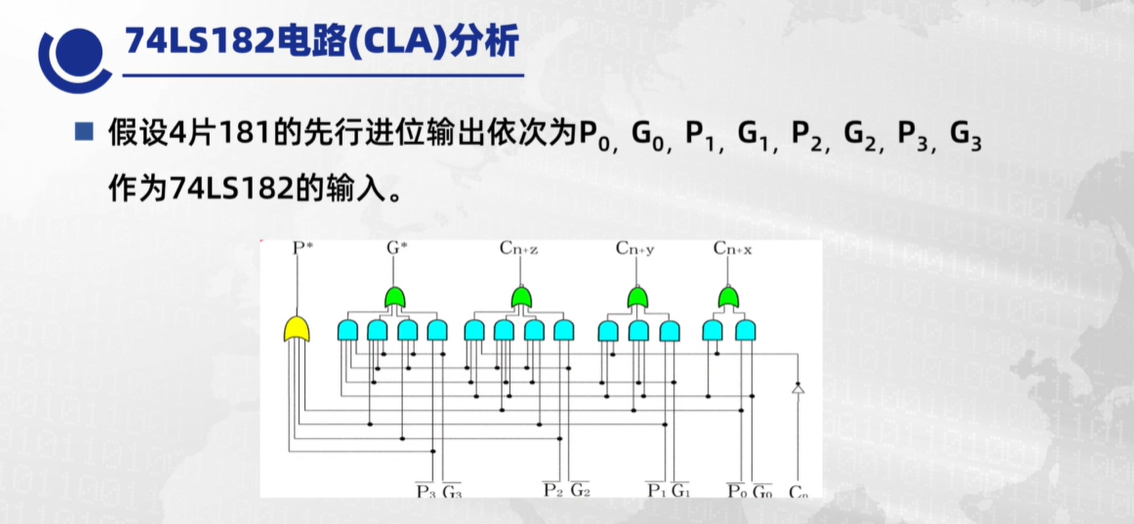

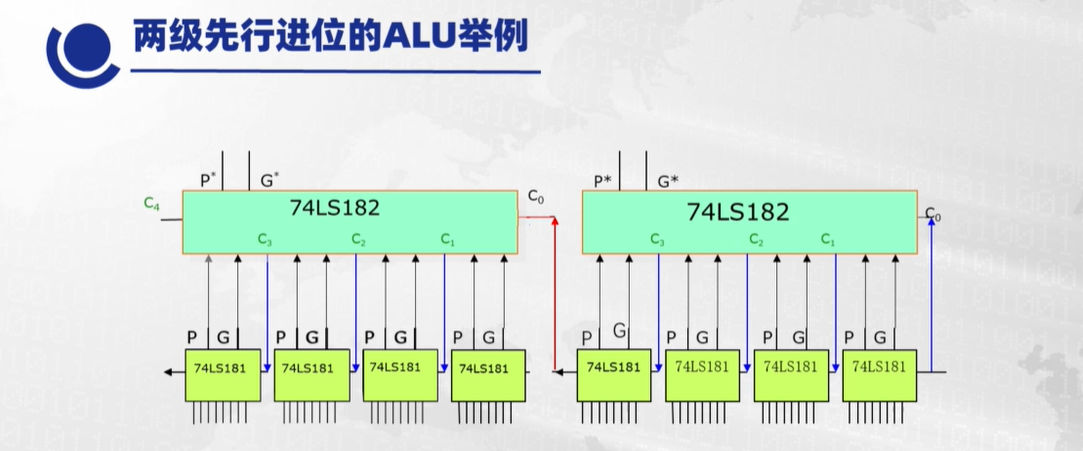

下图是74LS182的逻辑电路图,即将四片74LS181的进位信号P、G作为输入送进了74LS182的先行进位部件,实现了第二级的先行进位,最后将两片74LS182串行并联,即可以实现32位的ALU运算单元

下图是74LS182的逻辑电路图,可以发现和四位先行进位加法器大致一样

下图是两级先行进位32位ALU单元的线路图

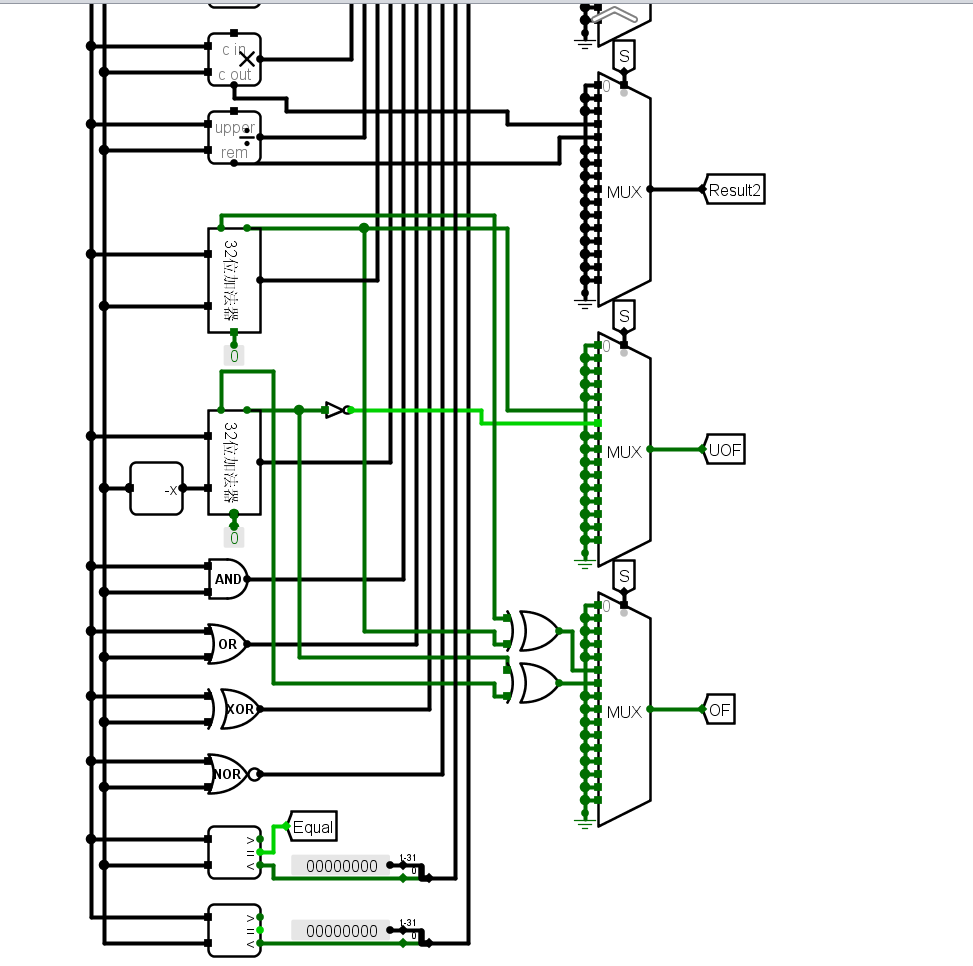

有一点点毛病的ALU运算单元

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-23X1Z6jY-1681220060939)(001_定点数的运算方法及运算器.assets/6c0f10a67f1e41cea94ddc87556a6411.png)]

定点运算器的基本结构

- 算术逻辑运算单元ALU

实现算术和逻辑的运算

- 寄存器组

暂存待加工的信息和加工后的结果

- 多路开关、锁存器、输出移位

控制数据输入和输出

- 运算器内部总线

连接各组部分,实现信息的传送

总线

总线是计算机内各部件之间传送信息的公用的一组连线

按所在位置分类,总线可以分为内部总线和外部总线。

- 内部总线是指CPU内各部件之间的连线

- 外部总线指系统总线,即CPU与存储器、I/O系统之间的连线

按逻辑结构分类,总线可以分为单向总线和双向总线:

- 单向总线是指信息只能向一个方向传送

- 双向总线是指信息可以两个方向传送既可以发送数据也可以接受数据

三态门实现双向传送功能

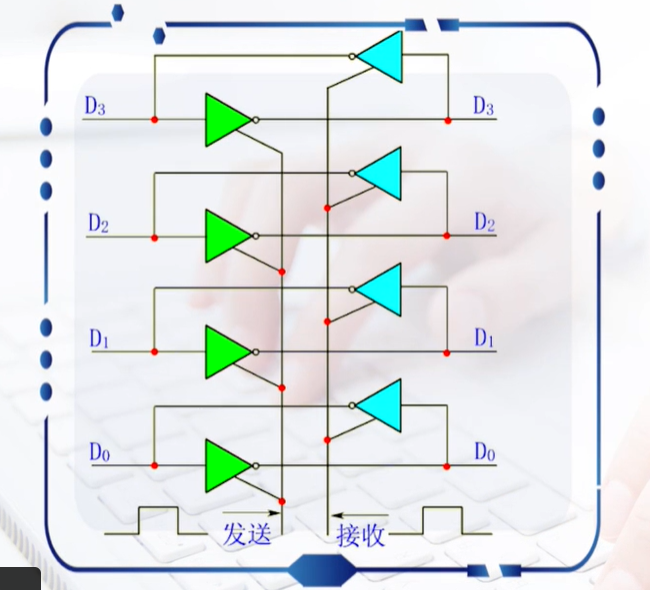

下图是一个三态门实现的双向传送功能:

假设图中的左边向右边为信号发送,右边向左边为信号接收。当左边的四个发送信号为高电平时,四个三态门处于导通状态,右边的四个接收信号为低电平,三态门处于高阻状态,为信号的发送,反之也一样。

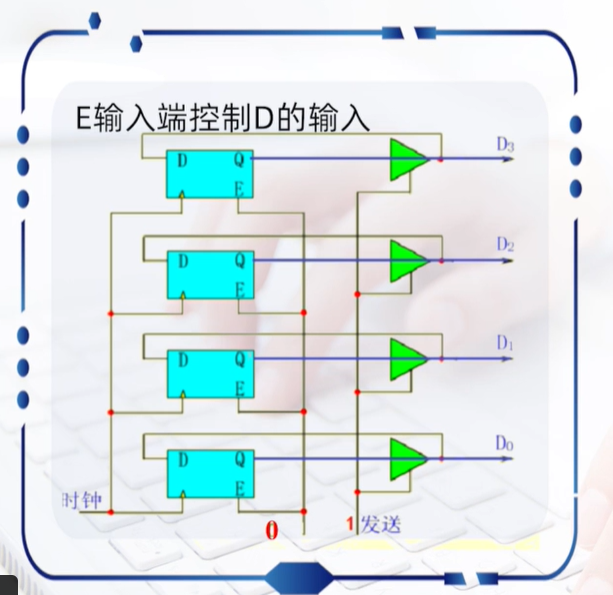

带锁存器的双向传送

我们称控制锁存器的信号为E,控制三态门的信号为P,当E=0,P=1时,三态门被打开,而锁存器保持原值不变,也就是将原来的值送给了三态门,当E=1,P=0时,三态门处于高阻状态,锁存器打开,接受了数据总线送来的值并保存。

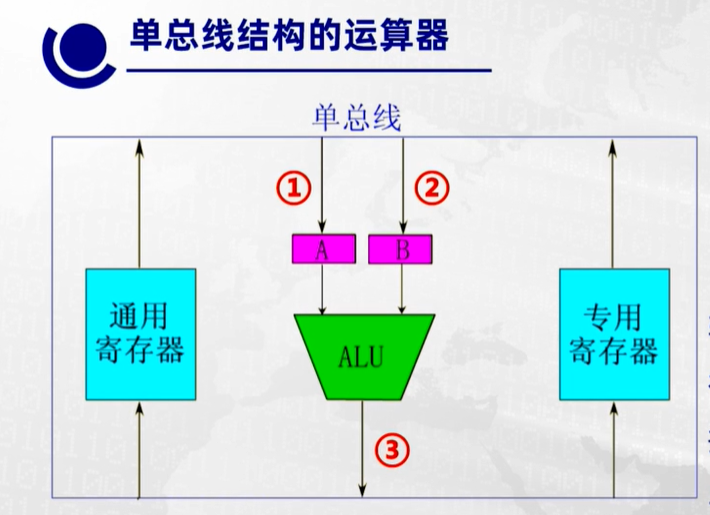

单总线结构的运算器

由于单总线数据只能够向一个方向传送,因此运算过程需要分为三个串行操作:

- 将第一个操作数送入A锁存器

- 将第二个操作数送入B锁存器

- 将结果送到目标空间

这样做的操作数都比较慢但是控制电路比较简单

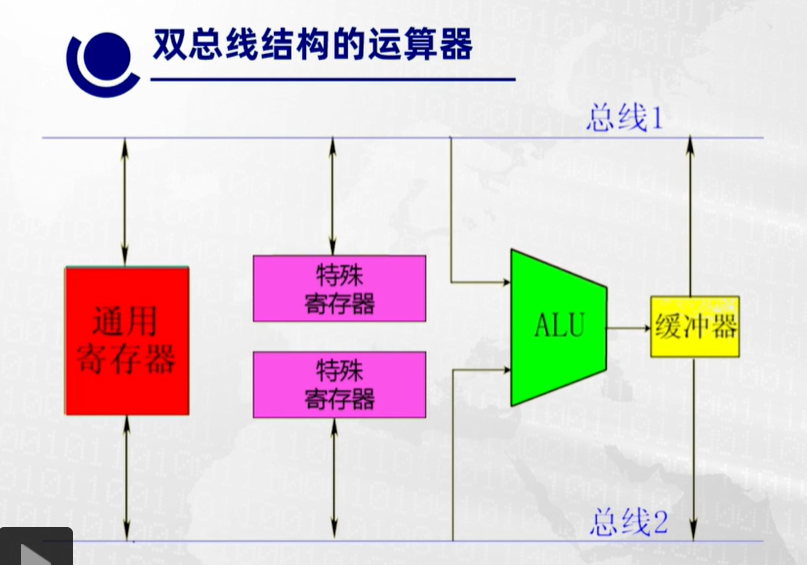

双总线结构的运算器

双总线结构的运算器只需要两步操作就可以完成运算

ALU可以同时接受总线1和总线2上的数据,立刻就算出运算结果

两个特殊寄存器可以分别与两条总线交换数据,通用寄存器可以与两条总线的任意一条交换数据

当ALU计算完成时不能够将结果直接输出到总线上,因为此时总线1和总线2都被输入数据占用,因此设置一个缓冲器暂存数据,然后再输出到任意一条总线上。

- 将两个操作数从两个总线送到ALU,结果送入缓冲器

- 将结果送到送到目的寄存器

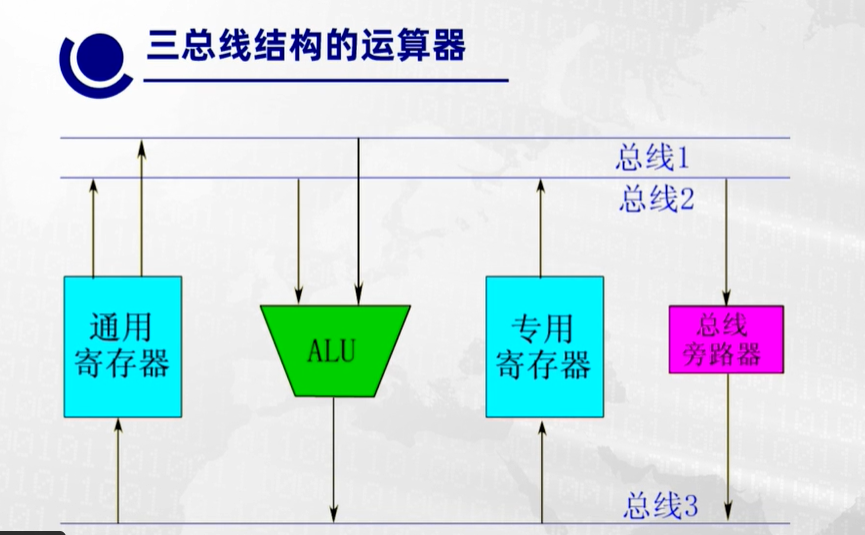

三总线结构的运算器

可以通过一步操作直接完成运算

- 将两个总线上的数据送到ALU,然后算出结果送到总线3(需要注意,两个总线上的数据送到ALU会有时间延迟,需要考虑到这一点)

总线旁路器的作用是如果一个数据不需要修改直接输出,可以经过旁路器直接输出到总线三。

运算一步完成,但是硬件结构比较复杂