题外话:本人是FPGA刚入门的新手,手头正好有块Xilinx的AC701评估板,官方例程太高端不适合入门,网上关于Artix-7的资料又太少,所以在学习的过程中把自己的心得与大家分享,希望能够一起交流。学习中借鉴了很多特权同学的教材,比如AT7套件的教程,基本上都做了移植,在这里谢谢特权同学。

---------------------------------------------------------------------------------------------------------------

本实例内容为PLL的配置和例化,通过PLL产生4个不同频率的时钟,分别驱动 4 个 LED 指示灯闪烁一样的频率。通过观察这 4 个 LED 指示灯的闪烁同步与否,可以确认 PLL 产生的这 4 个时钟的频率关系。

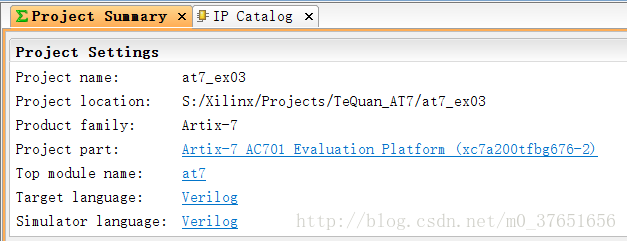

新建工程时选择AC701 Evaluation Board。

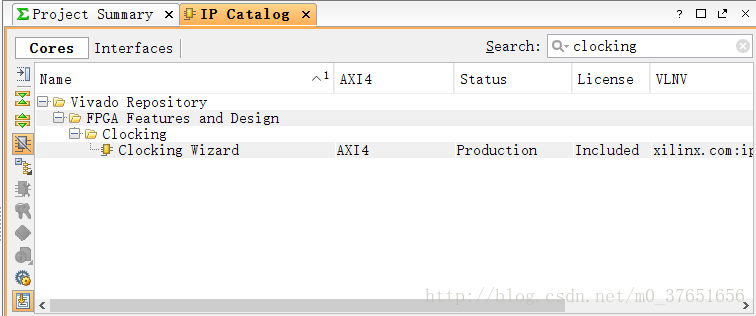

在IP Catalog中输入clocking,选择clocking wizard ip核。

首先配置Clocking Options页:

Primitive:选择为PLL

Input Clock Information:Primary Input Frequency( MHz)设置为200(本例中选择输入时钟为SYSCLK,时钟源为SiT9102 LVDS 200MHz)。Source选择Differential clock capable pin,因为输入时钟为差分时钟,当改变输入时钟类型时一定要设置相应的时钟源!

然后设置Output Clocks页:

Output Clock:勾选clk_out1、 clk_out2、clk_out3、clk_out4,Output Freq(MHz)分别设置为50、100、200、400。Enable Optional Inputs/Outputs:勾选reset、locked。

Reset Type:选择Active High。

后面几个页面根据需要进行修改。

添加顶层源码at7.v,在顶层模块中例化PLL ip和LED控制模块,代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2018/02/26 09:32:50

// Design Name: at7_ex03

// Module Name: at7

// Project Name: PLL配置实例

// Target Devices:

// Tool Versions:

// Description:

// PLL输出时钟做分频,产生LED闪烁控制信号

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module at7(

input SYSCLK_P, //SiT9102 LVDS 200MHz时钟,xdc只需要约束p端

input SYSCLK_N,

input ext_rst_p, //外部复位,高电平有效

output [3:0] led

);

wire clk_50m; //PLL输出50MHz时钟

wire clk_100m; //PLL输出100MHz时钟

wire clk_200m; //PLL输出200MHz时钟

wire clk_400m; //PLL输出400MHz时钟

wire sys_rst_n; //PLL输出的locked信号,作为FPGA内部的复位信号,低电平复位,高电平正常工作

//`define SIMULATION

`ifdef SIMULATION

`define PARAMETER_COUNTER 9

`else

`define PARAMETER_COUNTER 23

`endif

// PLL例化

clk_wiz_0 u1_clk_wiz_0(

// Clock in ports

.clk_in1_p(SYSCLK_P), // input clk_in1_p

.clk_in1_n(SYSCLK_N), // input clk_in1_n

// Clock out ports

.clk_out1(clk_50m), // output clk_out1

.clk_out2(clk_100m), // output clk_out2

.clk_out3(clk_200m), // output clk_out3

.clk_out4(clk_400m), // output clk_out4

// Status and control signals

.reset(ext_rst_p), // input reset

.locked(sys_rst_n)); // output locked

//50MHz时钟进行分频闪烁,计数器为23位

led_controller #(`PARAMETER_COUNTER) u2_led_controller_clk50m(

.clk(clk_50m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[0]) //LED指示灯接口

);

//100MHz时钟进行分频闪烁,计数器为24位

led_controller #(`PARAMETER_COUNTER+1) u3_led_controller_clk100m(

.clk(clk_100m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[1]) //LED指示灯接口

);

//200MHz时钟进行分频闪烁,计数器为25位

led_controller #(`PARAMETER_COUNTER+2) u4_led_controller_clk200m(

.clk(clk_200m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[2]) //LED指示灯接口

);

//400MHz时钟进行分频闪烁,计数器为26位

led_controller #(`PARAMETER_COUNTER+3) u5_led_controller_clk400m(

.clk(clk_400m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有效

.sled(led[3]) //LED指示灯接口

);

endmodule

led_controller.v的代码如下:

//单个LED闪烁

module led_controller(

input clk, //时钟信号

input rst_n, //复位信号,低电平有效

output sled //LED指示灯接口

);

parameter CNT_HIGH = 24; //计数器最高位

//-------------------------------------

reg[(CNT_HIGH-1):0] cnt; //24位计数器

//cnt计数器进行循环计数

always @ (posedge clk or negedge rst_n)

if(!rst_n) cnt <= 0;

else cnt <= cnt+1'b1;

assign sled = cnt[CNT_HIGH-1];

endmodule

约束文件at7.xdc代码如下:SYSCLK差分时钟只需要对P端进行约束。

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

#SYSCLK

#单端90MHz

#set_property PACKAGE_PIN P16 [get_ports FPGA_EMCCLK]

#set_property IOSTANDARD LVCMOS33 [get_ports FPGA_EMCCLK]

#差分200MHz

set_property PACKAGE_PIN R3 [get_ports SYSCLK_P]

set_property IOSTANDARD LVDS_25 [get_ports SYSCLK_P]

#set_property PACKAGE_PIN P3 [get_ports SYSCLK_N]

#set_property IOSTANDARD LVDS_25 [get_ports SYSCLK_N]

#差分156.250MHz

#set_property PACKAGE_PIN M21 [get_ports USER_CLOCK_P]

#set_property IOSTANDARD LVDS_25 [get_ports USER_CLOCK_P]

#set_property PACKAGE_PIN M22 [get_ports USER_CLOCK_N]

#set_property IOSTANDARD LVDS_25 [get_ports USER_CLOCK_N]

#CPU_RESET

set_property PACKAGE_PIN U4 [get_ports ext_rst_p]

set_property IOSTANDARD LVCMOS15 [get_ports ext_rst_p]

#GPIO_LED

set_property PACKAGE_PIN M26 [get_ports led[0]]

set_property IOSTANDARD LVCMOS33 [get_ports led[0]]

set_property PACKAGE_PIN T24 [get_ports led[1]]

set_property IOSTANDARD LVCMOS33 [get_ports led[1]]

set_property PACKAGE_PIN T25 [get_ports led[2]]

set_property IOSTANDARD LVCMOS33 [get_ports led[2]]

set_property PACKAGE_PIN R26 [get_ports led[3]]

set_property IOSTANDARD LVCMOS33 [get_ports led[3]]

#GPIO_BUTTON

#set_property PACKAGE_PIN P6 [get_ports sw[0]]

#set_property IOSTANDARD LVCMOS15 [get_ports sw[0]]

#set_property PACKAGE_PIN T5 [get_ports sw[1]]

#set_property IOSTANDARD SSTL15 [get_ports sw[1]]

#set_property PACKAGE_PIN R5 [get_ports sw[2]]

#set_property IOSTANDARD SSTL15 [get_ports sw[2]]

#set_property PACKAGE_PIN U5 [get_ports sw[3]]

#set_property IOSTANDARD SSTL15 [get_ports sw[3]]

#set_property PACKAGE_PIN U6 [get_ports GPIO_SW_C]

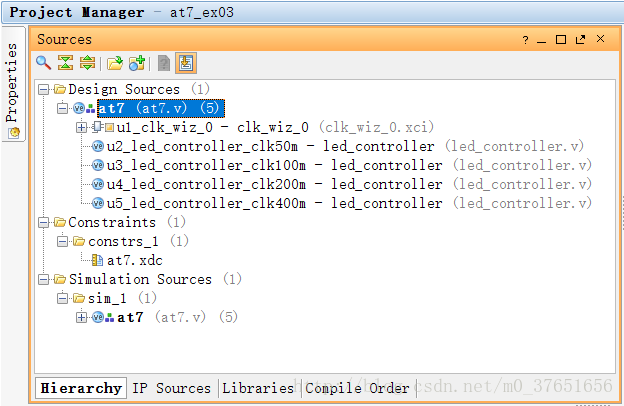

#set_property IOSTANDARD SSTL15 [get_ports GPIO_SW_C] 最终的工程目录如下图所示:

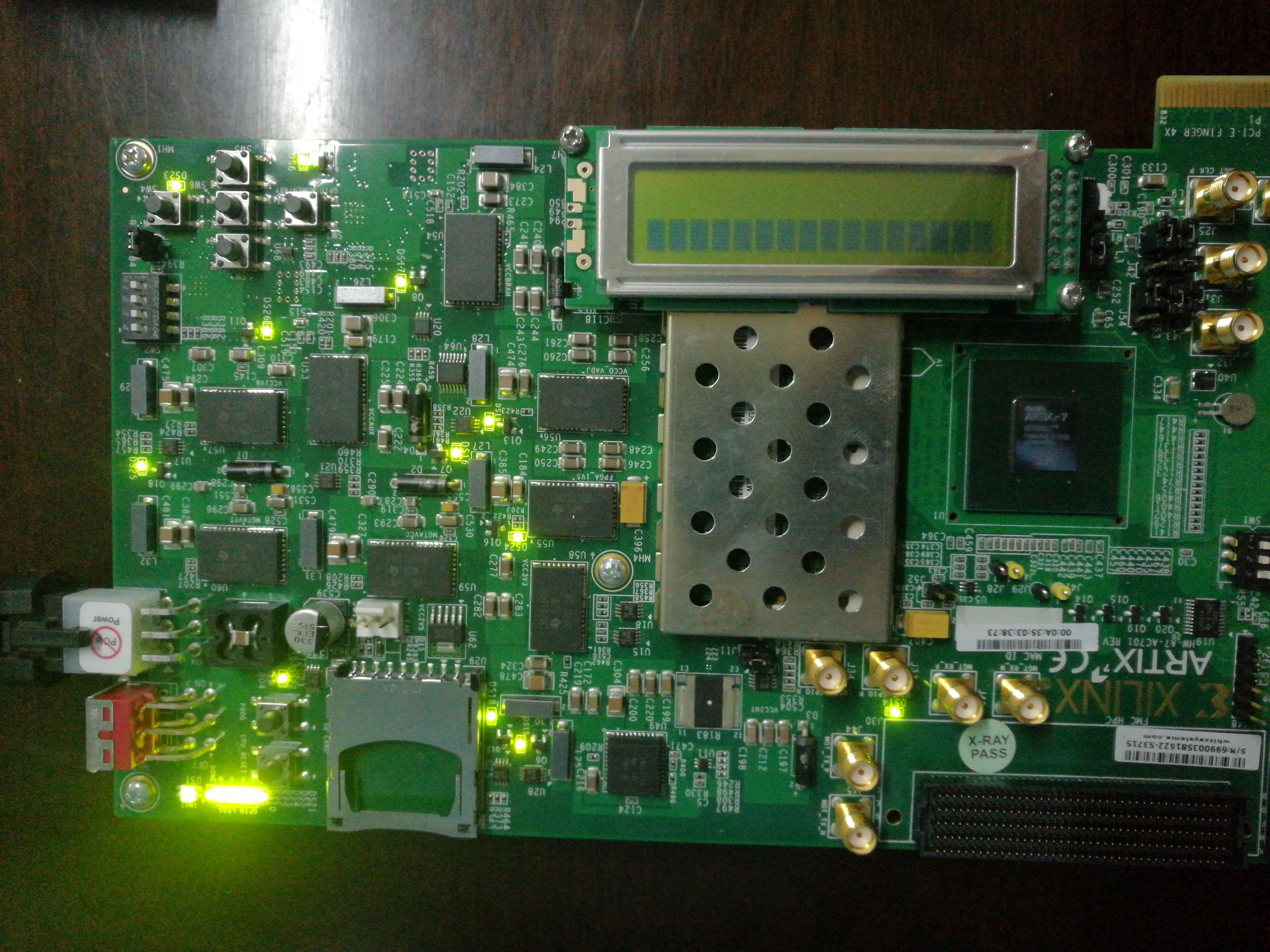

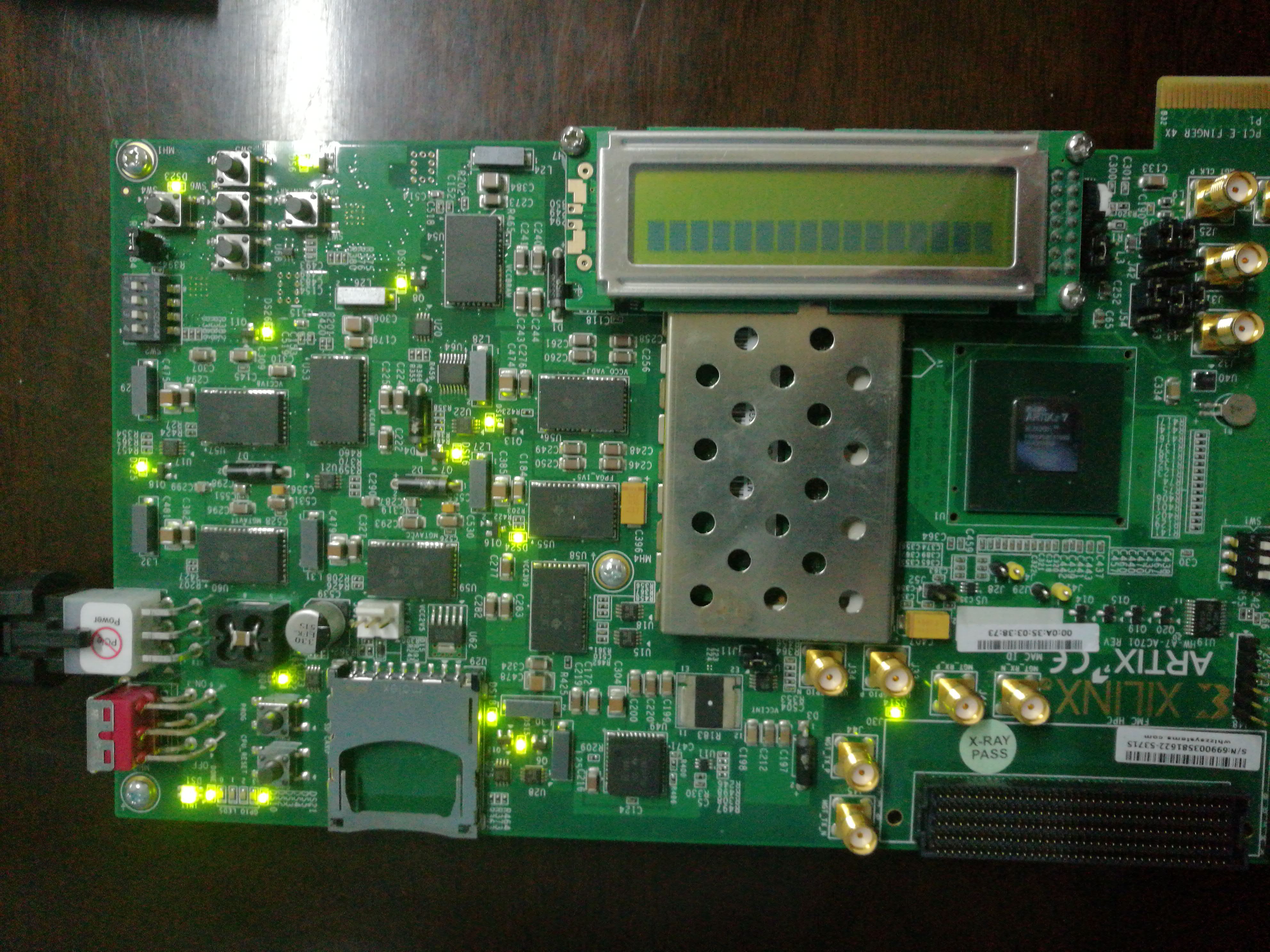

生成bit文件后烧录到评估板,效果如下图,四个LED(左下角)闪烁频率相同,证明PLL按配置要求产生了四个不同频率的时钟。

版权声明:本文为m0_37651656原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。