1、什么是总线?

答:总线是运算部件之间数据流通的公共通道。

2、总线的作用?

答:提高专用信号处理逻辑电路的运算能力和速度。

3、总线与部件之间是怎么连接的?

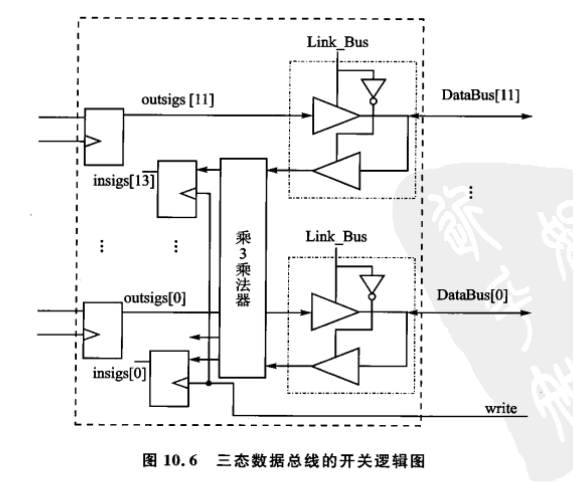

答:各运算部件和数据寄存器组是通过带控制端的三态门与总线相连接的。通过控制端口电平的高低来确定某一时刻是哪一个部件使用总线。

控制信号的相互配合需要由同步状态机控制开关阵列控制,将在后面讲解如何设计复杂的同步状态机。

4、实例:三态数据总线的开关逻辑图?

**********************************************************

5、verilog程序实现:

module SampleOfBus(DataBus,link_bus,write);

inout[11:0] DateBus; //12位总线双向端口

input link_bus; //向总线输出数据的控制电平

reg[11:0] outsigs; //模块内12位宽的数据寄存器

reg[13:0] insigs; //模块内14为快的数据寄存器

assign DataBus = (link_bus)? outsigs:12'hzzz;

always@(posedge write)

begin

insigs <= DataBus*3;

end

endmodule

*********************************************************

made by qidaiYMM, your comment is appreciated.

email:1519882610@qq.com

转载于:https://www.cnblogs.com/qidaiymm/p/4887678.html