定长指令周期—时序发生器输出函数设计

实验目的

帮助学生理解传统三级时序系统中时序发生器的基本原理,学生能设计定长指令周期的时序发生器状态机以及输出函数。

实验内容

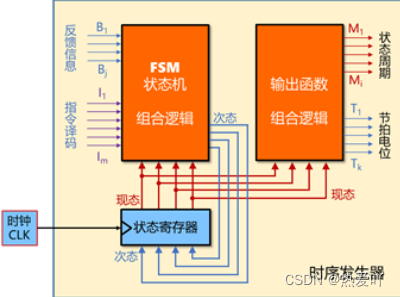

利用数字逻辑电路相关知识设计定长指令周期的三级时序系统,时序发生器包括状态机和输出函数两部分,上一关已经实现了FSM状态机逻辑,本实验要求设计实现输出函数组合逻辑。

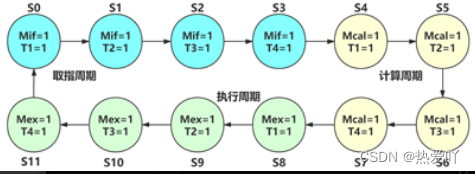

单总线结构中如果采用定长指令周期,所有MIPS指令都需要3个机器周期,每个机器周期4个时钟节拍,一共需要12个状态,状态图如下:

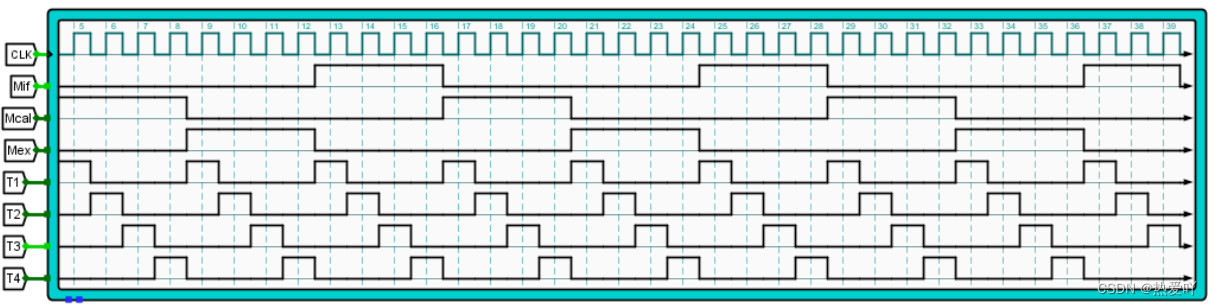

输出函数为组合逻辑,输入为状态寄存器的现态输出,输出为状态周期电位和节拍电位信号,定长指令周期的状态周期电位和节拍电位信号时序如下:

根据时序输出要求,填写excel表,自动生成各输出信号的逻辑表达式,在logisim中自动生成电路即可。

版权声明:本文为weixin_44176581原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。