目录

加法器是算术运算的一种,在计算机和一些处理器中被运用于算术逻辑单元ALU中或者处理器的其他部分如计算地址,加减操作等类似操作。今天。我们来重温下数字电路中的加法器。

一、半加器

半加器用于计算2个单比特二进制数a与b的和,输出结果sum(s)和进位carry(c)。在多比特数的计算中,进位c将作为下一相邻比特的加法运算中。单个半加器的计算结果是2c+s。其真值表、逻辑表达式、verilog描述和电路图分别如下所示。

真值表

输入 | 输出 | ||

a | b | s | c |

0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 0 | 1 |

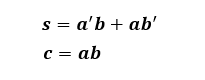

逻辑表达式

Verilog描述

module half_adder(

input a,

input b,

output c,

output s

);

assign c = a & b;

assign s = a ^ b;

endmodule电路图

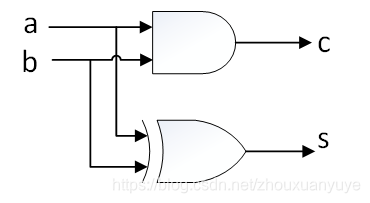

二、全加器

全加器不同于半加器的地方是,全加器带有进位cin。输入为a,b,cin, 输出为sum(s)和carry*(cout),均是单比特信号。s为a,b,cin三个单比特数的和,cout为a,b,cin三个数超过2后的进位。真值表、逻辑表达式、verilog描述和电路图分别如下所示。

真值表

输入 | 输出 | |||

a | b | cin | s | cout |

0 | 0 | 0 | 0 | 0 |

0 | 1 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 0 |

1 | 1 | 0 | 0 | 1 |

0 | 0 | 1 | 1 | 0 |

0 | 1 | 1 | 0 | 1 |

1 | 0 | 1 | 0 | 1 |

1 | 1 | 1 | 1 | 1 |

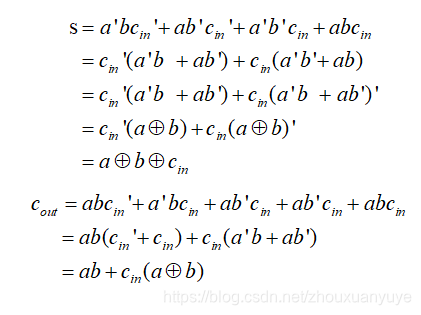

逻辑表达式

Verilog描述

module full_adder(

input a,

input b,

input cin,

output cout,

output s

);

assign s = a ^ b ^ cin;

assign cout = a & b | (cin & (a ^ b));

endmodule电路图

表示符号

三、行波进位加法器

N-bit加法器可以根据1-bit全加器组合而成。每个全加器的输出进位cout作为下一个全加器的输入进位cin,这种加法器称为行波进位加法器(Ripple-carry adder,简称RCA),如一个16比特加法器的结构如下图所示,其中A,B为16比特的加数,S为A+B的和,c16为该加法器的输出:

由上图可以看出得到进位c16的结果依赖于c15,c14,c13,…,c2,c1,c0,对于32-bit,64-bit,128-bit等加法器,进位链将显得更加长。所以,行波进位加法器设计简单,只需要级联全加器即可,但它的缺点在于超长的进位链,限制了加法器的性能。

Verilog描述

module rca #(width=16) (

input [width-1:0] op1,

input [width-1:0] op2,

output [width-1:0] sum,

output cout

);

wire [width:0] temp;

assign temp[0] = 0;

genvar i;

for( i=0; i<width; i=i+1) begin

full_adder u_full_adder(

.a ( op1[i] ),

.b ( op2[i] ),

.cin ( temp[i] ),

.cout ( temp[i+1] ),

.s ( sum[i] )

);

end

endmodule半加器,全加器和行波进位加法器,源码公众号回复002。

更多阅读,关注“纸上谈芯”,不定期更新,共同学习: