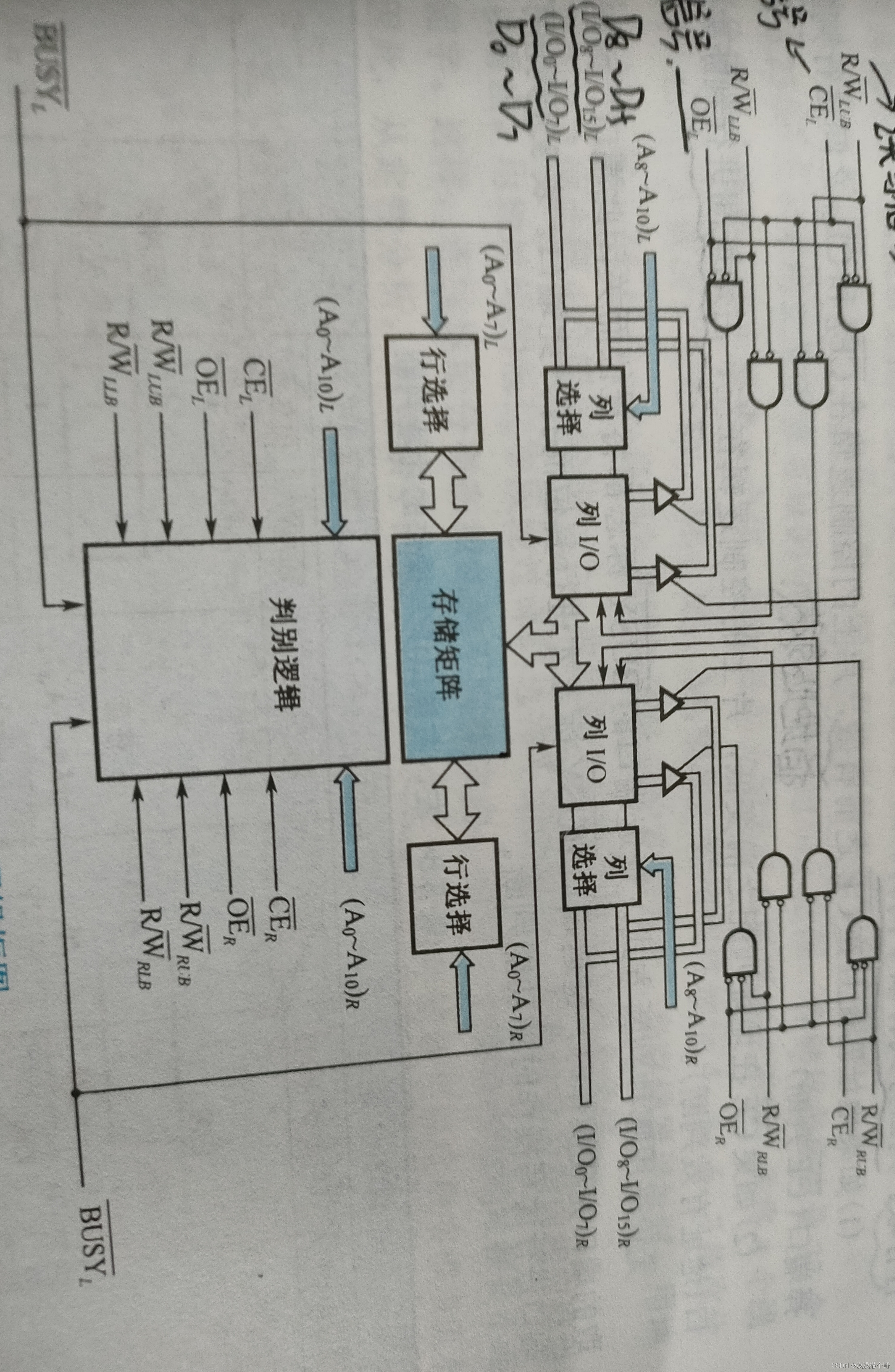

1.双端口存储器的逻辑结构

双端口存储器是同一个存储器具有两组相互独立的读写控制电路。(双端口存储器也可以由DRAM构成)

2.无冲突读写控制

当两个端口的地址不同时在两个端口上进行读写操作,一定不会发生冲突。当任意端口被选中驱动时,就可对整个存储器进行存取,每一个端口都有自己的片选控制和输出驱动控制。

图中字母符号下标中L表示左端口,R表示右端口,LB表示低位字节,UB表示高位字节。表中符号1代表高电平,0表示低电平,X为任意,Z为高阻态。

3.有冲突的读写控制

当两个端口同时存取存储器同意存储单元,而且至少有一个端口为写操作时,便发生读写冲突。

仲裁逻辑可以根据两个端口的地址匹配或片选使能信号有效的时间决定对哪个端口进行存取,判断方式有两种。

(1)如果地址匹配且在CE非之前有效,片上的控制逻辑在CEL非和CER非之间进行判断来选择端口。

(2)如果CE非在地址匹配之前变低,片上的控制逻辑在左右地址间进行判断来选择端口。

版权声明:本文为m0_73648269原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。