本篇文章为本人学习Xilinx的Vivado HLS教程记录的学习笔记,仅供学习参考。

Vivado HLS官方视频教程:

优酷视频v.youku.com目录:

- Vivado HLS课程简介

- FPGA与CPU、GPU、DSP的区别

- FPGA的优势

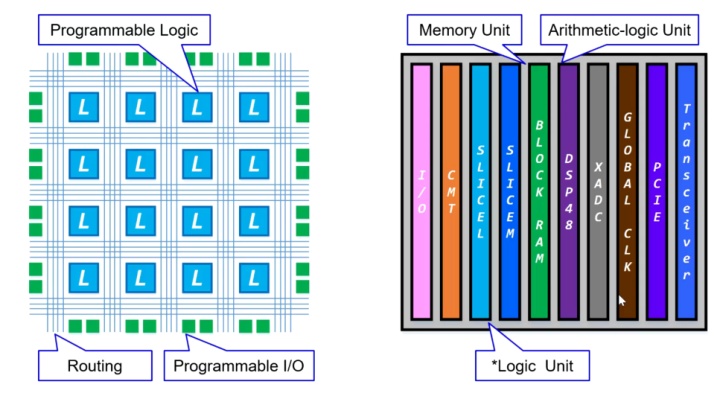

- Xilinx FPGA架构:逻辑单元、算术逻辑单元、存储单元

- 使用C/C++ 来开发FPGA时需要关注的方面

1.Orientation and Overview of this Course(课程简介):

设计流程、代码风格、for循环和数组的优化方法、输入输出端口的实现方式

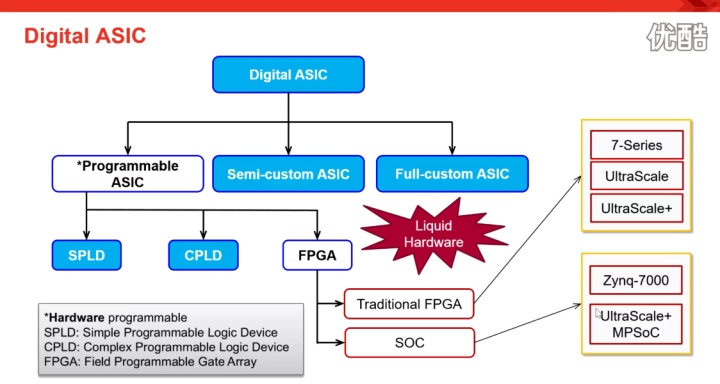

2.FPGA架构(软件工程师的角度):

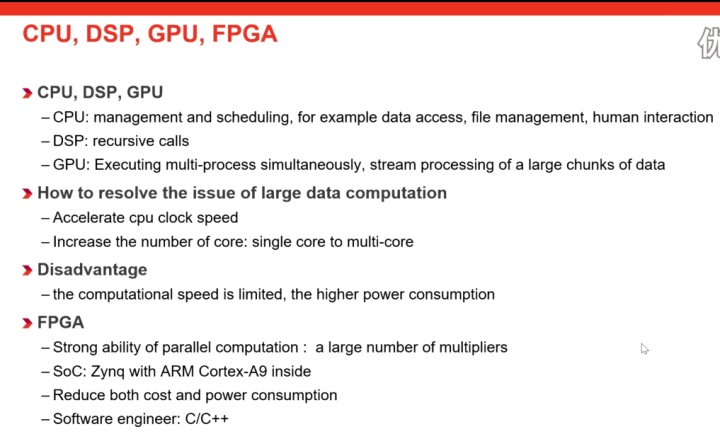

2.1 FPGA与CPU、GPU、DSP的区别

- FPGA是硬件可编程,其他芯片为软件可编程。

- FPGA具有丰富的硬件计算单元(大量乘法器)以及分布式并行内存,其他芯片只有非常有限的计算资源,比如CPU只有几个高性能ALU,另外其他芯片一般使用一个共享内存,在任何是有只能进行一次的读或者写操作。

- FPGA灵活的硬件资源导致所使用的HDL语言抽象级别非常低,为RTL级,而其他芯片的编程语言都是在算法级或者系统级。

- CPU适用于调度和管理的场景,比如文件管理,人机交互。

- DSP适合数据处理,尤其是递归调用

- GPU适合大容量数据流处理

来自 <https://blog.csdn.net/wangwenqing2018/article/details/77824785>

2.2 FPGA的优势

2.3 Xilinx FPGA架构(软件工程师角度)

逻辑单元、存储单元、算术逻辑单元

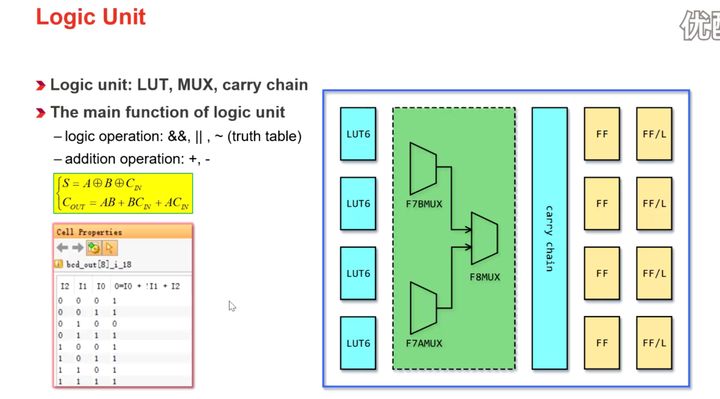

(1)逻辑单元:LUT查找表、MUX数据选择器、carry chain进位链

- LUT实现逻辑函数发生器:通过真值表的方式实现

- 加法运算也属于逻辑运算(异或、与等):可用LUT或DSP48实现

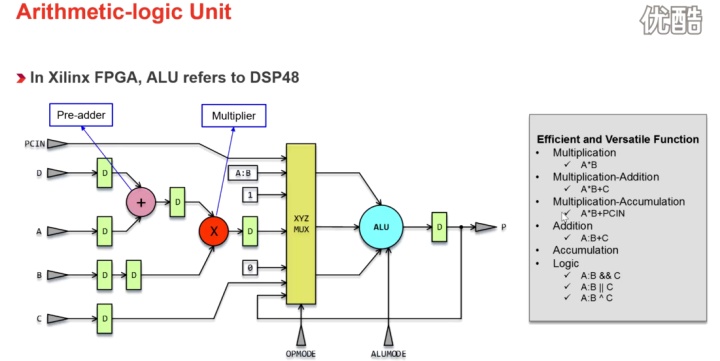

(2)ALU算术逻辑单元:DSP48

可实现加法、乘法、累加等,可应用于数字滤波、FFT等

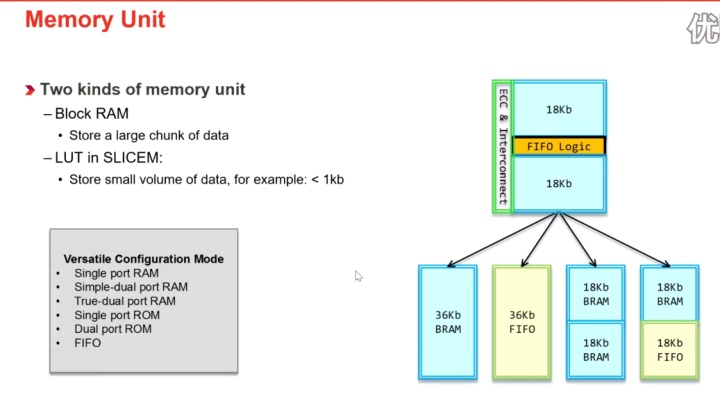

(3)存储单元:

- Block RAM(块随机存储器、2个18Kb的内存组成)

- 分布式RAM(LUT in SLICEM)

- 可多功能配置模式:单端/双端、ROM/RAM、FIFO

- C/C+数组会映射到RAM

软件工程师关注:功能、操作与单元的对应关系、算法模型的资源利用率(综合报告有)、优化方法

3.使用C/C++ 来开发FPGA时需要关注的方面:

- 算法的不同部分的功能

- FPGA底层单元的操作

- 算法不同部分同FPGA底层单元的映射关系

- 算法的FGPA资源使用率

版权声明:本文为weixin_35591736原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。