摘要

本文延续上期文章对cameralink发送模块的设计探索。上期文章,用一般意义上的方法实现了速率为40Mhz/280Mhz 的图像数据传输,效果良好,这种方法由于将cameralink时钟信号一并以串行方式生成,可称之为“源同步”方式。然而这种方式下,对PCB的物理等长布线要求高,一旦改变硬件连接,可能造成部分数据失真。本文,将探究非源同步方式下的cameralink发送过程中时钟和数据的处理。这种情况下,采用时钟相位动态调整的方式,使得设计更具有灵活性。

1. 非源同步和源同步的区别

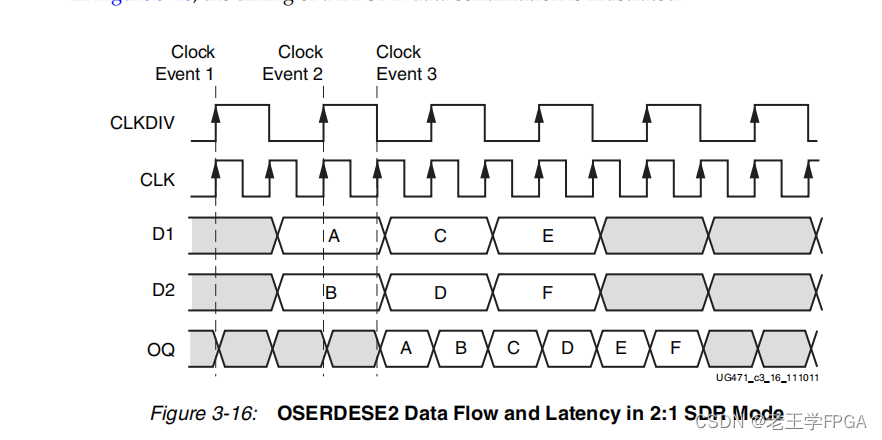

这里源同步是指数据和时钟边沿对齐同步发出,在没有外在物理延迟的情况下可以认为数据和时钟信号是同步对齐的。如下图所示,我们使用xilinx的OSERDES资源时,由于延迟的存在,其输出的串行数据和时钟边沿不是对齐的(延迟时间见下表)。

版权声明:本文为weixin_41895751原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。