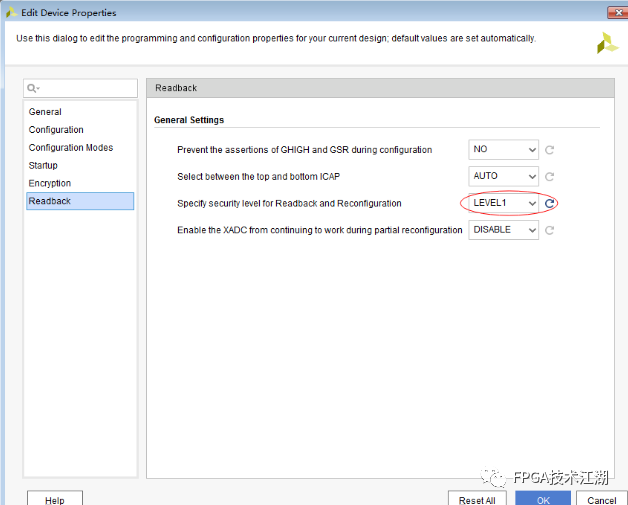

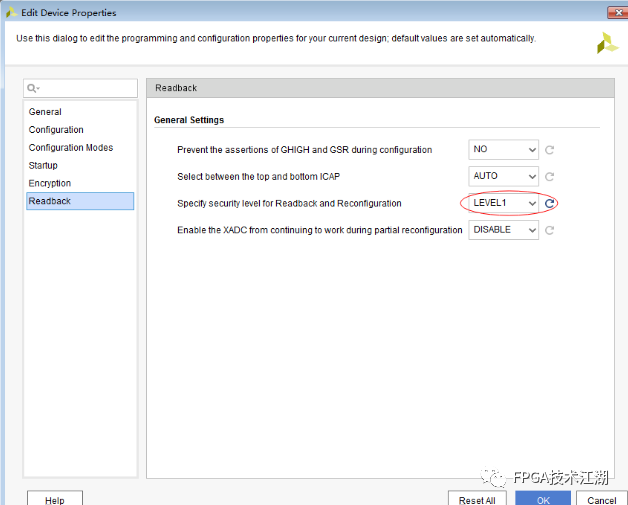

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。今天给大侠带来Xilinx FPGA bit 文件加密设计,话不多说,上货。当你的项目终于做完了,到了发布的关键节点,为了防止自己的心血被别人利用,最好对产品进行bit加密。首先咱们来了解一下加密的优点,xilinx的V6和7全系列FPGA支持AES256加密,加密的好处:1. 可以防止别人回读或者对你的程序进行逆向;2. 防止更改烧写的bit文件。如果仅仅是防止回读,可以简单设置BITSTREAM.READBACK.SECURITY,其中LEVEL1是禁止回读,LEVEL2禁止回读和重新烧写FPGA。但如果对手的逆向能力很强,比如说在FPGA上电加载bit的时候用逻辑分析仪把用bit文件“读”出来,这个简单的设置肯定就不行了。这时候可以使用AES256加密。AES算法简介:AES即高级加密标准,是一种区块加密,当然也是对称加密。区块固定为128bit,密钥为128,192或256bit。AES有5种加密模式,xliinx采用的是CBC模式。有一个128bit初始向量IV(startCBC),先利用初始向量IV与第一组数据进行异或后再进行加密运算生成C1。将C1作为初始向量与第二组数据进行异或后再进行加密运算生成C2。以此类推,当最后一组数据加密完毕后,将加密结果拼接为最终结果,C = C1C2C3……Cn。所以采用CBC模式的256AES需要两个东西,128bit-startCBC和256bit-AES key。到这里还没完,完成了bit加密还没有认证,万一别人把烧进去bit文件篡改了怎么办?(重新烧了新的bit文件)。所以xilinx又提供了HMAC的认证,这个就跟校验差不多了,检查消息的完整性。所以还需要提供256bit-HMAC,加上128bit-startCBC和256bit-AES key,一共是三个。这三个key可以自己生成,也可以指定空的 .nky文件,由软件随机生成好。 for example···

Device xc7a35t;

Key 0 0f2ec1178ae0d04c8c1431afe8266d08e799b01c5c486c2567f3621f47319aaf;

Key StartCBC a6262d508c338eeab815340a7832436d;

Key HMAC d82e72733a7bd7904c802d13db37187b8ad20b972ac163470c5a4d239bce6308;

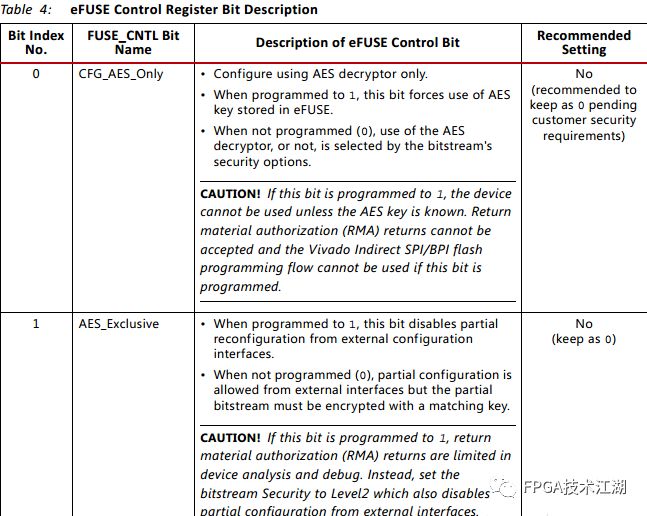

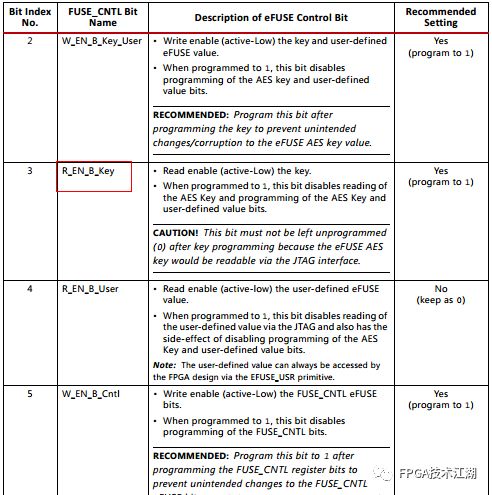

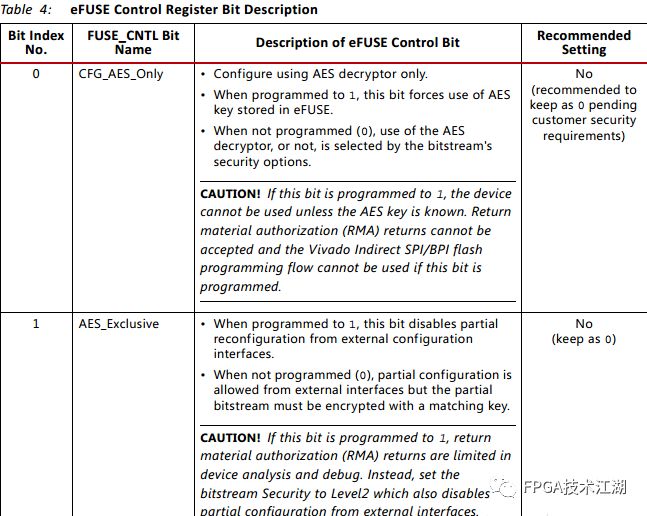

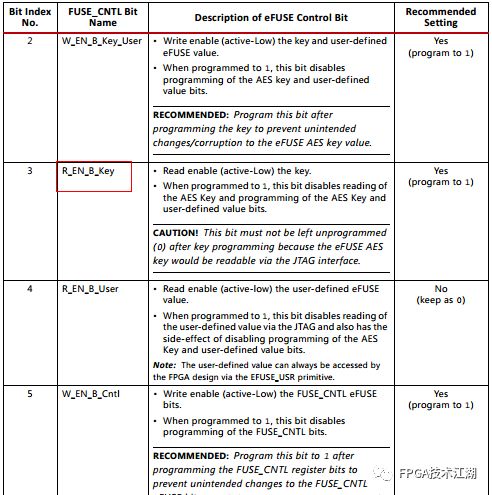

··· 加密的AES key可以存到FPGA内部易失性的BBR或只能烧写一次(OTP)的eFUSE中。BBR需要电池供电,可以多次编程。eFUSE不需要电池,但只能烧写一次。这里使用eFUSE。eFUSE寄存器 首先来看一下eFUSE寄存器: 一共有四个寄存器,分别是存放AES秘钥,用户信息,设备DNA和eFUSE控制。下面特别关注一下eFUSE控制寄存器:

一共有四个寄存器,分别是存放AES秘钥,用户信息,设备DNA和eFUSE控制。下面特别关注一下eFUSE控制寄存器:

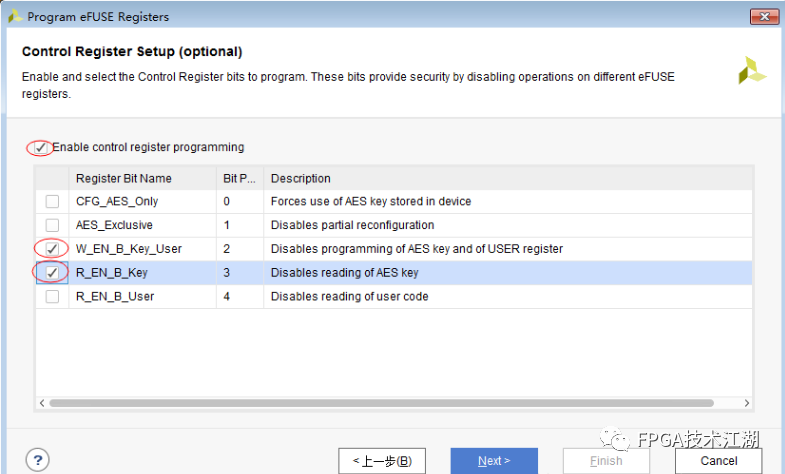

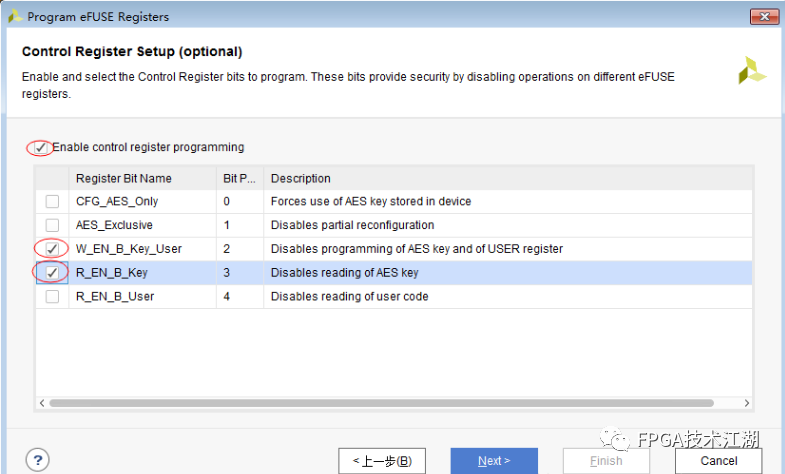

一共有6个bit有用,各种设置的优缺点表里有详细说明,使用参考设置101100就行了。其中bit0很重要,万一置位了,AES的key又搞丢了,FPGA就变砖头了。具体的操作步骤如下:1、生成key和加密bit下面三个key可以自己生成填进去,也可以由软件随机生成。

一共有6个bit有用,各种设置的优缺点表里有详细说明,使用参考设置101100就行了。其中bit0很重要,万一置位了,AES的key又搞丢了,FPGA就变砖头了。具体的操作步骤如下:1、生成key和加密bit下面三个key可以自己生成填进去,也可以由软件随机生成。

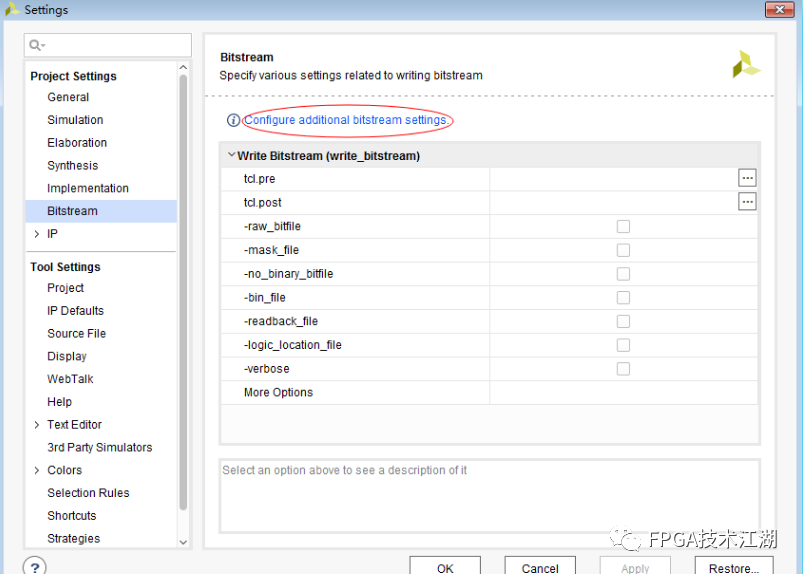

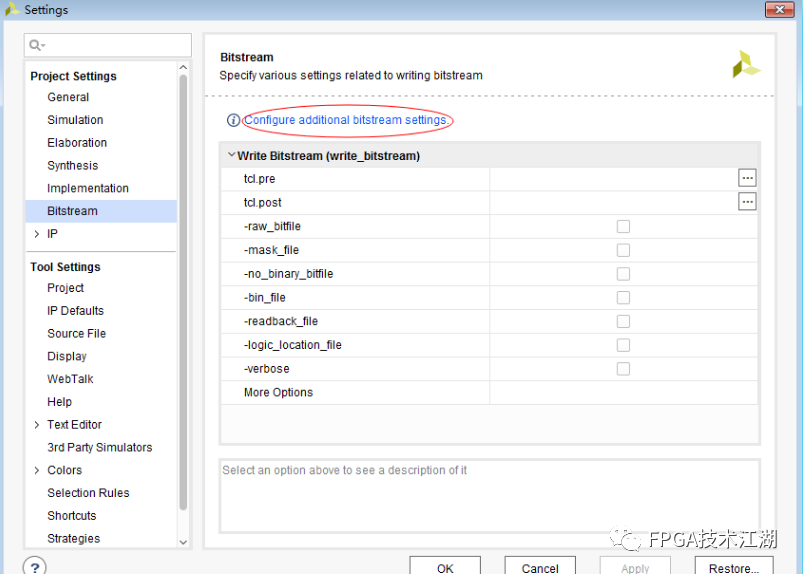

要打开edit device properties,先要打开sythesized design 或者implement design,然后在generate bitstream右键设置。

要打开edit device properties,先要打开sythesized design 或者implement design,然后在generate bitstream右键设置。

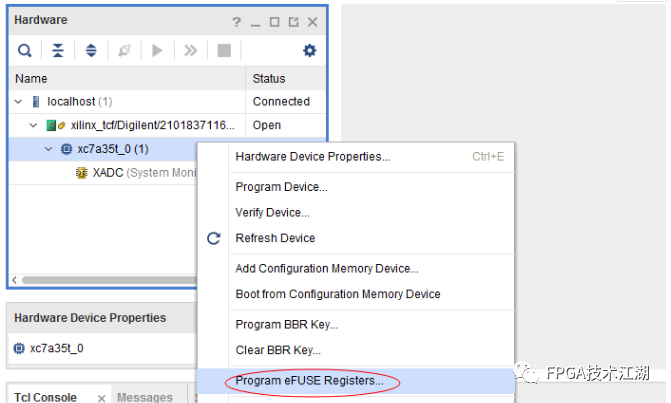

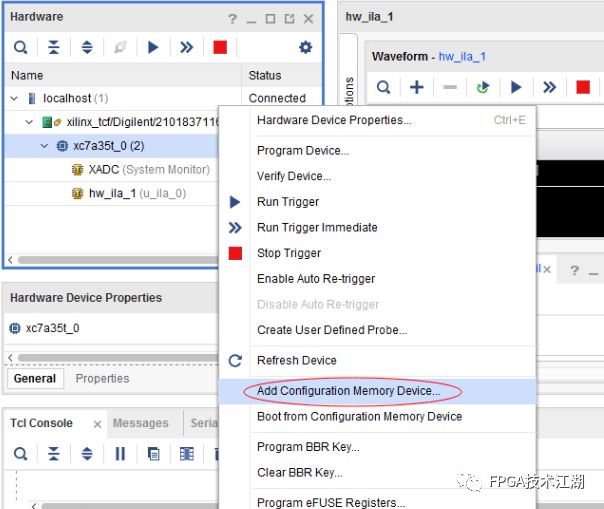

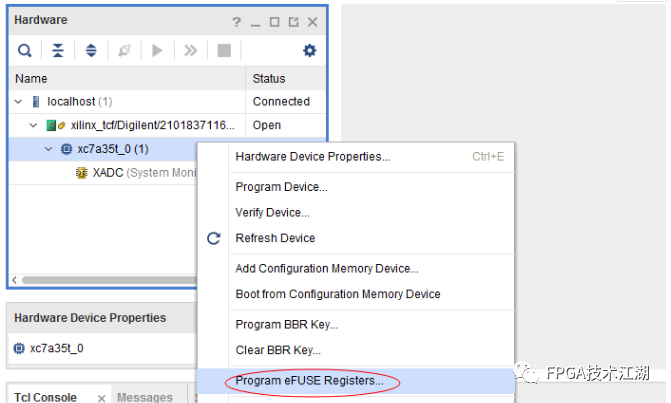

2、下载eFUSE

2、下载eFUSE

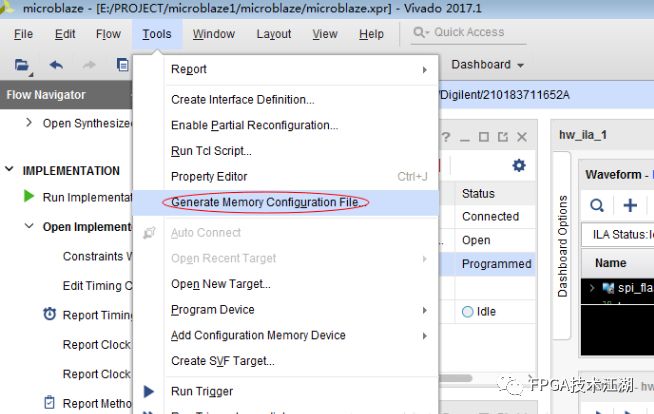

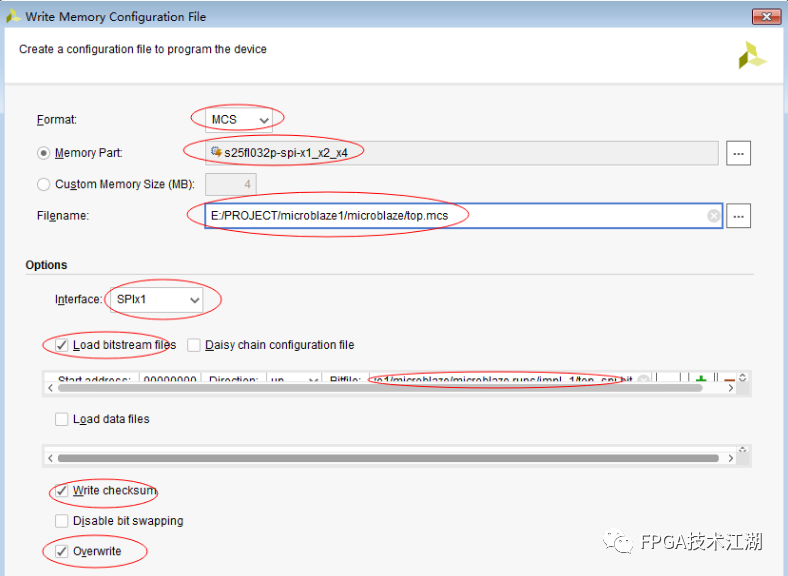

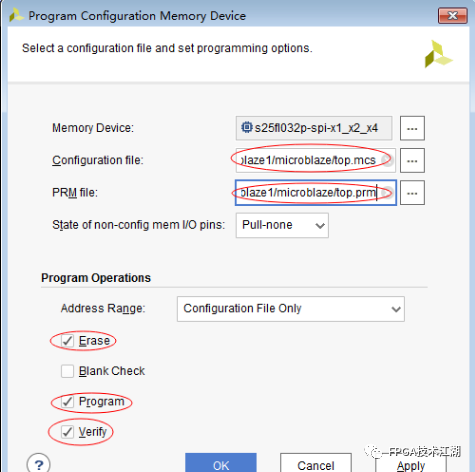

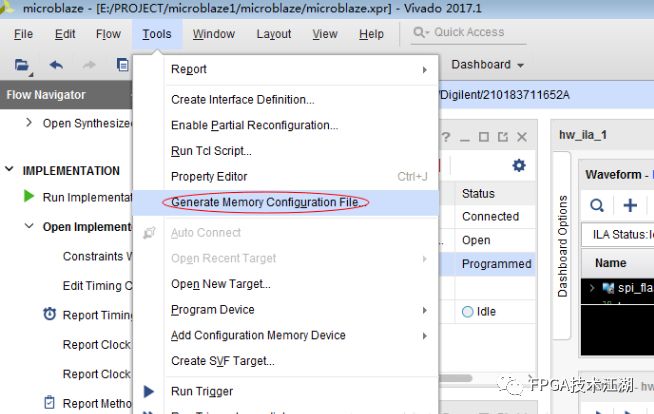

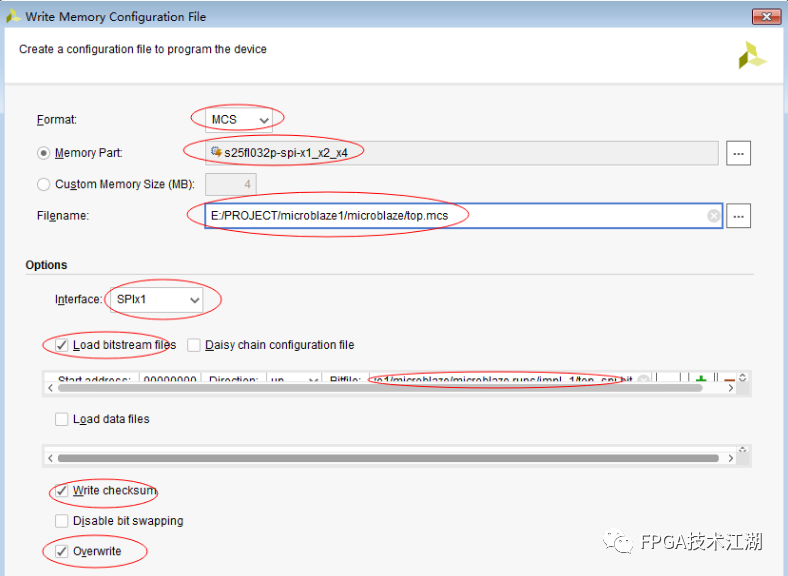

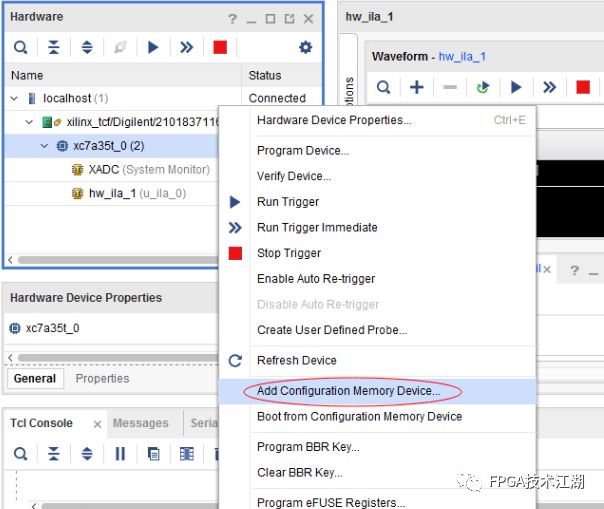

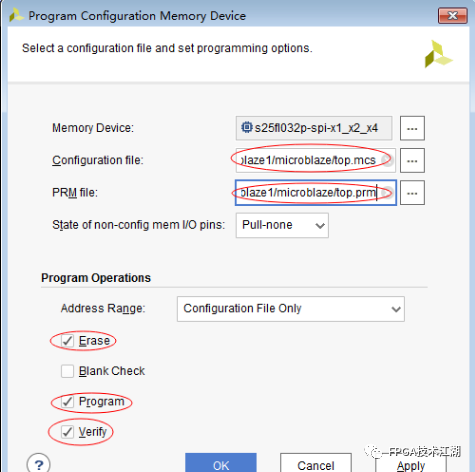

3、烧写FPGA程序

3、烧写FPGA程序

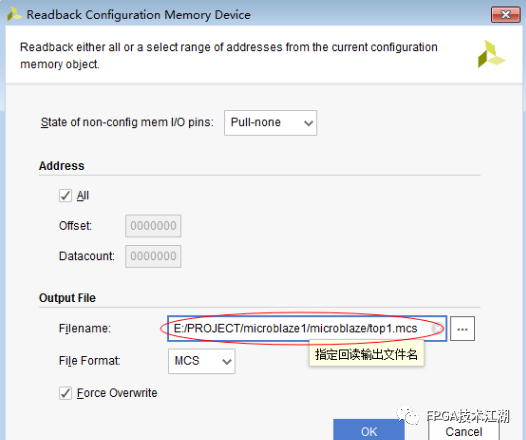

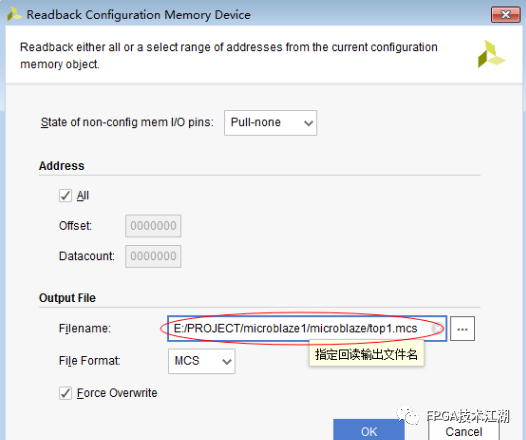

4、验证,读出mcs然后烧到另一个FPGA里面去,可以看到不能工作。当然,也可以在前面eFUSE设置时选择只能加载AES加密的bit文件,这样换一个不加密的bit下进去也能验证。

4、验证,读出mcs然后烧到另一个FPGA里面去,可以看到不能工作。当然,也可以在前面eFUSE设置时选择只能加载AES加密的bit文件,这样换一个不加密的bit下进去也能验证。

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

Device xc7a35t;

Key 0 0f2ec1178ae0d04c8c1431afe8266d08e799b01c5c486c2567f3621f47319aaf;

Key StartCBC a6262d508c338eeab815340a7832436d;

Key HMAC d82e72733a7bd7904c802d13db37187b8ad20b972ac163470c5a4d239bce6308;

··· 加密的AES key可以存到FPGA内部易失性的BBR或只能烧写一次(OTP)的eFUSE中。BBR需要电池供电,可以多次编程。eFUSE不需要电池,但只能烧写一次。这里使用eFUSE。eFUSE寄存器 首先来看一下eFUSE寄存器:

一共有四个寄存器,分别是存放AES秘钥,用户信息,设备DNA和eFUSE控制。下面特别关注一下eFUSE控制寄存器:

一共有四个寄存器,分别是存放AES秘钥,用户信息,设备DNA和eFUSE控制。下面特别关注一下eFUSE控制寄存器:

一共有6个bit有用,各种设置的优缺点表里有详细说明,使用参考设置101100就行了。其中bit0很重要,万一置位了,AES的key又搞丢了,FPGA就变砖头了。具体的操作步骤如下:1、生成key和加密bit下面三个key可以自己生成填进去,也可以由软件随机生成。

一共有6个bit有用,各种设置的优缺点表里有详细说明,使用参考设置101100就行了。其中bit0很重要,万一置位了,AES的key又搞丢了,FPGA就变砖头了。具体的操作步骤如下:1、生成key和加密bit下面三个key可以自己生成填进去,也可以由软件随机生成。

要打开edit device properties,先要打开sythesized design 或者implement design,然后在generate bitstream右键设置。

要打开edit device properties,先要打开sythesized design 或者implement design,然后在generate bitstream右键设置。

2、下载eFUSE

2、下载eFUSE

3、烧写FPGA程序

3、烧写FPGA程序

4、验证,读出mcs然后烧到另一个FPGA里面去,可以看到不能工作。当然,也可以在前面eFUSE设置时选择只能加载AES加密的bit文件,这样换一个不加密的bit下进去也能验证。

4、验证,读出mcs然后烧到另一个FPGA里面去,可以看到不能工作。当然,也可以在前面eFUSE设置时选择只能加载AES加密的bit文件,这样换一个不加密的bit下进去也能验证。

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!版权声明:本文为weixin_34007013原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。