一.实验内容

1.用两片74138译码器拼接成4-16译码器

2.验证仿真电路的正确性

3.注意观察输出信号的毛刺

二.实验步骤

本次实验采用Quartus软件进行,具体过程如下:

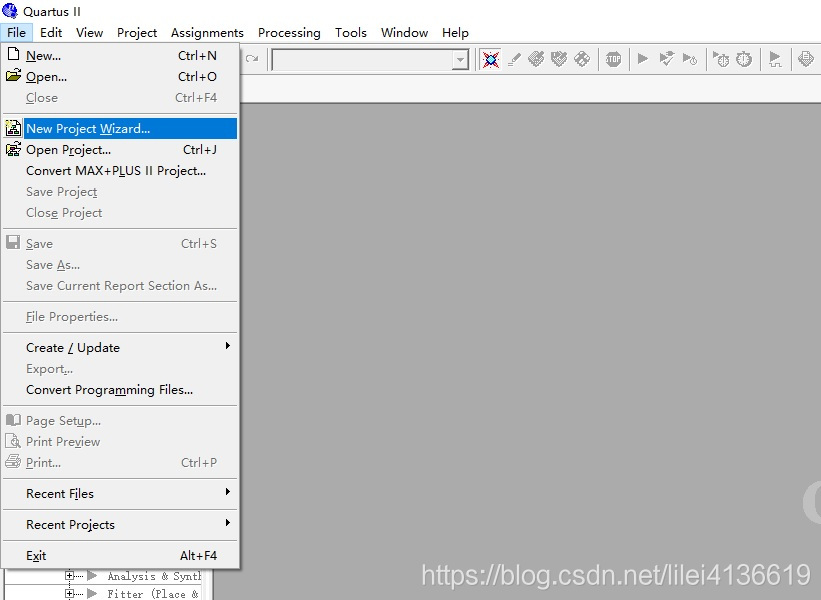

1. 创建新项目

新项目的创建:

点击菜单中的New Project Wizard开始创建新项目。

设定项目存放路径及命名项目文件(项目存放路径尽量避免出现中文):

为项目添加可能需要的文件(此项可略过):

为项目选择合适的硬件设备:

检查项目各项参数设定无误后点击Finish即可完成项目创建:

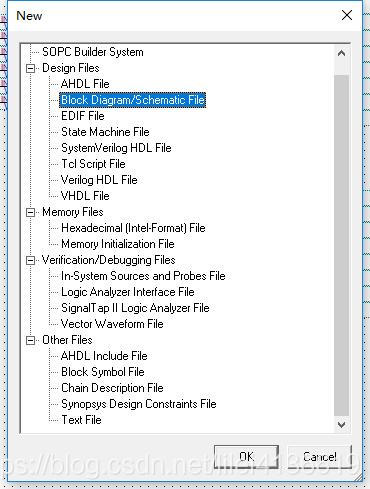

2.为项目添加文件

为项目添加新文件:

选择添加框图/示意文件(Block Diagram/Schematic File):

在新窗口中添加所需元件:

元件添加窗口中包含众多常用元件,如74系列芯片、基本逻辑门等,通过各种元件的组合可以实现你想要的功能。

添加元件搭建4-16译码器:

搭建完成后进行编译:

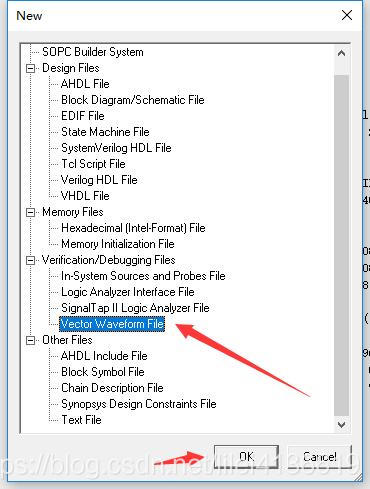

添加波形仿真文件(Vector Waveform File):

在波形仿真文件中添加输入输出引脚:

利用Node Finder工具批量添加引脚:

为输入引脚添加输入信号波形:

3.仿真

波形仿真及结果:

三.实验结果

从上图仿真结果波形可以看出两个74138译码器经过适当连接可以构成4-16译码器,同时可以看到在某些输入信号跳变的时刻输出波形中出现了毛刺,这就是竞争冒险现象。

版权声明:本文为lilei4136619原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。