一、设计内容

设计一个8位可逆计数器,可逆计数器真值表为:

输入 | 输出 | |||

CLR | EN | UPDOWN | CLK | Q7...Q0 |

1 | X | 0 | ||

0 | 0 | 不变 | ||

0 | 1 | 1 | 上升沿 | 计数器加1 |

0 | 1 | 0 | 上升沿 | 计数器减1 |

二、设计思路

判断时钟的上升沿,对输出结果进行加一、减一处理

CLR为复位信号,高电平置零;EN为使能端,低电平有效;

UPDOWN:调节计数器加一、减一的按钮,高电平+1。

三、设计代码

计数器设计代码:

//filename:Countor.v

// Edit by xixihahasoso on 2022/5/6

// 8 bit Countor

module Countor ( CLR, EN, CLK, UPDOWN, Q);

input CLR, EN, CLK, UPDOWN;

output [7:0] Q;

reg [7:0] Q;

always @ (posedge CLK) begin

if (CLR)

Q = 1'b0;

else if (!EN)

Q = Q;

else if(UPDOWN)

Q = Q + 1'b1;

else

Q = Q - 1'b1;

end

endmodule

验证代码:

//filename:Countortb.v

// Edit by xixihahasoso on 2022/5/6

// 8 bit Countor_tb

`timescale 1ns/1ns

module Countor_tb();

reg CLR, EN, CLK, UPDOWN;

wire [7:0] Q;

parameter Period = 20;

Countor test ( CLR, EN, CLK, UPDOWN, Q);

always begin

#(Period/2)

CLK = ~ CLK;

end

initial begin

CLR = 1; EN = 0; CLK = 0; UPDOWN = 0;

#25 CLR <= 0;

#30 EN <= 1;

#100 UPDOWN <= 1;

#500 $finish;

end

endmodule

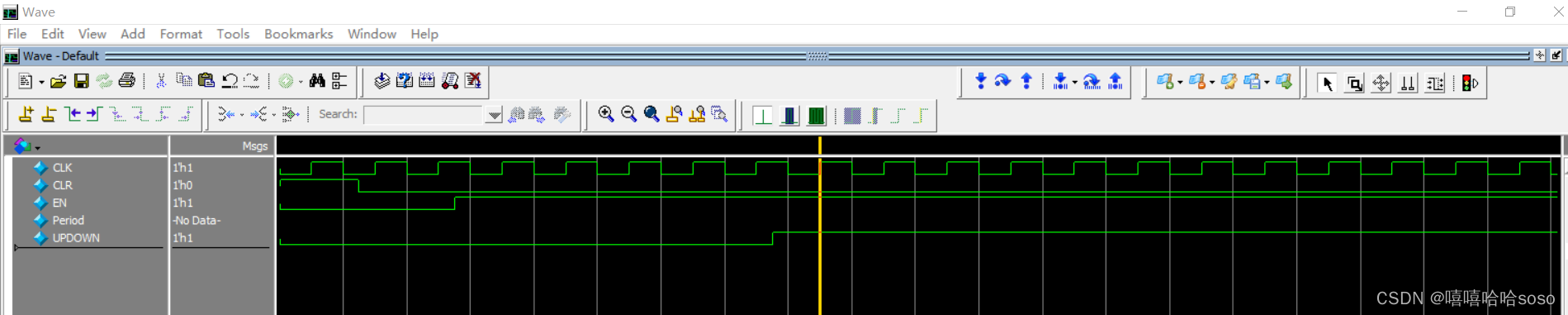

四、仿真结果

五、总结

虽然代码只有十几行,但是是没有参考任何代码,自己独自完成的,还是很开心的。

小菜鸡的修行之路还很长远,继续努力!

哦,来到这打卡,是因为一个同学给我分享了好几次自己的作业,我觉得这里有许多可以学习的前辈,在这打卡可以促进我前进,可行<Yeah!>

版权声明:本文为qq_39591444原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。