1、功能

将输入的3位二进制数译成十进制的8位输出。

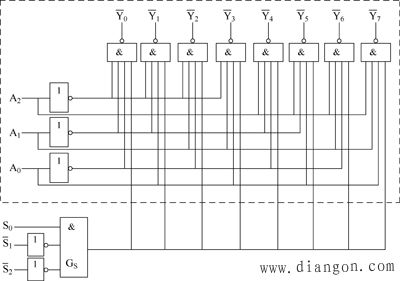

译码器是将每种二进制的组合代码译成对应的输出线上的高低电平信号。其逻辑图如下:

2、真值表

| A | B | C | out |

| 0 | 0 | 0 | 0000_0001 |

| 0 | 0 | 1 | 0000_0010 |

| 0 | 1 | 0 | 0000_0100 |

| 0 | 1 | 1 | 0000_1000 |

| 1 | 0 | 0 | 0001_0000 |

| 1 | 0 | 1 | 0010_0000 |

| 1 | 1 | 0 | 0100_0000 |

| 1 | 1 | 1 | 1000_0000 |

3、代码解析

首先编写my3_8的代码:

module my3_8(a,b,c,out);

input a;//输入端口a

input b;//输入端口b

input c;//输入端口c

output reg [7:0] out;//输出端口

always@(a,b,c) begin

case({a,b,c})

3'b000:out = 8'b0000_0001; //_代表的是占位符,写不写都一致,写上便于区分

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

endcase

end

endmodulecase(控制表达式)

分支值1:begin 一条或多条语句end

分支值2:begin 一条或多条语句end

....

default:begin 一条或多条语句end

end

endcase其中,case的各分支语句没有优先级之分的,而if...case语句有优先级。case的各分支的值必须互斥,不可具有相同的分支值。default是代表除了上述情况外的其他情况。

对其进行创建testbench文件,代码如下:

`timescale 1ns/1ns

module my3_8_tb;

reg a;

reg b;

reg c;

wire [7:0] out;

my3_8 u1(

.a(a),

.b(b),

.c(c),

.out(out)

);

initial begin

a=0;b=0;c=0;

#200;

a=0;b=0;c=1;

#200;

a=0;b=1;c=0;

#200;

a=0;b=1;c=1;

#200;

a=1;b=0;c=0;

#200;

a=1;b=0;c=1;

#200;

a=1;b=1;c=0;

#200;

a=1;b=1;c=1;

#200;

$stop;

end

endmodule4、仿真结果与分析

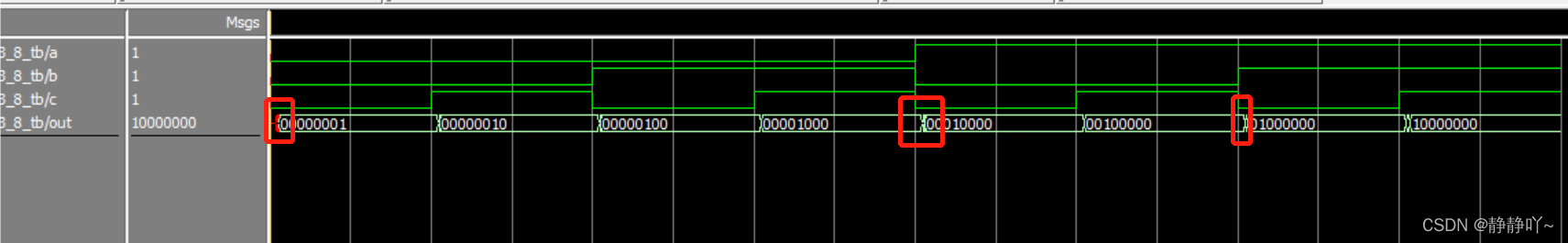

程序编写结束后,电极Assignments-settings-simulation,在这里设置仿真参数,工具名为ModelSim-Altera,程序格式为Verilog HDL,在compile test bench中设置为相应的testbench文件,设置结束后,点击RTL Simulation仿真,得到如下图所示:

在仿真图中可以看出,结果与真值表完全相同,当输入为000时,输出为0000 0001;当输入为001时,输出为0000 0010;以此类推。

关闭RTL Simulation仿真,点击Gate Level Simulation仿真,得到如下图所示:

从仿真图中可以看到刚开始的时候,输出有一段红色区域,出现了未知态,这主要是因为输出在上电的0时刻是未知的,输出是由输入决定的,并且会有一定的延迟,经过短暂时间后,恢复正常。

后仿真中出现00000011的状况主要原因:

从00000001到00000010的过程中,有两位发生变化,两位发生的变化时间不同,如下如所示:

版权声明:本文为weixin_44956956原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。