前言

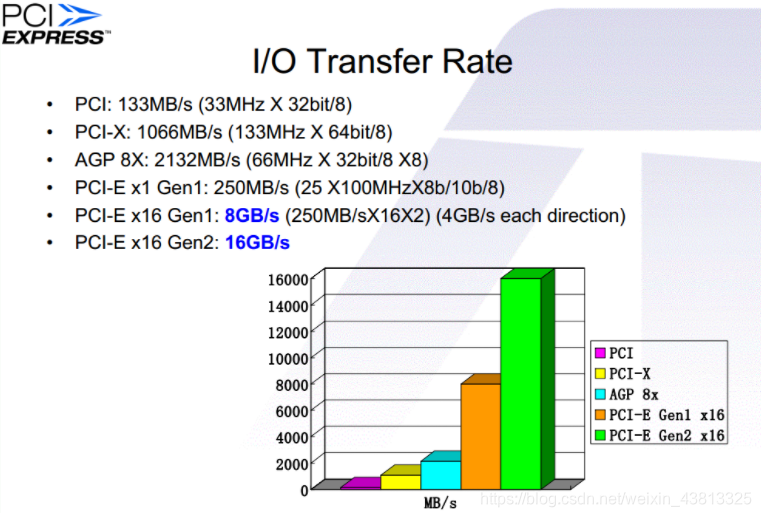

随着科技的发展,数据量需求增加,高速数据传输接口就显得越来越重要了,相较PCIe的前辈PCI的单端并行传输数据的方式,PCIe采用高速串行传输数据,采用差分信号降低共模信号干扰,采用更高的时钟并将时钟信号嵌入数据流中,而不是单独的时钟信号,这样就避免了时钟产生的时延等问题,高速串行传输代替并行是大势所趋,像高速AD/DAJESD数据接口也是一种串行传输的方式。

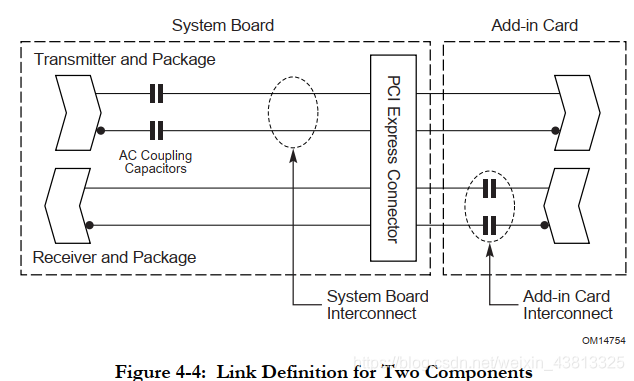

和PCI并行总线架构不同PCIe是点对点的连接方式,每组链接称为一个link,包含1-16条lane(x1,x2,x4,x8,x16)

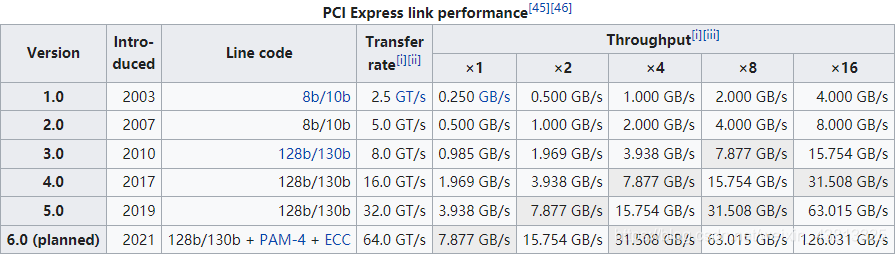

,PCIe gen 1/2/3/4/5速率如下图所示,主要是在编码方式和速率上的区别,其中GT表示链路的峰值带宽,是总线频率x数据宽度x2(T/R),不同版本不同lane数的速率计算公式: gen 1/2速率=Transfer rate *8/10 * lane数据(8b/10B编码),gen 3/4/5速率=Transfer rate *128/130 *lane数据(128b/130B编码)

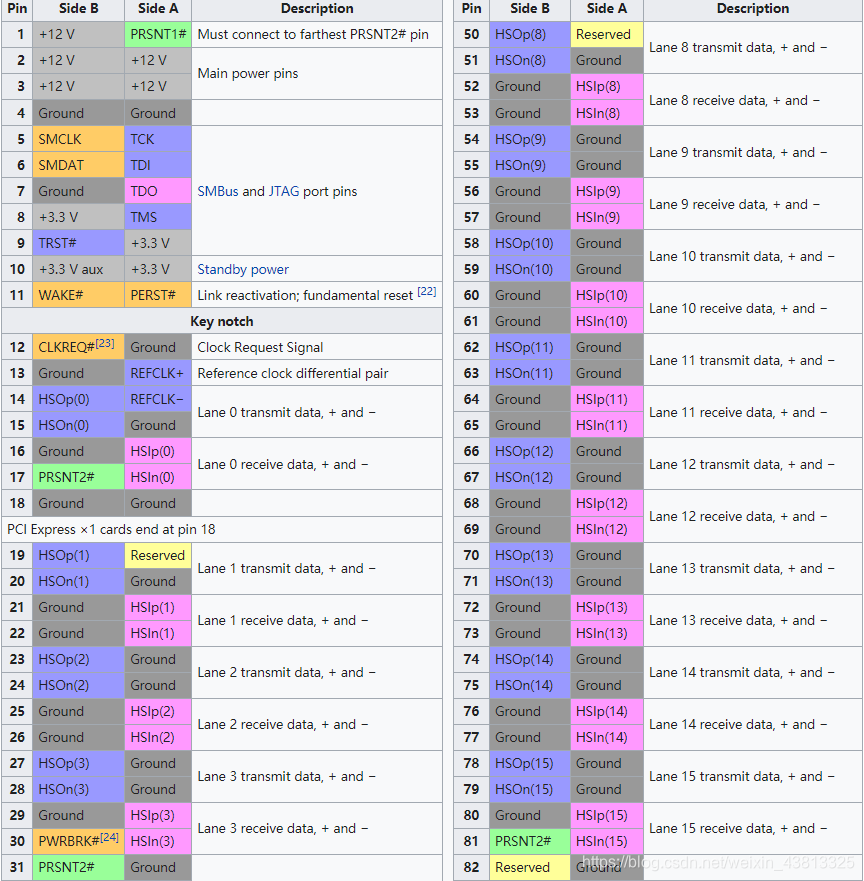

PCIe连接器引脚定义

关键信号描述

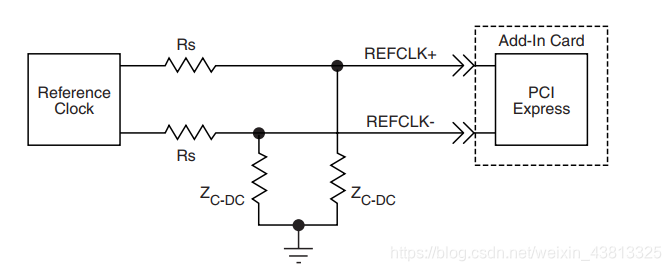

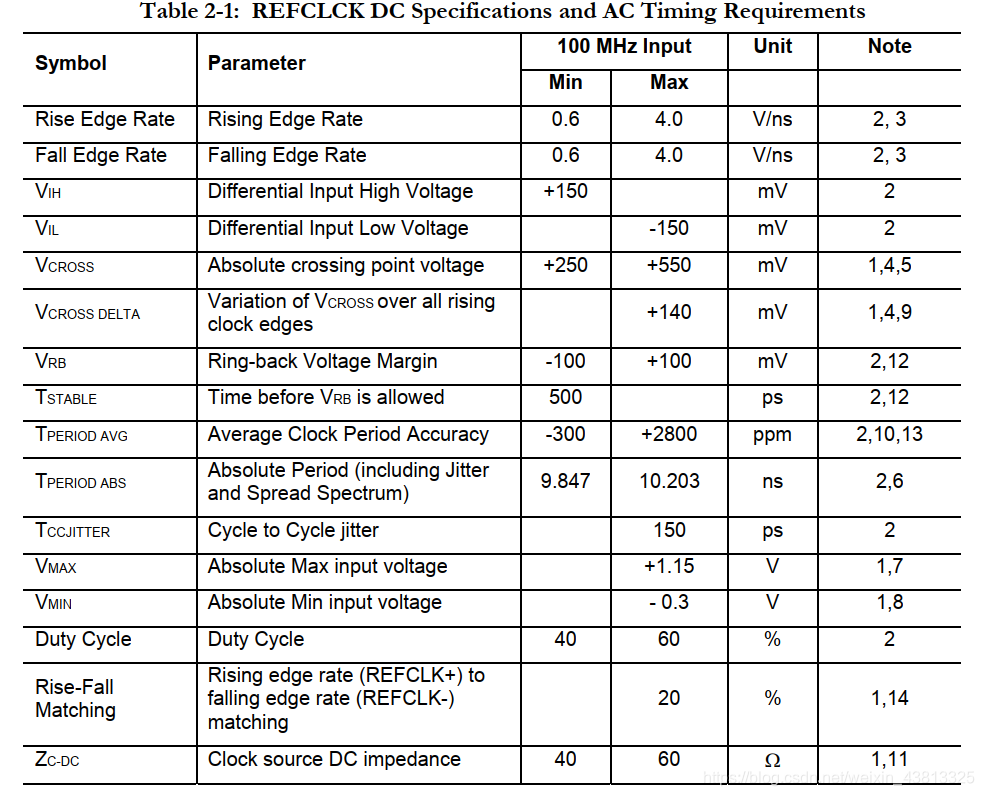

REFCLK+/- : 单端摆幅0-0.7V、频率100M±300ppm,RS防止信号振铃和EMI辐射,时钟的端接电路一般需要接在系统板上,接收端(PCIE扣卡)端接会降低信号摆幅和上升下降沿时间,需要确认是否满足需求,时钟按照100R阻抗、5mil trace width、扣板上最大走线长度12000mil,端接ZC-DC(40~60R),时钟用于做处理器系统和插卡之间同步,PCIE插卡可以使用插槽提供的时钟,也可以使用独立的参考时钟,但需要在设备配置空间中进行相应配置。

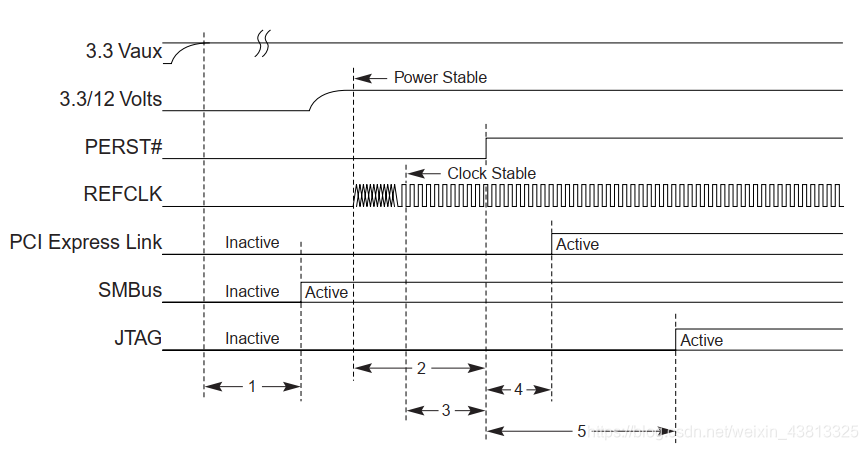

PERST#:

一上电,将PERST#信号拉低100ms,在这之前电源和时钟都将能够处于稳定工作状态。

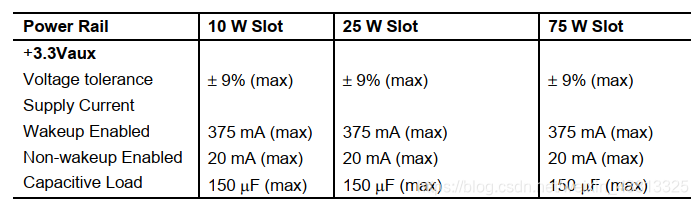

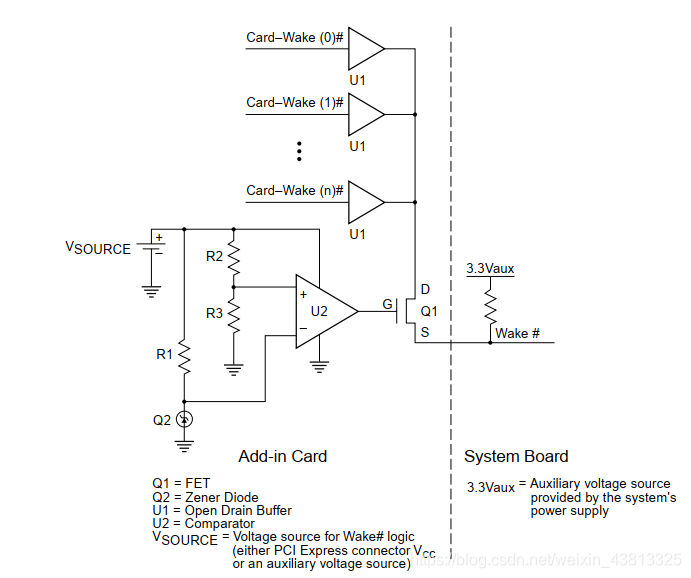

WAKE#:当设备进入休眠状态时,主电源已经停止供电,PCIE设备使用该信号向处理器系统申请唤醒请求,并提供主电源供电,PCIE设备中WAKE#信号是一个可选功能,当使用该功能时必须使用VCCAUX供电。WAKE#是一个开漏信号,因此当具有多个PCIE设备时可以将所有WAKE#信号线与之后接入处理器系统。当某PCIE设备需要被唤醒时,该设备现将WAKE#信号拉低,处理器设备识别到唤醒请求之后将为PCIE设备供主电源,并使用PERST#对其进行复位,长复位完成之前,电源和时钟将逐渐稳定状态,此时WAKE#信号保持拉低状态,当复位完成WAKE#也将拉高。

JTAG:

联合测试行为组,用于调试时使用,是可选项,不使用时悬空。

SMBCLK/SMB DAT:

类似I2C总线,但时钟频率有区别,SMbus最高时钟频率100KHz,支持超时功能,处理器系统可利用该功能复位从设备。

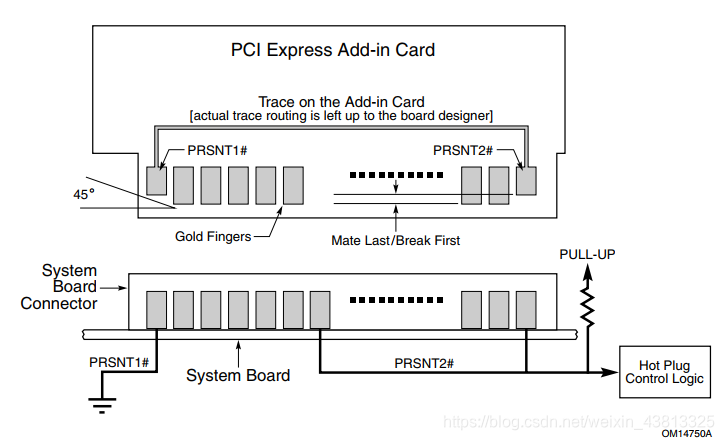

PRSNT1#/PRSNT2#:

PRSNT1#/PRSNT2#用于处理器系统检测插卡是否存在,当插卡插上处理器系统时,原本上拉的PRSNT2#信号立即被拉低,此时表示插卡被插入系统。

PET/Rpx/nx:收发差分数据线,PCIE支持x1、x2、x4、x8、x16多个lane,链路中在发送端串电容,实现交流耦合。

电源上电时序

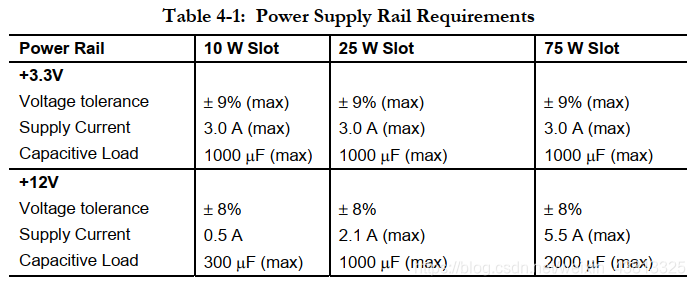

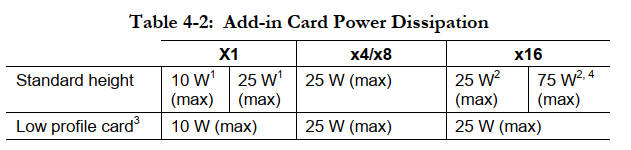

没有上电时序要求。插卡功耗范围:

不同功耗下各个点电压说明: