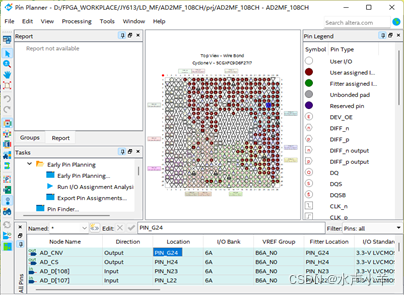

问题:传统FPGA管脚分配方法可以通过Quartus软件界面Pin Planner一一配置,但做毕业设计时共用6片FPGA,每片FPGA需分配200个左右IO,共需分配上千个IO,手动分配效率极低且容易出错,还不易修改。

解决方法:采用了结合Altium Designer和文本编辑器,编写qsf脚本的方式分配FPGA IO管脚,具体步骤如下,此方法方便高效,可以准确的分配6片FPGA的IO管脚。

图1 Pin Planner分配管脚图

1、在“AD”软件中打开FPGA原理图,将原理图FPGA的部分转换元器件为图纸符号。去掉与分配管脚无关的连接,只保留想要连接的管脚。

2、点击 tools-convert-Push part to sheet

3、点击设计,生成FPGA原理图的网表,并转换为Verilog文件。

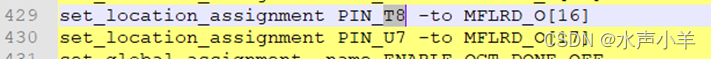

4、使用文本编辑器修改生成的.v文件为qsf文件格式:即删除文件前面和后面多余部分、使用“*_*_*_”替换为“set_location_assignment PIN_”、“NamedIOSignal_”替换为“-to”、“)*^p” 替换为“^p”、“-to ”替换“,”、排序后“,”替换“-to”就完成.v文件变为.qsf文件。

图2 FPGA原理图网表转化.v文件

图3 转化.v文件格式

图4 转化.qsf文件格式

版权声明:本文为xiansaitan5036原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。