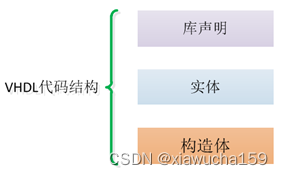

VHDL代码结构

VHDL代码结构包括3个基本组成部分:

①库声明(LIBRARY)

②实体 (ENTITY)

③构造体 (ARCHITECTURE)

如图:

学习迁移

与C语言对比,学习理解会相对容易,尤其对于初学者来说

库类似于C语言的中的头文件

实体entity类似于C语言的各种变量,但是在fpga里要集中放在头部。

构造体类似于C语言的代码块或功能函数。

库声明

库声明:列出当前设计文件里需要用到的所有库文件,如ieee,std work等。

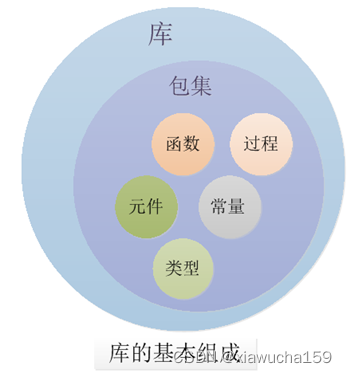

库是一些常用代码的集合,将电路设计中经常使用的一些代码存放到库中有利于设计的重用和代码共享。

库的典型结构如下图,其中代码经常以函数,过程,或元件等标准形式存放在包集中,用户可以根据需要对其进行编译使用。

库声明作用

库声明有利于设计重用和代码共享,同时可以使代码结构_更加清晰。

库的种类

库的种类包括3种常用库:

① ieee库

② std 库

③ work库

3种库的详细介绍

ieee库 包含了许多包集(代码包的集合)

举例:

std_logic_1164: 定义了STD_LOGIC(8值)和 STD_ULOGIC(9值)多值逻辑系统。

std_logic_arith: 定义了SIGNED(有符号)和UNSIGNED

(无符号)数据类型和相关的算数运算和比较运算的操作。

包含许多数据类型转换的函数,可以实现数据类型的转换。

std_logic_signed: 内部包含了一些函数,这些函数可以使STD_LOGIC_VECTOR类型的数据像SIGNED类型的数据一样进行运算操作。

std_logic_unsigned: 内部包含了一些函数,这些函数可以使STD_LOGIC_VECTOR类型的数据像UNSIGNED类型的数据一样进行运算操作。

std库

std库是VHDL的标准资源库,包括数据类型和输入/输出文本等内容。std库中存放有包集standard和textio。

work库

work库是当前的工作库,当前设计的所有代码都存放在work库中,使用work库不需要进行任何声明。

VHDL代码结构举例:

--文件名:tp_test_single.VHD

--功能描述: 示波器测试脚查看

--作者:xiawucha159

--版本:V1.0-2022.06.01编写

--公司:

--版权:

①

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

②

entity tp_test_single is

port(

tp_0 :in std_logic;

tp_1 :in std_logic;

tp_2 :in std_logic;

tp_3 :in std_logic;

tp_4 :in std_logic;

tp_5 :in std_logic;

tp_6 :in std_logic;

tp_7 :in std_logic;

tp_out :out std_logic_vector(7 downto 0)

)

end tp_test_single;

③

architecture BEHAVIOR of tp_test_single is

begin

tp_out <= tp_7 & tp_6 & tp_5 &tp_4 & tp_3 & tp_2 &tp_1 & tp_0;

end BEHAVIOR;

其中①②③分别对应了 库声明、实体、 构造体。

VHDL代码结构中3个基本组成部分的作用

库 :提供常用代码集合。

实体: 描述电路的所有输入输出引脚

构造体: 描述电路行为和要实现的功能。

迁移理解

> FPGA一个.vhd文件可以认为成是一块电路,用软件写代码画出来的一块硬件电路,类似于PCB的一块电路板。