VC Spyglass CDC

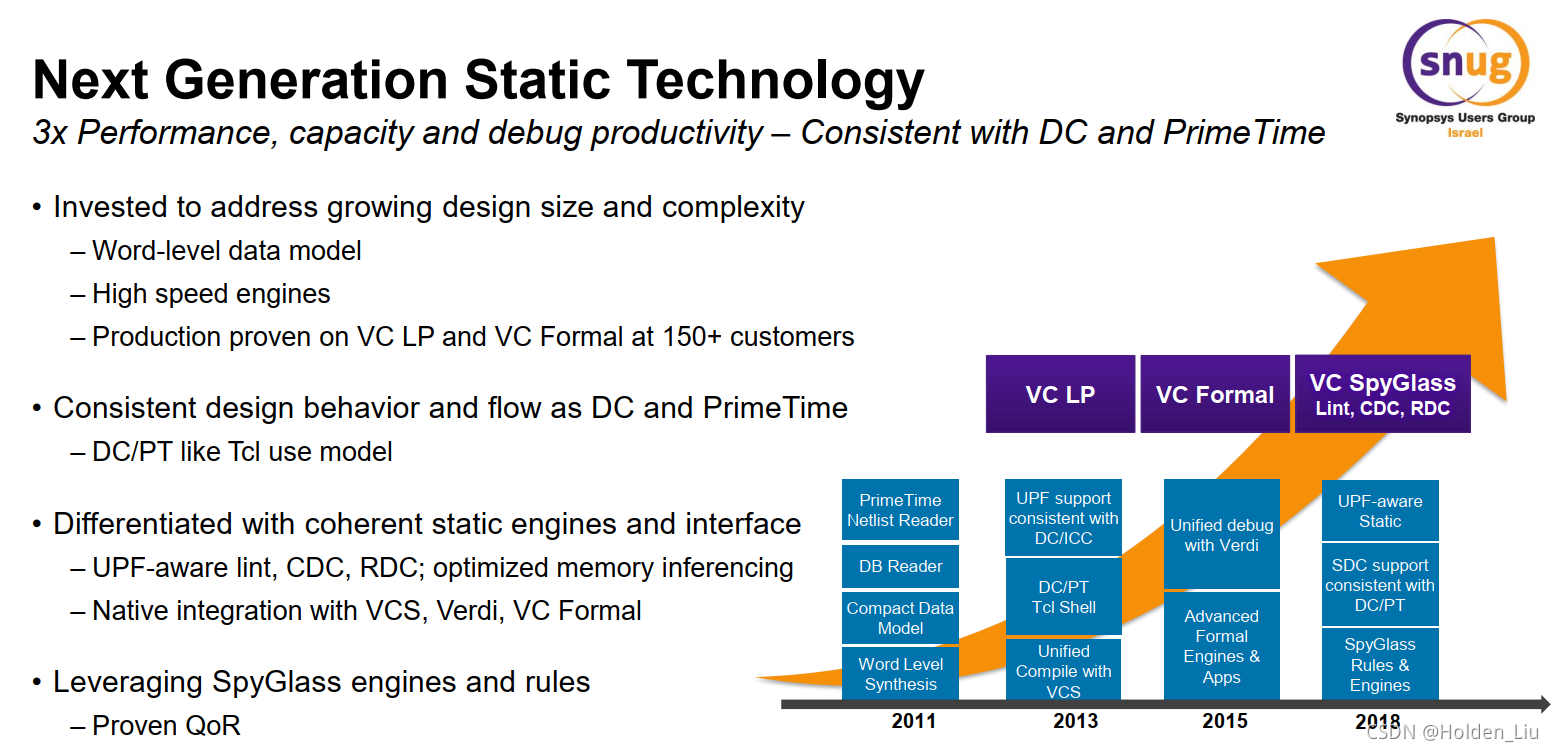

Synopsys Verification Continuum的静态验证平台VC static platform包含了VC LP,VC formal,VC Spyglass三种静态检查工具。Spyglass原是Atrenta旗下的静态检查工具,占据CDC/RDC sign-off工具的大部分市场份额。后来Synopsys收购了Atrenta,整合Spyglass推出了VC Spyglass。VC Spyglass作为Synopsys推出的期望继承Spyglass的新一代产品,兼容原有Spyglass的Use Mode,提供更高性能和更多功能,和PT/DC工具的命令兼容,采用Verdi的debug界面,加入Machine Learning,低误报,对Netlist/低功耗的支持等优势。

与Spyglass CDC的区别

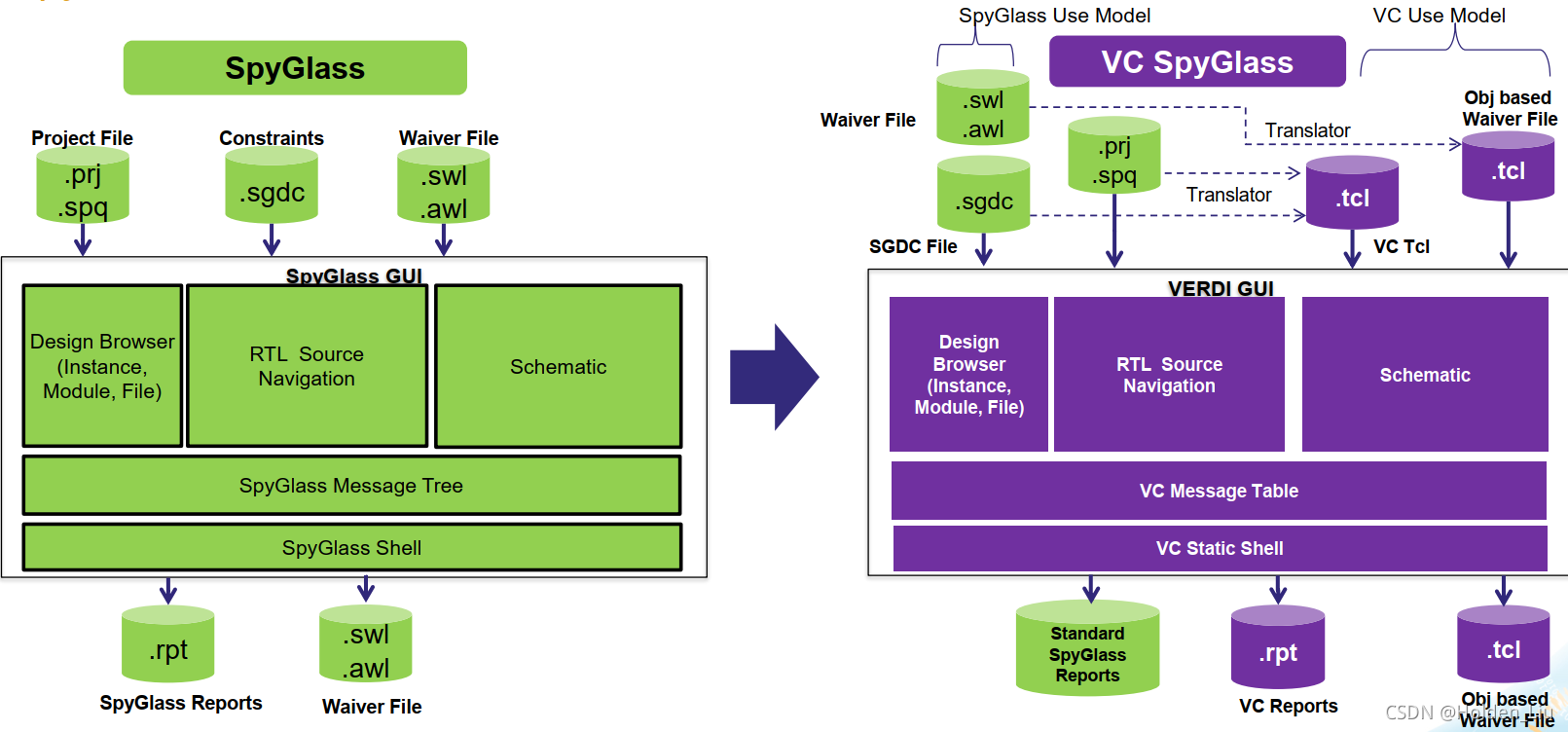

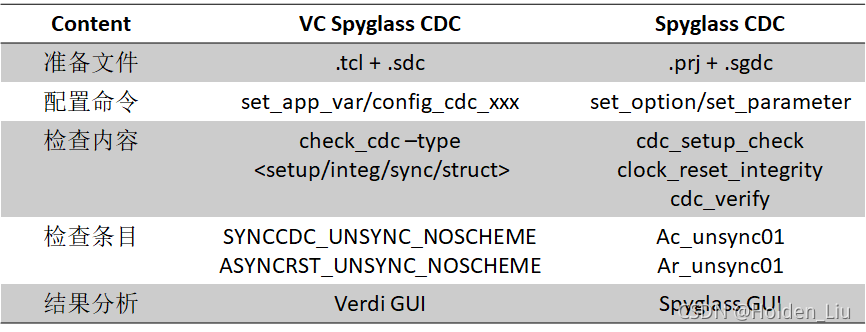

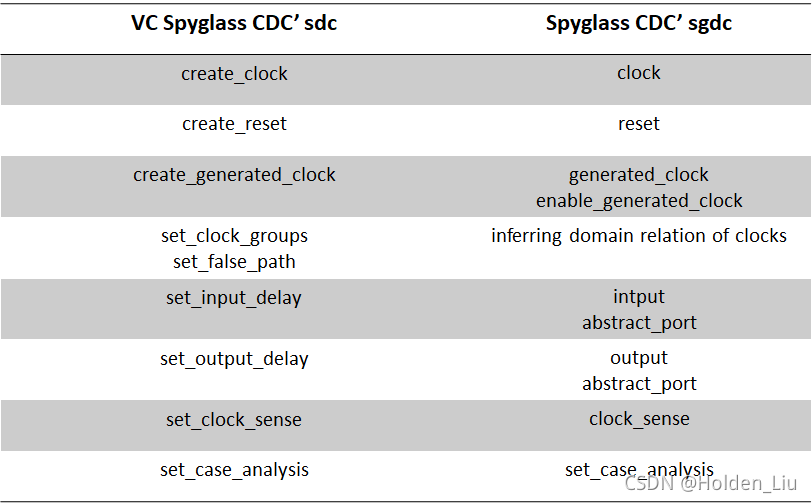

VC Spyglass的时钟约束由sdc提供,和DC PT工具一样。而Spyglass的由sgdc提供。

sdc与sgdc在命令上有区别。sdc可以转化成sgdc的形式。

VC Spyglass也支持SpyGlass Use Model,可以吃进SpyGlass的工程文件进行CDC check,利于将过往项目往新工具上迁移。

VC Spyglass和DC类似,对于工具变量的配置都是使用set_app_var

VC Spyglass对CDC的检查分为四类,都是仅从结构上做检查

相同违例的上报归类为一种Tag,形式和Spyglass略有不同,具体rule的内容也有些差别。

VC Spyglass的GUI界面是VCst Activity View + Verdi,trace code/schematic 都是在Verdi中查看。

VC Spyglass可以参考DC的sdc创建,复用其中的一部分内容。

CDC工具只关心设计中哪些object属于哪些clock domain,提供了这些信息,就可以做check了。

set_false_path对于DC是忽略路径上的时序约束,而VC Spyglass则当作异步路径,做CDC check。

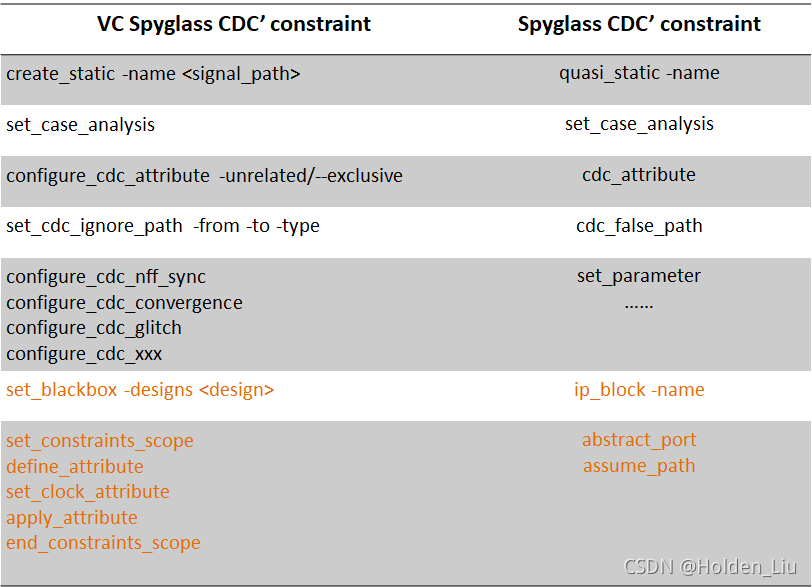

根据设计意图,添加约束

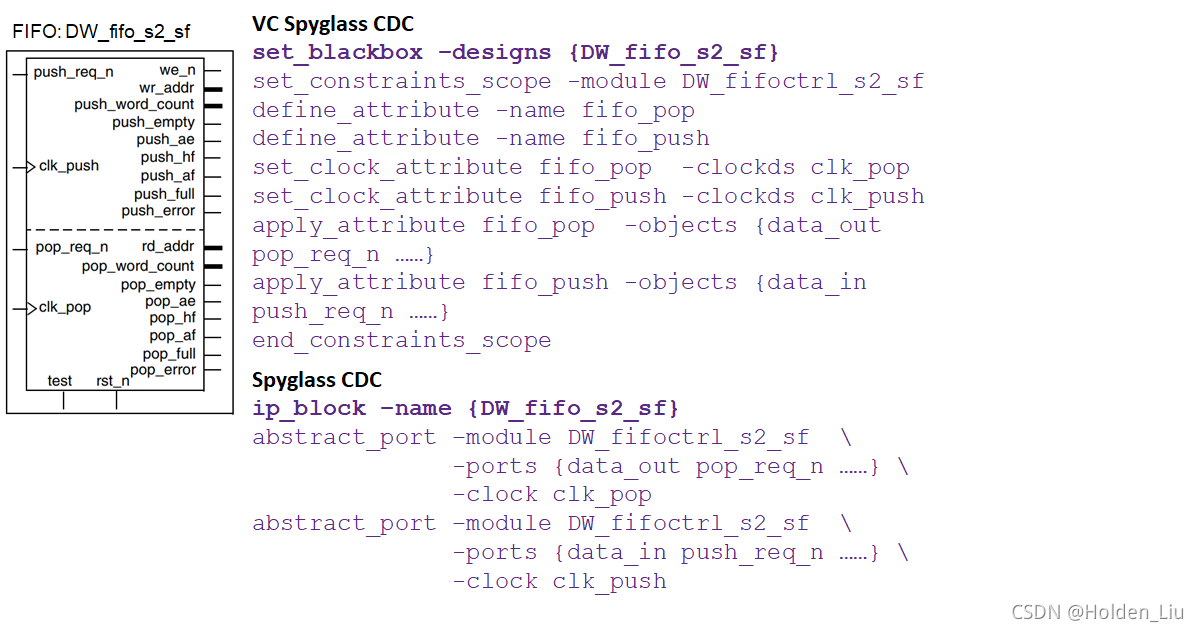

对于一些第三方golden模块,可以设置为黑盒,不做CDC检查。但是模块边界处需要指定clock domain的约束。VC Spyglass可以使用一系列attribute命令描述,相比Spyglass,可读性更强。

更多复杂的使用示例,参考?VC Spyglass 对比 Spyglass 描述抽象模型 abstract port

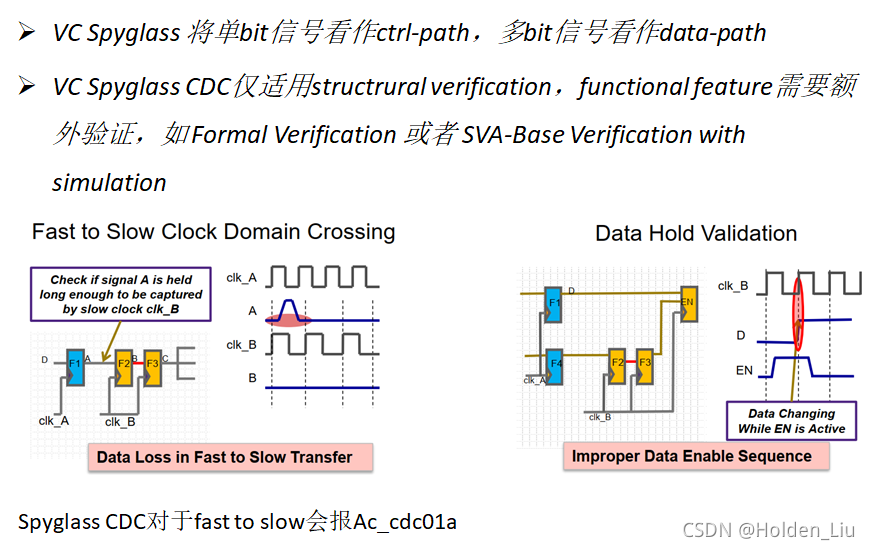

VC Spyglass仅从结构上做检查,例如单比特信号经过两级寄存器同步后,工具认为符合CDC要求。但是信号如果是脉冲类型,存在漏采,不满足功能上的要求,正确方法是使用脉冲同步器。

对于多bit data信号的传递,如下电路从结构上是正确的,CDC check pass。但是如果data在data_vaild assert时发生改变,也会引起亚稳态。但这属于功能问题,VC Spyglass还无法检查。

对于功能检查部分,可以采用Formal Verification 或者 SVA-Base Verification with simulation。

VC Spyglass Hybrid Flow可以根据当前约束产生相应的SVAs,用于simulation,一方面可以检查function 功能,另一方面也可以确认CDC约束是否正确。

reset同步释放的SVA:? assertion for reset synchronous release

clock switch和glitch检测的SVA:?assertion for clock switch and clock glitch