简介

随着工艺的提高IC在集成度和性能方面一直在不断地进步,但功耗却越来越大,尤其在32nm工艺后静态功耗已经超过了动态功耗。

功耗越大,芯片的有源区温度越高,则芯片的失效率越高、寿命越低。现代数字IC对于低功耗的要求甚至已经超过对于性能的要求。

功耗组成

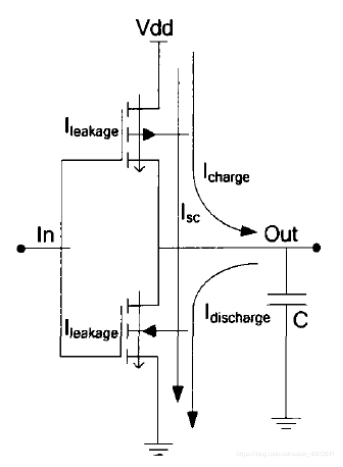

以CMOS IC为例,功耗分为静态功耗,动态功耗,短路功耗。

动态功耗表示电路完成一次翻转所消耗的能量。

短路功耗表示电路在翻转时由于PN管的直接导通造成的功耗损失。

静态功耗指电路在不工作时依然有功耗产生。

P=CVDD2fNsw+QscVDDfNsw+IleakVDD

式中,f为时钟频率Nsw为活动因子(即周期内输出节点发生变化的次数)Ileak为漏电流。

漏电流包括:

栅漏电流,亚阈值电流,PN结反向电流等等。

降低功耗的方法

电压控制

多电压域:

由于功耗与电源电压的平方成正比,与其他变量均呈线性关系,因此可以考虑降低电源电压来直接降低功耗,但电源电压的降低会导致电路的驱动能力下降,使得延时增大。

所以可以在一个设计中加入多个电压,在关键路径采用高电压以保持延时尽量的小,在一些非关键路径采用低电压以降低功耗。

多阈值域:

降低阈值电压可以减小同电源电压下的延迟,使电源电压的降低幅度可以更大,但会导致亚阈值电流的增加和低电平噪声容限的下降。

可以利用不同的衬底掺杂工艺,可制造出两种不同阈值电压的MOSFET,与多电压域方法相比,多阈值方法无需改变电路结构,不会增加面积开销和布局难度,但需多阈值工艺支持,因增加了工序和掩模,成本比单阈值工艺高。

动态电压调节:

由于系统工作时,并不是每时每刻都要保持高速处理状态,例如在处理文本任务时大部分电路处于空闲状态,故在系统高速工作的时候提供正常电压,在系统休闲时候采用低电压。

自适应体偏置:

在芯片上安装漏电传感器来检测漏电流的大小,如发现超漏电超过额定值就启动阱偏置电路来改变衬底偏压,增加阈值电压,使漏电流降至允许值之下,这种方法就称为自适应体偏置。

由于最差情况设计:

一般一块芯片上性能极差的电路占据较小的部分,如果全部按照最差的情况设计,会使得功耗急剧的增加,所以引入纠错机制保证那些性能差的电路能够在错误运行状态下纠正过来,这样使得电路工作环境不那么严苛,以此来降低电路的功耗。

待机控制

思想:

当系统不工作时,使得电路处于一种待机或睡眠状态以降低功耗,但需要一定的时间恢复到常态。

门控电源:

当芯片处于待机或睡眠模式时,切断不工作部分电路的电源以降低功耗。

门控时钟:

在时钟信号输入之前,加一个使能信号与时钟信号相“与”,当电路不工作时用来关断无需工作的单元,从而降低了相关电路以及时钟树导致的功耗。

门控输入:

无需运算时,将电路的输入置于某个固定的值,使之不再运算,从而降低动态功耗。

电路的优化

协同优化:

由于降低功耗会带来延时的增加,减小延时又不得不增大电压带来更大的功耗,所以以能量·延迟积最小化作为目标来优化。对于时间余量大的路径可以增加面积,提高阈值电压等方式来降低功耗。

降低翻转频度:

由于数字电路中间电路翻转的频率与信号输入的位置有关,所以输入输出重新排序,让翻转概率高的信号的接入点尽可能靠近输出节点来降低翻转频率。

互联线:

由于长的互连线通过会加入中继器来降低延时,而中继器又会带来额外的功耗,故可以对中继器进行优化。