主存储器基本组成

半导体元器件原理

· 存储器主要由存储体、地址寄存器、数据寄存器组成(图左上);这三部分在时序控制逻辑电路的组织下有条不紊的进行工作(图右上);简而言之就是存储芯片由存储器和控制电路组成

· 存储体(图右下)由存储单元构成,存储单元由存储元构成;

· 存储元(图左下)是一个电路,包含2个半导体元件:MOS管、电容;

· MOS管:输入高电压即可导通,不加电压或低电压则绝缘

· 电容:2个金属板和中间的绝缘体构成;给上金属板加高电压,地下金属板接地为0,则上下产生电压差,电容开始充电,电容上保存了电荷则对应二进制的1;

· 读取二进制:给MOS管加高电压,MOS管接通,电容里有电荷可以向外流出,则就是二进制的1

· 多个存储元相互连接,上边的红线连着存储元的MOS管,当红线加高电压,即MOS管都接通,如果绿色线检测到有电流,则该存储元存储了二进制1,一次性可以读出一整行存储元存储的二进制信息,一整行存储元就是一个存储单元也是一个存储字- - - 一个存储单元(一个存储字)的存储元的MOS都连在一根线上

存储芯片的组成原理

· 译码器(图坐下):根据MAR给出的地址,将 某1条 字选线变成高电平信号;每1 个地址对应译码器的 1 跟字选线,MAR有n位,则译码器有2的n次方跟字选线

· 译码器(图坐下):根据MAR给出的地址,将 某1条 字选线变成高电平信号;每1 个地址对应译码器的 1 跟字选线,MAR有n位,则译码器有2的n次方跟字选线

· 本存储单元的字选线上有高电平信号时,存储单元内的每个存储元的数据线(位线)(图右上绿色线)会将存储元内的电流信号串给MDR,从而读出本存储单元的内容

· 上图所示芯片只有译码器、MAR、MDR还不够完整,还需要增加控制电路(如下图),才是一个存储芯片

· 控制电路:控制译码器、MAR、MDR

· 作用一:MAR和译码器

···········CPU通过地址总线将地址信息传送给MAR,使用电信号传送难免会有不稳定的情况出现,所以当MAR中的电信号稳定下来之前,MAR中的地址信号是不能送给译码器的;只有MAR中的电型号稳定下来后,控制电路才会打开译码器的开关;

· 作用二:MDR和数据总线

···········只有MDR中的电信号稳定后,控制电路才会允许MDR将内容传给数据总线

· 作用三:芯片是否处于可工作状态

···········片选线CE或CS被加上低电平的时候,这个芯片才处于可工作状态,类似于这个芯片的“总开关”

· 作用四:读写状态表示

··········有2中表示策略,一种是读控制线和写控制线分开,当读控制线被加上低电平时,表示现在要进行度操作,写控制线同样;另一种中读写控制线于一体,高电平表示写状态,低电平表示读状态

以上就是一个存储芯片内部完整的功能部分了,接下来是将这些细节封装后的示意图(图左下)

· 存储矩阵:存储元组成的存储单元、存储单元组成的存储体

· 译码驱动:译码器和驱动器;驱动器- - -通常加载译码器后方,保证译码器输出给字选线的电信号稳定有效,将电信号进行放大的部件

· 读写电路:控制电路、字选线、位选线

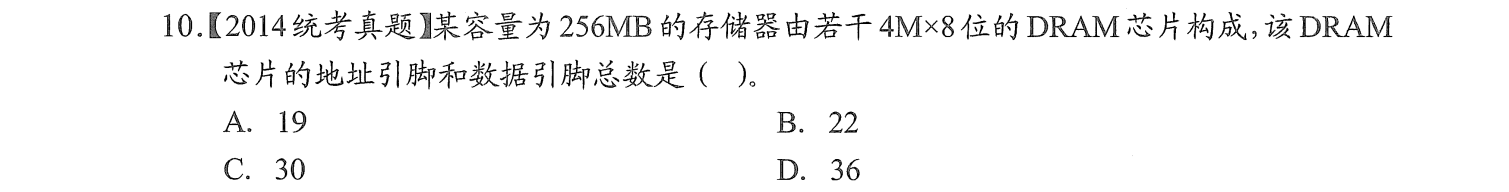

· 常见题目:问该存储芯片对外暴露的金属引脚数目;地址线、片选线、读写控制线、数据线的引脚数目总和

· 存储芯片的容量描述:存储单元个数 * 存储字长(如下图);根据存储单元个数得到地址线引脚个数,根据存储字长得到数据线引脚个数

寻址方式

2种特定类型的RAM芯片

动态DRAM和静态SRAM的特性差别

· 上文存储芯片组成结构讲的就是DRAM的结构,存储元是栅极电容

栅极电容V.S.双稳态触发器

双稳态触发器

· (上图右)包含M1~M6 6个MOS管

· 双稳态:A高B低表示1,A低B高表示0

· 2根数据输出线:不同的线上是低电平时对应0或1

两者区别

· 读写数据

··············栅极电容- - -破坏性读出;双稳态触发器- - -非破坏性读出;

··············DRAM芯片- - -读写速度慢;SRAM芯片- - - 读写速度快;

··············DRAM芯片- - - 主存;SRAM芯片- - -Cache;

· 制造成本

··············栅极电容- - -仅2个半导体元件,成本更低;双稳态触发器- - - 好多个半导体元,成本高

· 集成度

·············芯片大小不能改变时,DRAM芯片有更高的集成度

· 功耗

·············栅极电容的电路简单,DRAM芯片功耗低 · 注:DRAM和SRAM都是易失性存储器

· 注:DRAM和SRAM都是易失性存储器

DRAM的刷新

1.多久刷新一次?

2.每次刷新多少存储单元?

什么是一行存储单元?

· 给出一个行地址,行地址译码器就会选中该行所有的存储单元

为什么要使用行列地址?

· 如果有n为地址即MAR有n位,译码器所连接的字选线的个数就有2的n次方;如果地址有20位,那么译码器就需要连接2的20次1024*1024=1048576跟字选线,一百万跟字选线连在译码器上,在工程上实现太过于困难

· 如果将地址分为行列地址,那么20位的地址可以分为10行10列,行列译码器分别只需要管辖2的10次方即1024个字选线即可,1024根字选线连在译码器上在工程上很好实现

如何使用行列地址选中存储单元?

· 采用上图左边的地址策略

地址信息00000000使得译码器选通第0根字选线;译码器一共连接2的8次方256根字选线

· 采用上图右边的地址策略

地址信息0000 0000被分为行地址 0000和列地址0000;行译码器选通第0根行字选线,列译码器选通第0根列字选线;存储单元只有行列字选线都被选通时才能对其进行读写操作,所以此时只有第一行第一列的存储单元被选中;行译码器和列译码器分别只需要连接2的4次方16根字选线,一共32根字选线

3.如何刷新?

4.在什么时刻刷新?

分散刷新

· 每次读写完后都刷新,造成读写周期翻倍

集中刷新

· 读写周期不改变,一共4000个周期,前面3872都在读写,后面的128周期用来逐行刷新

· 标记:没看懂的题

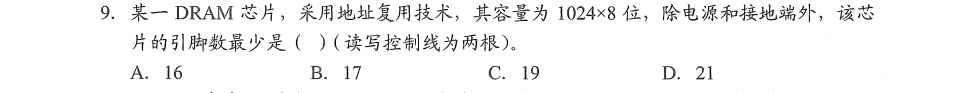

DRAM的地址线复用技术

· DRAM芯片一般是做主存,主存的存储容量要比Cache的存储容量大,相对来说地址数量就更多,所以DRAM芯片会有行列地址分开送的这个策略,SRAM没有这个顾虑

行列地址同时送

· 比如地址一共32位,行列同时送地址的话,就是把32位地址都同时一起给行、列地址译码器,就是行地址译码器和列地址译码器各自需要连接32根地址线,注意是地址线哦不是字选线

行列地址分开送

· 比如地址一共32位,行列地址分2次传送,行地址译码器和列地址译码器分别只需要连接16条地址线

· DRAM芯片采用地址线复用技术,行列地址分2次传送,地址线数量减半

· DRAM芯片采用地址线复用技术,行列地址分2次传送,地址线数量减半

· 4M个存储单元,即22位地址

· 答案:A

· 标记:没看懂的题

补充

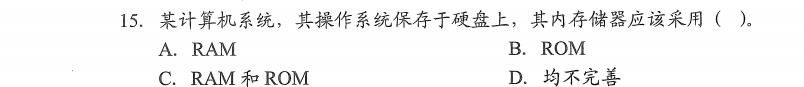

ROM芯片

了解几种ROM

计算机内重要的ROM

· 很多ROM也具有随机存取的特性

· 很多ROM也具有随机存取的特性

· Cache一般采用SRAM芯片,比ROM速度快很多

· 答案:A