目的:运用axi协议从MIG接口调用DDR

AXI接口的MIG测试【MIZ7035】

目录

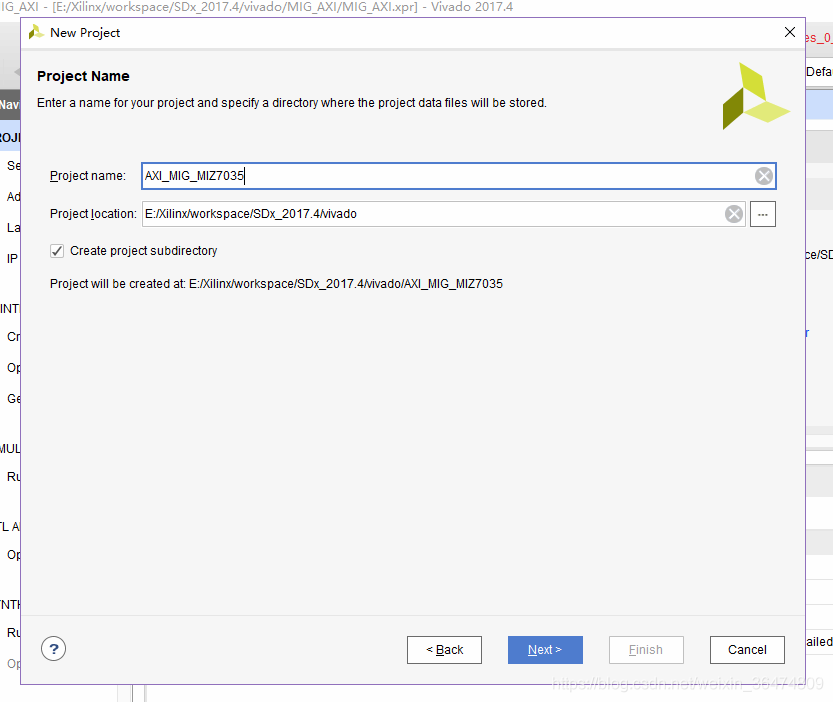

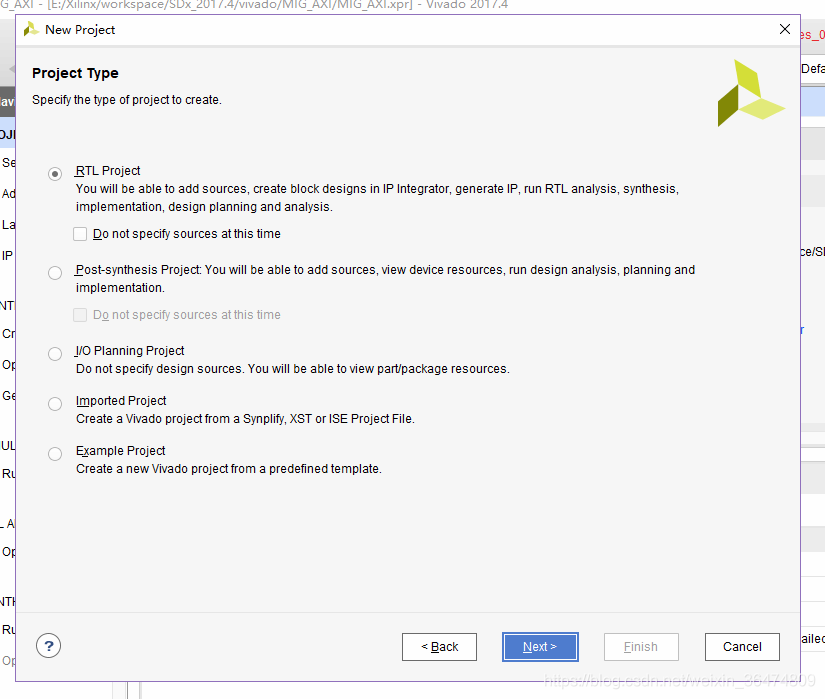

新建Vivado工程

新建工程,点击Next

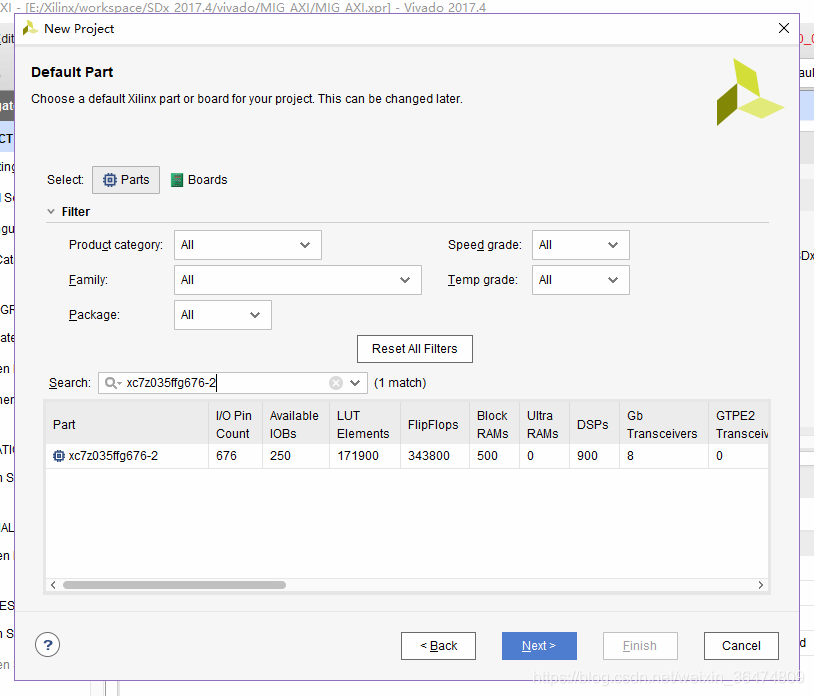

选型xc7z035ffg676-2

点击Next,Finish

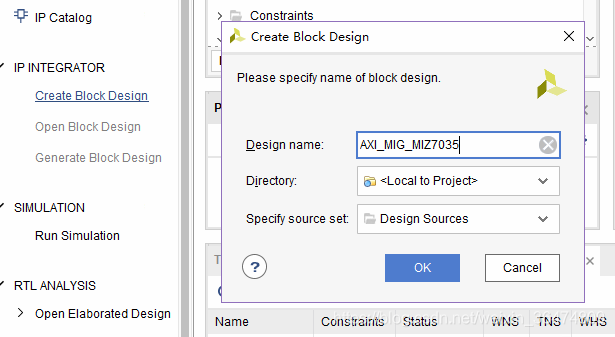

新建BD,点击OK

AXI接口的MIG IP

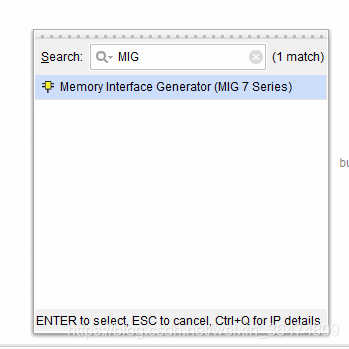

点击Add IP,添加MIG IP

双击MIG IP的GUI

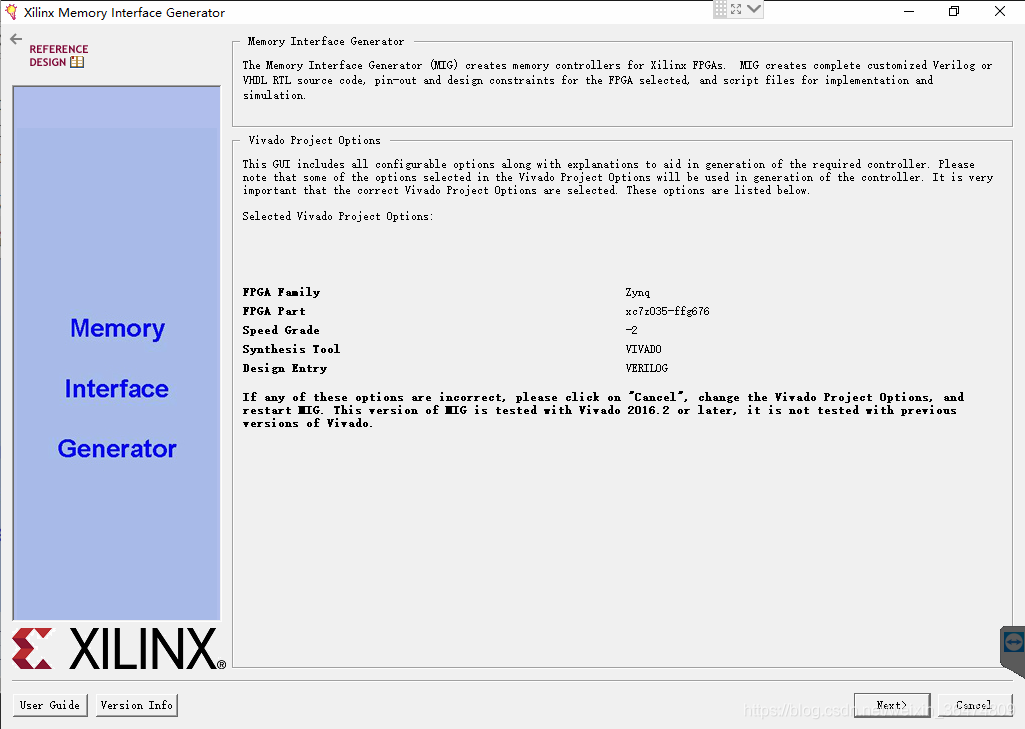

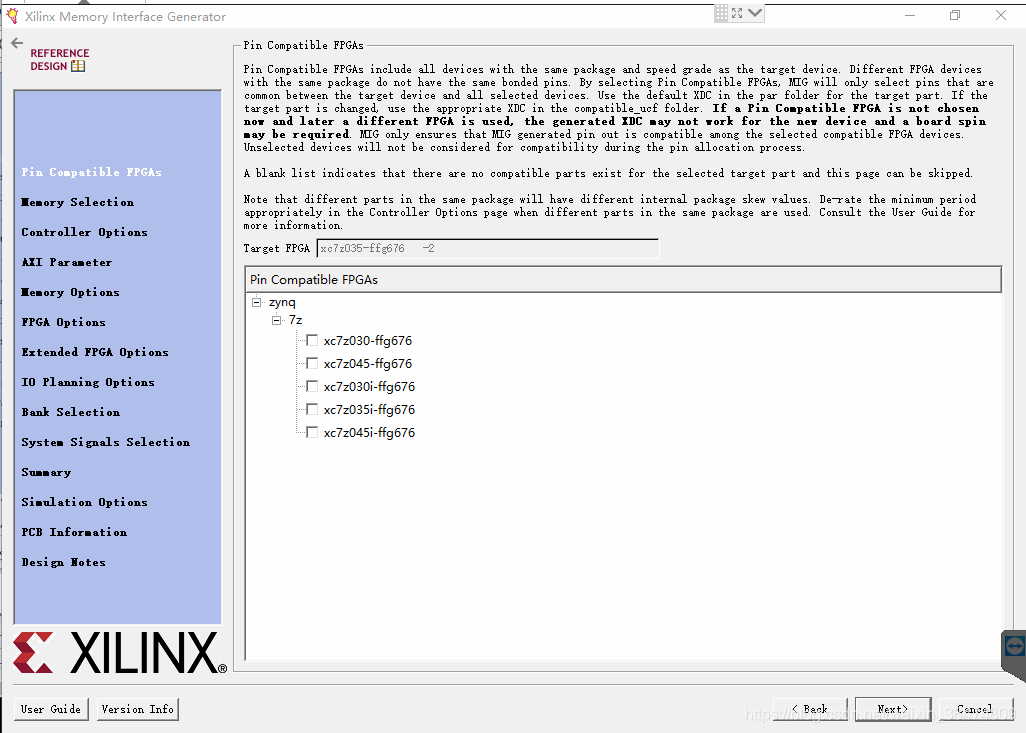

弹出窗口Xilinx Memory Interface Generator

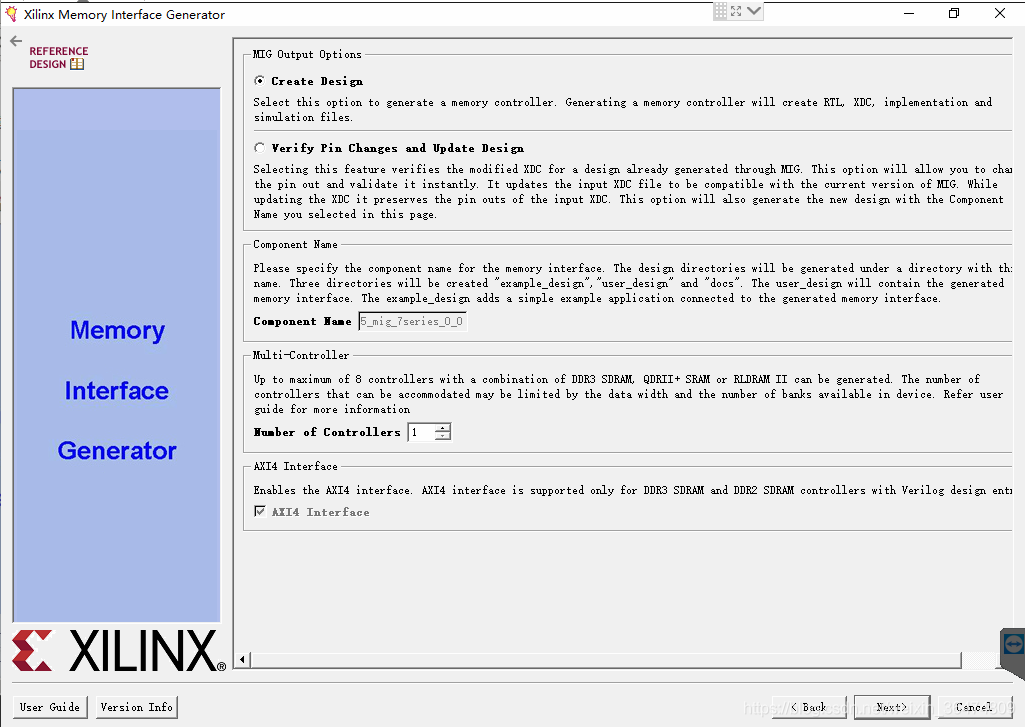

默认新建设计,1个控制器,AXI4接口

点击Next

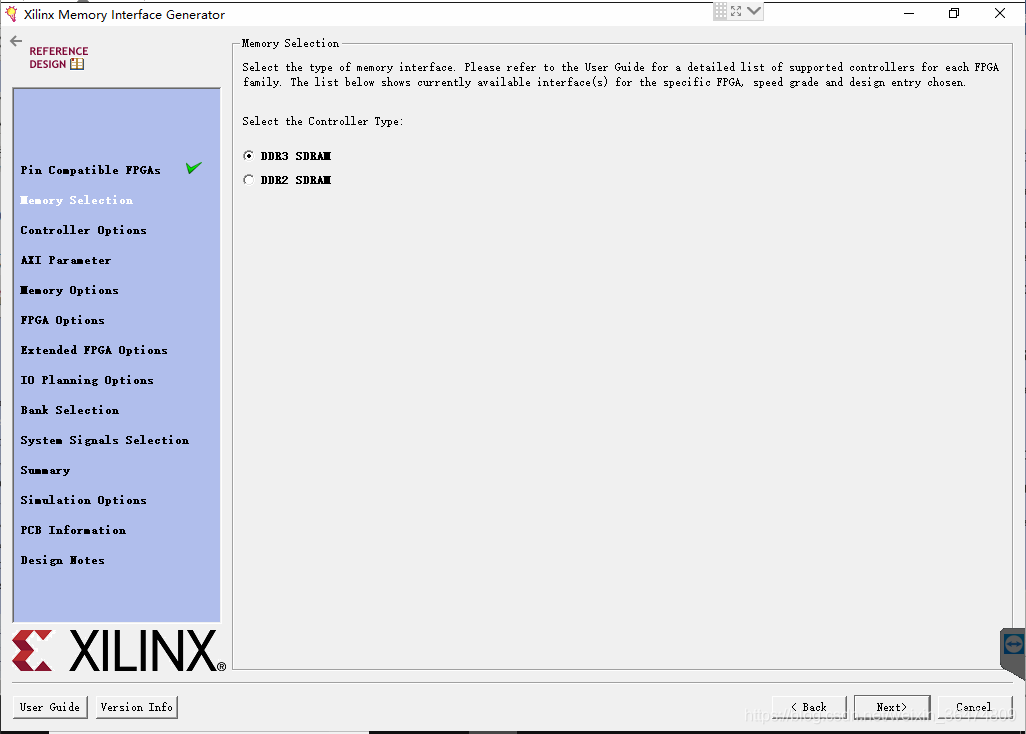

选择DDR3 SDRAM

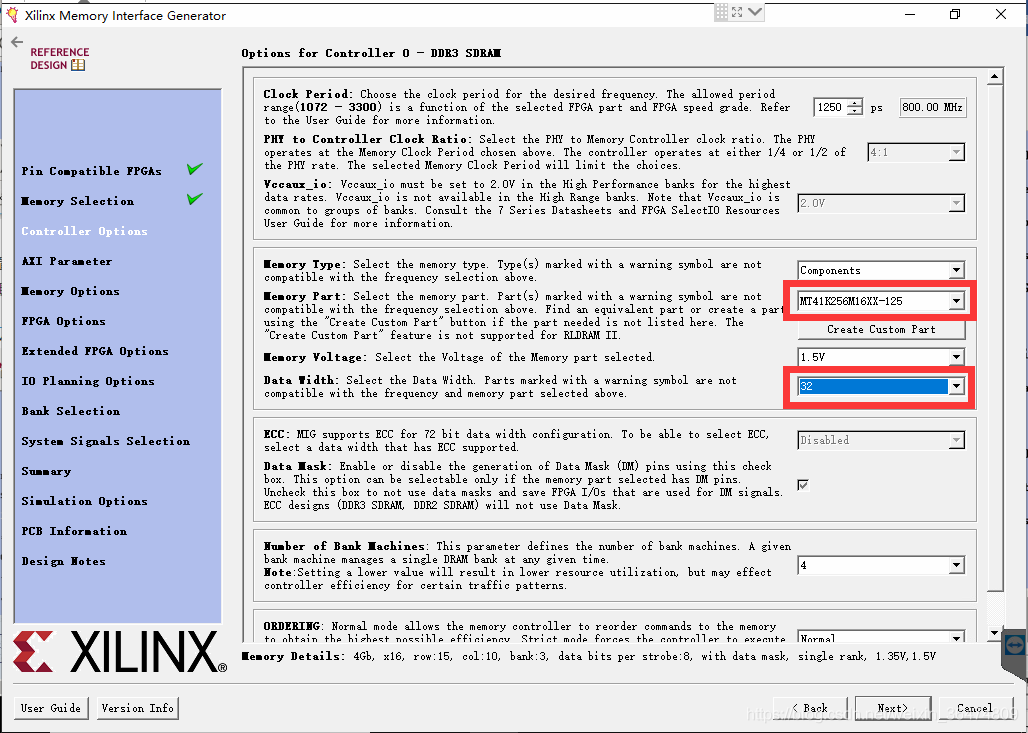

默认设置800MHz时钟,然后修改Memory Part为MT41K256M16XX-125,Data Width选择32位,其他设置默认

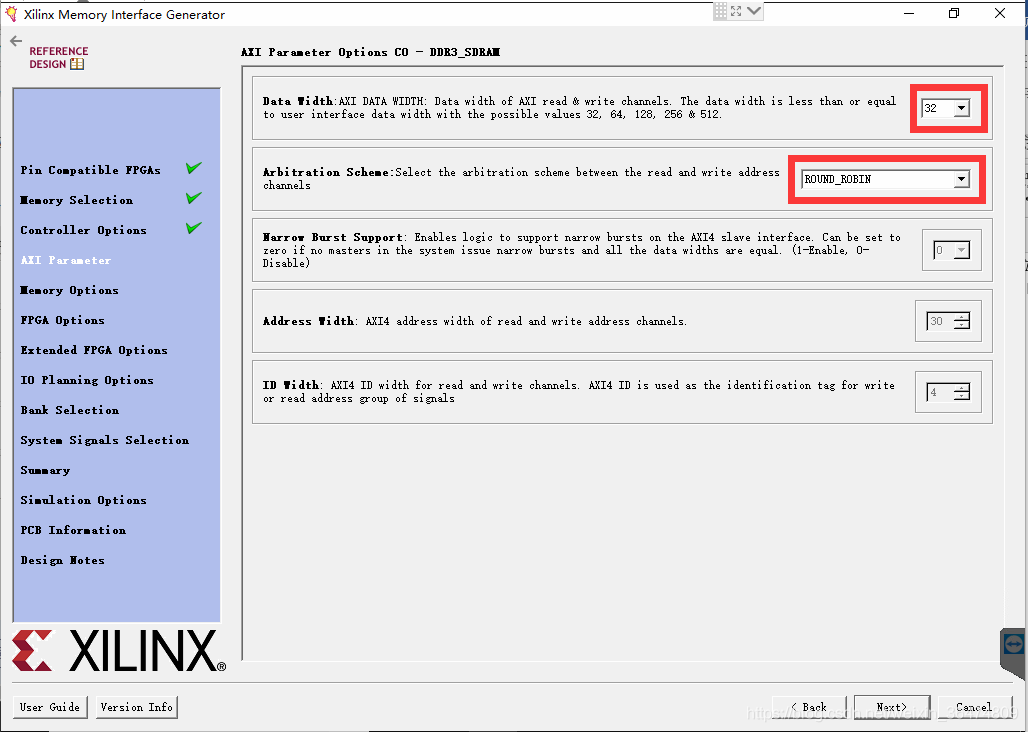

AXI的Data Width选择64位和PS的HP接口对应,或者32位和GP接口对应,地址线读写仲裁选择ROUND_ROBIN,其他默认

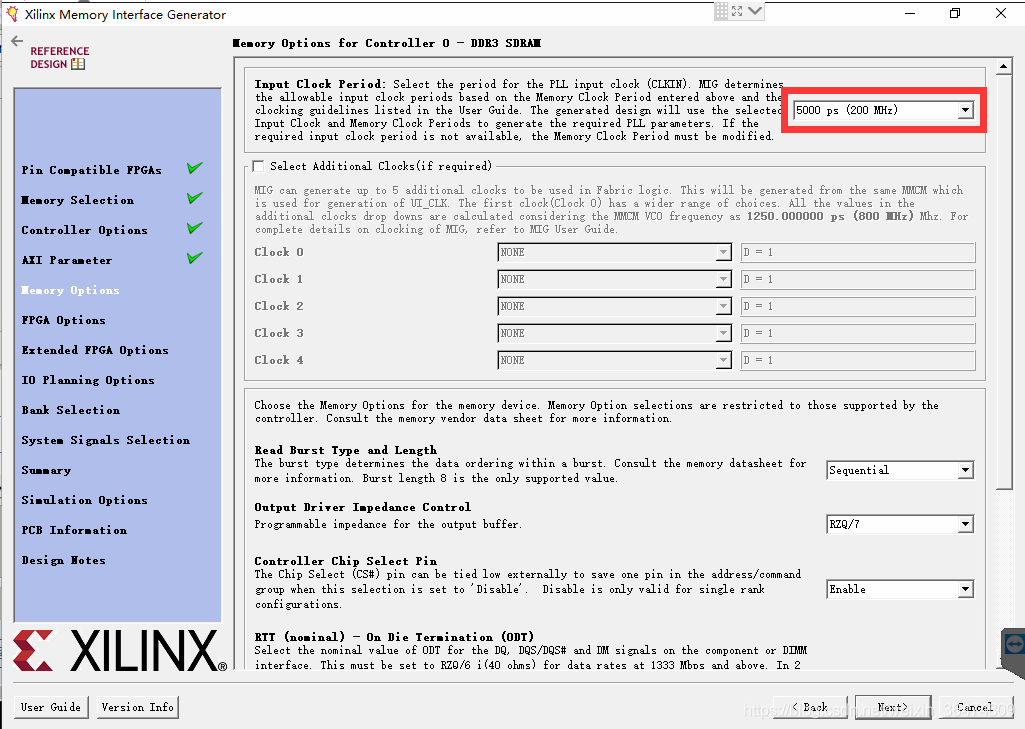

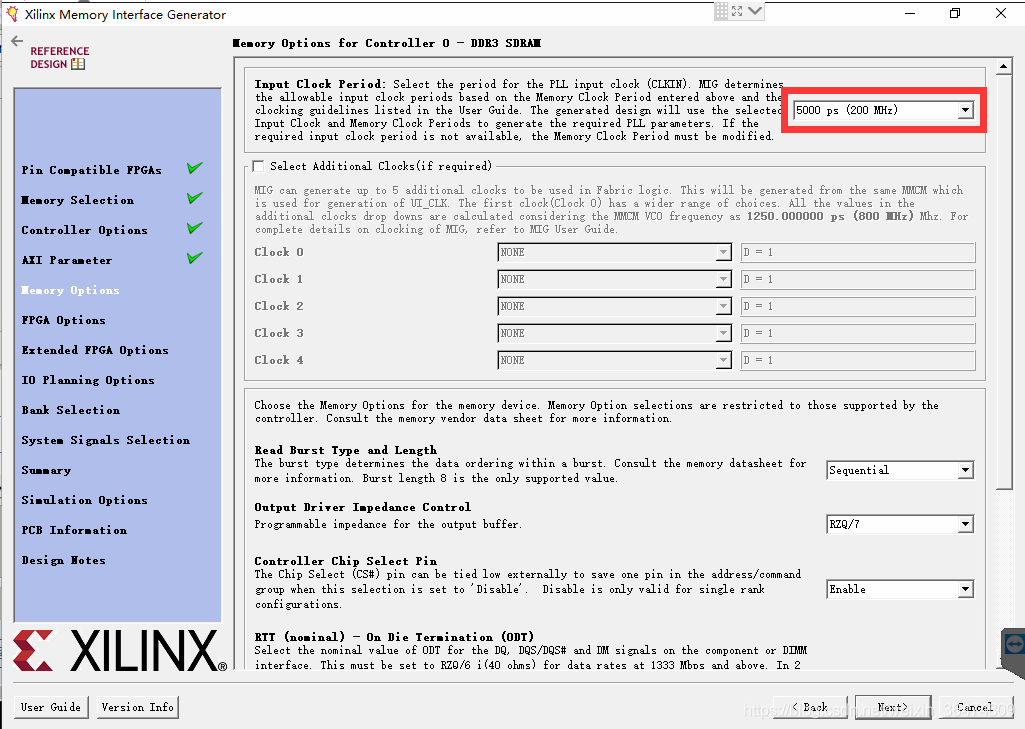

因为刚才选了800MHz和4:1,所以这里的输入时钟选择200MHz,其他默认

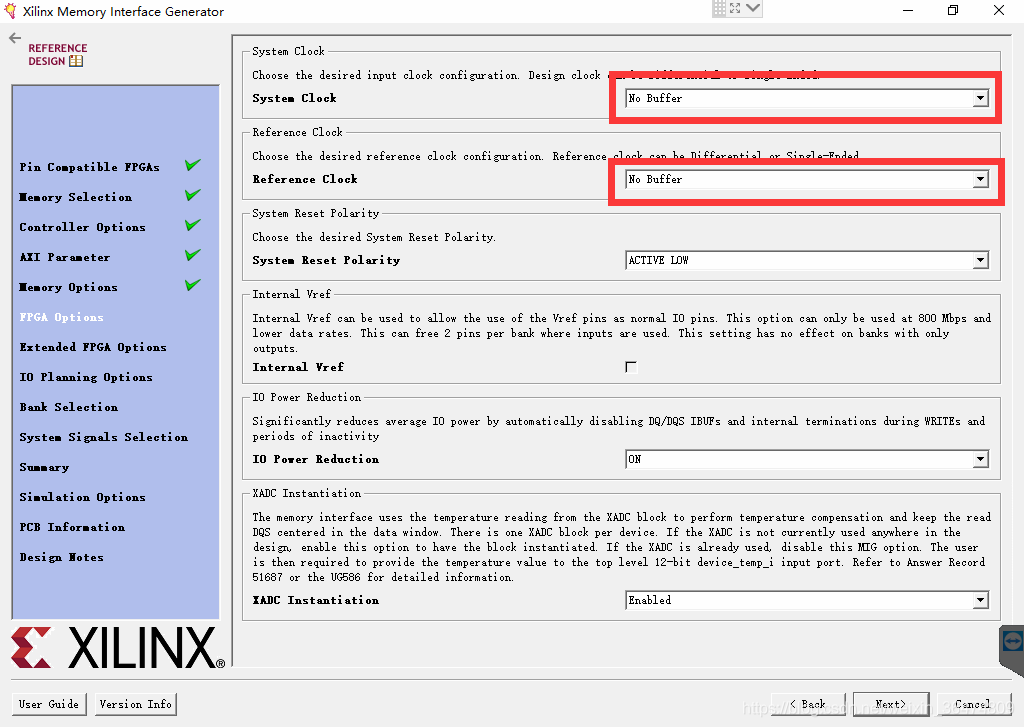

系统时钟和参考时钟来源于FPGA内部,这里选择No Buffer,其他默认

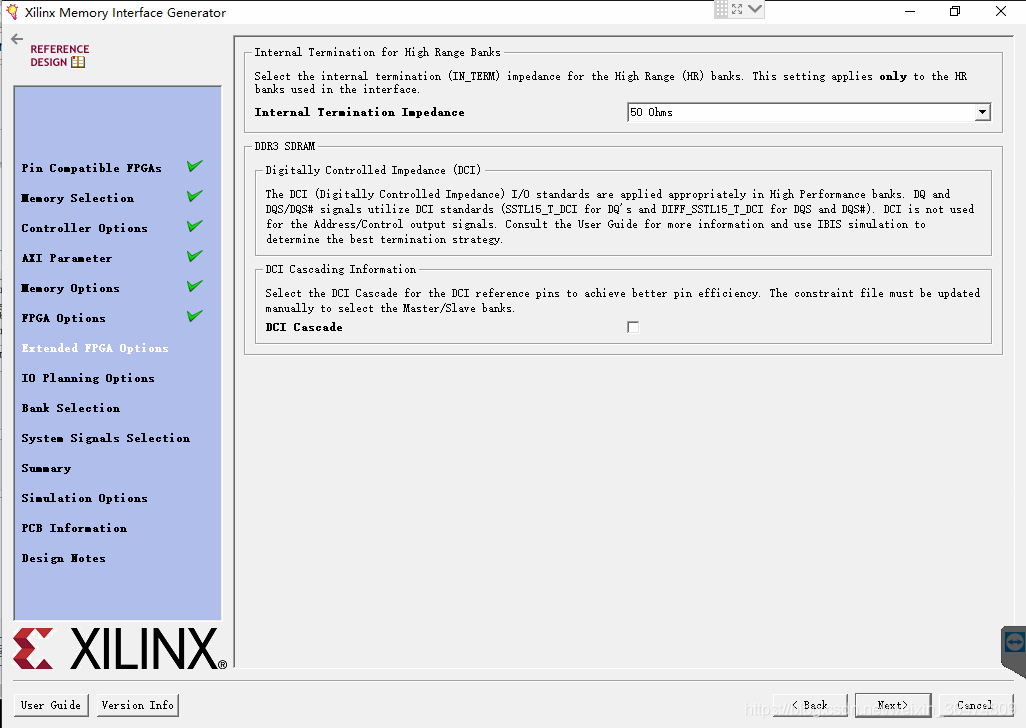

内部终端电阻选择50欧

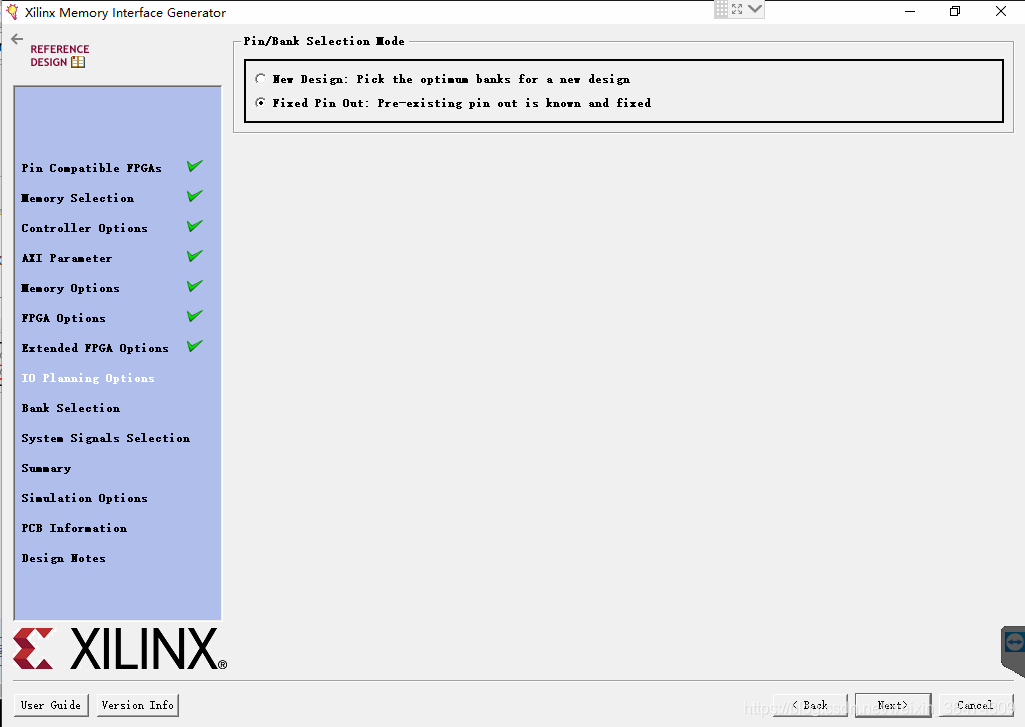

开发板已经是现成的,选择Fixed Pin Out

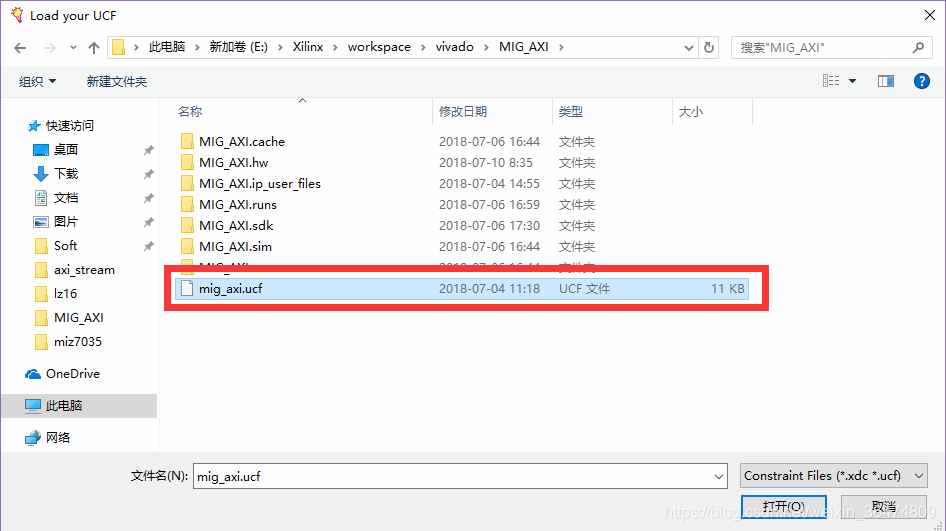

点击Read XDC/UCF

选择开发板默认的DDR管脚分布文件

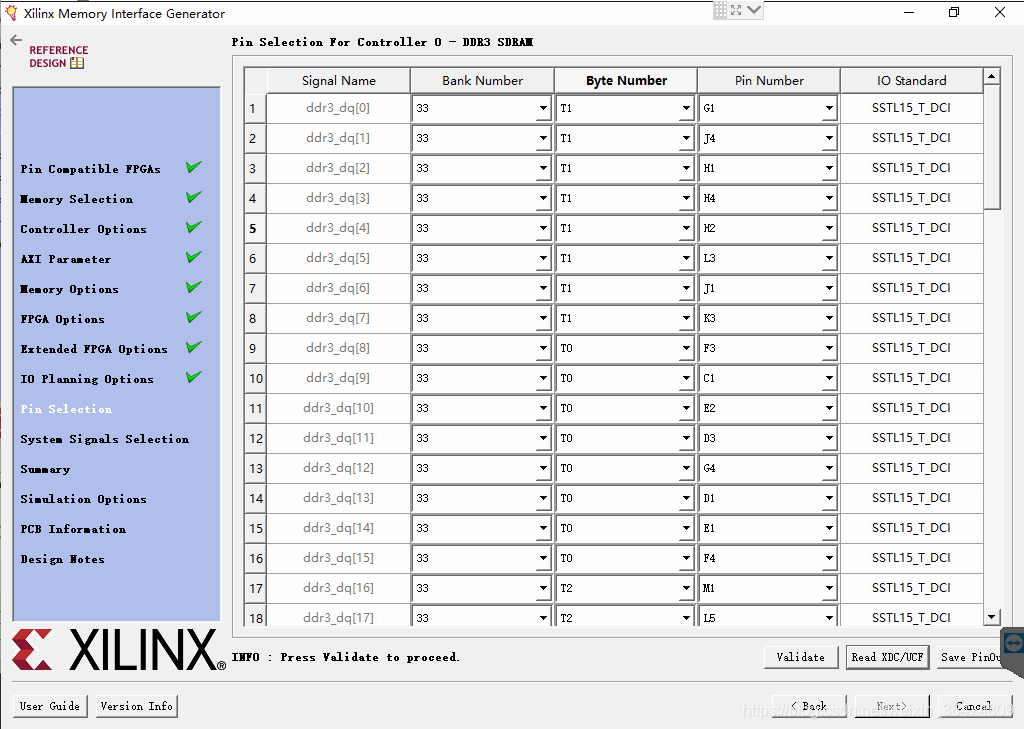

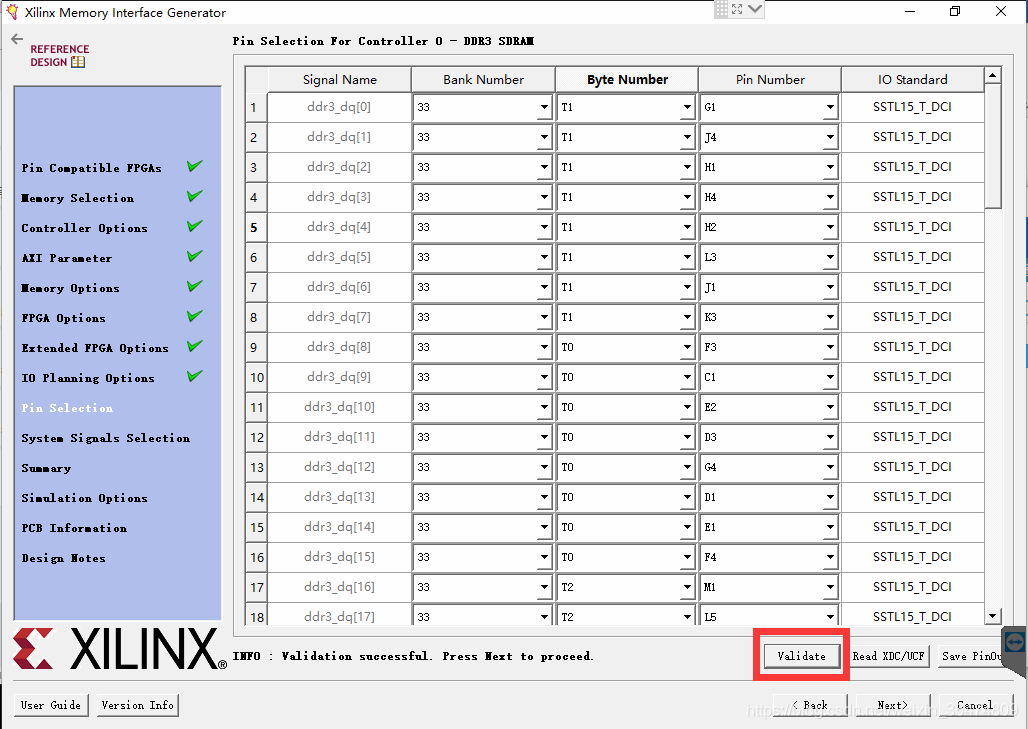

检查管脚

接下来,默认配置,一直Next;

…

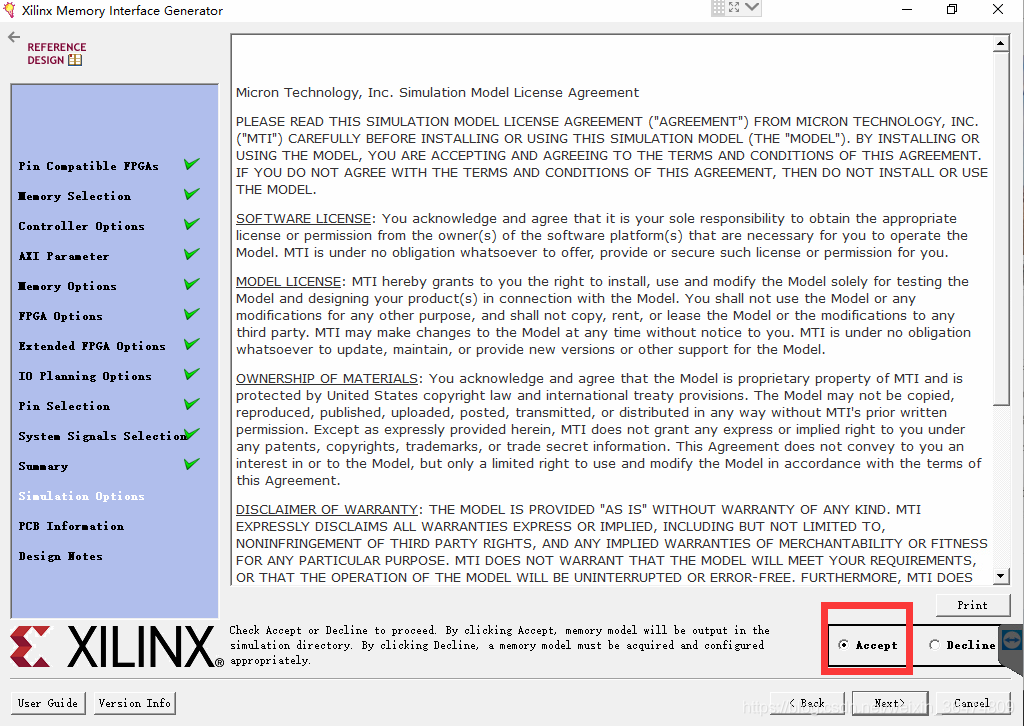

选中Accept

最后点击Generate

PS

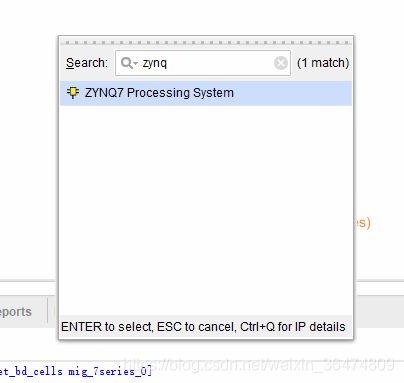

新建PS

双击PS7的IP

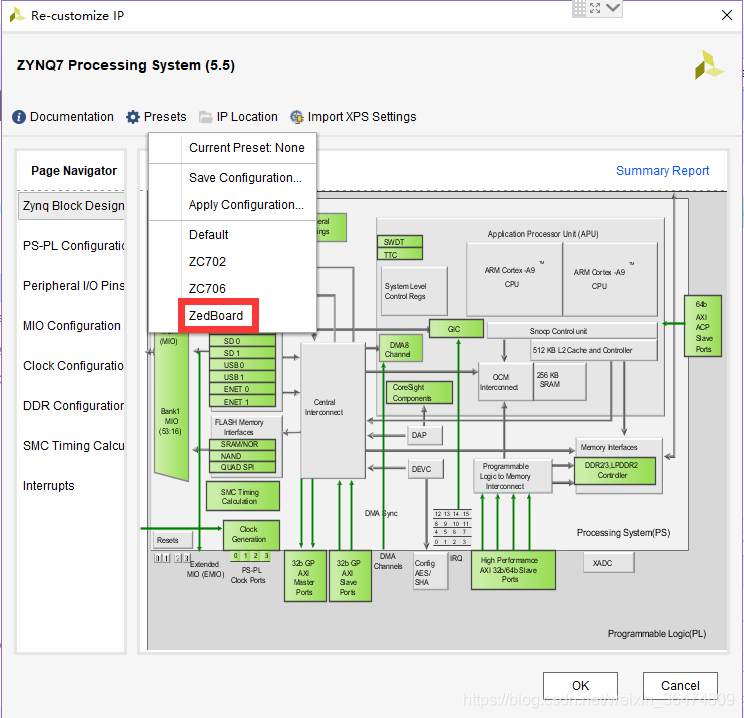

先应用一个开发板的配置(Zedboard),这样配置起来比较快

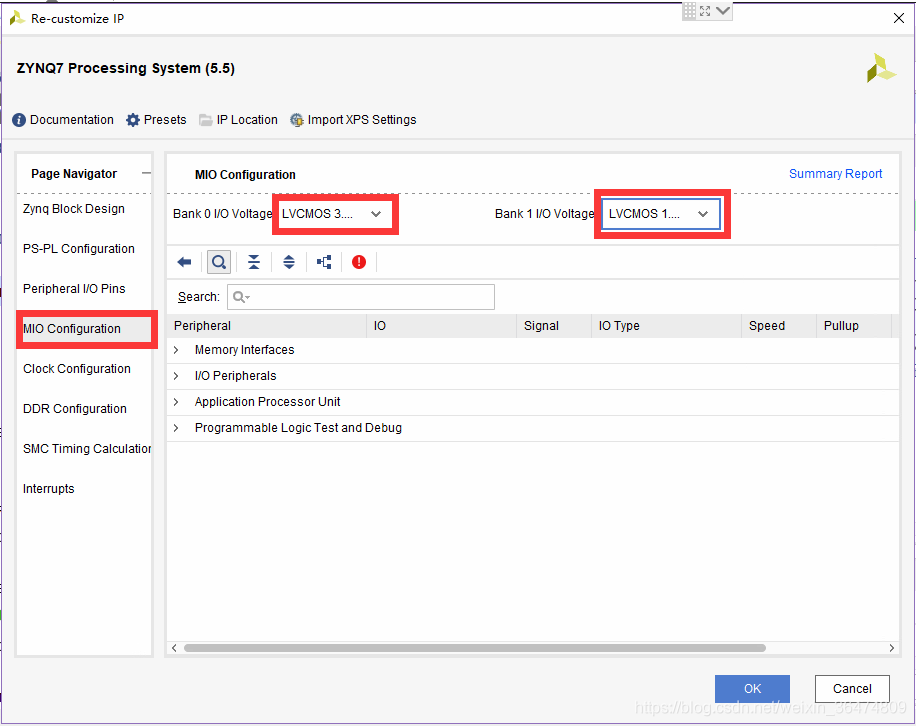

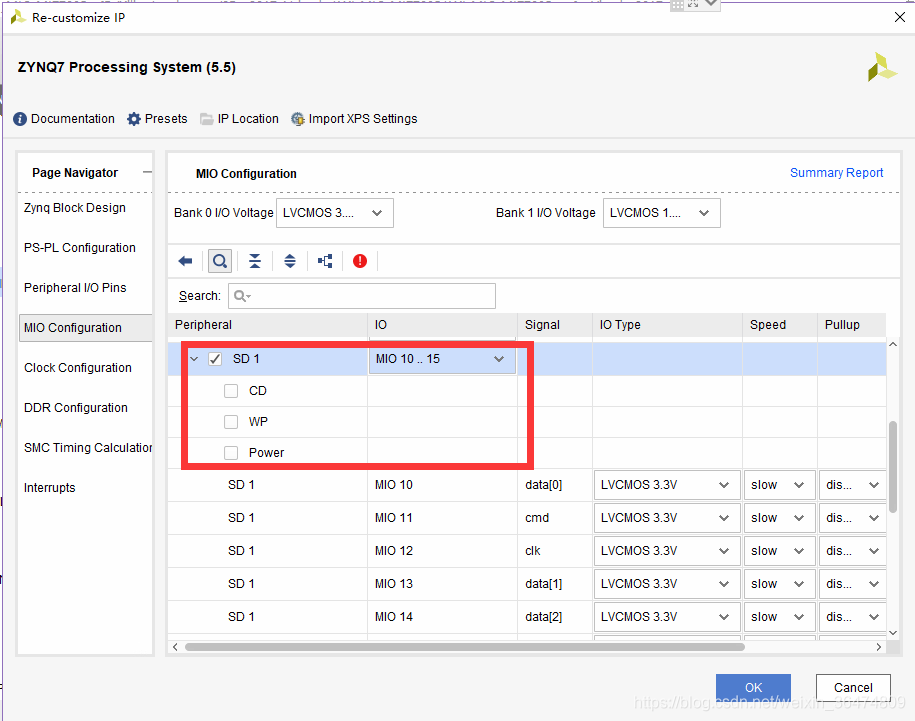

配置MIO

BANK0为3.3V,BANK1为1.8V

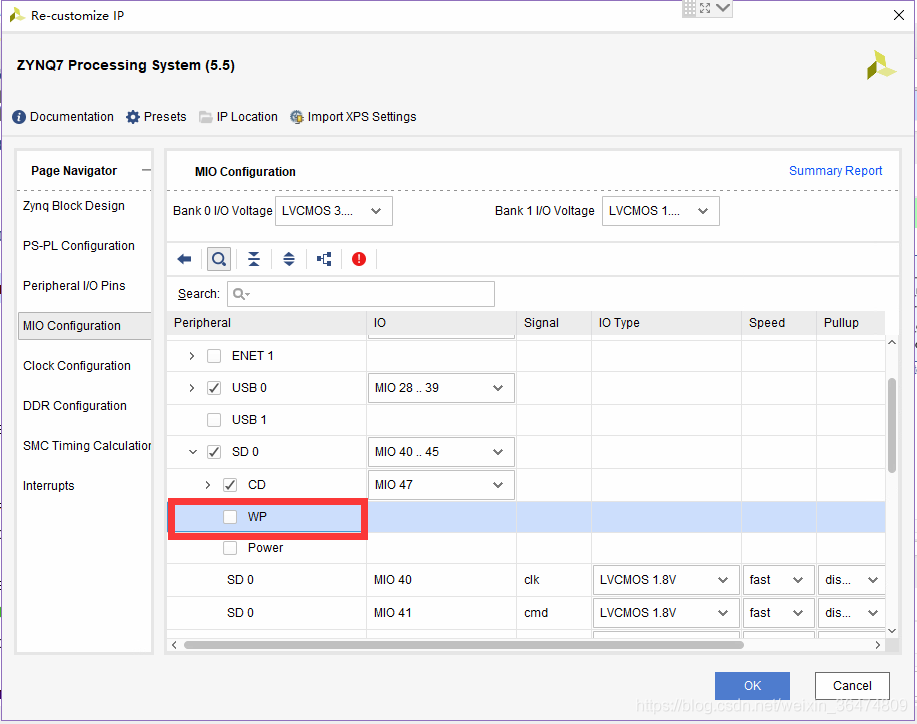

检查各个外设是否与MIZ7035的核心板匹配

SD卡,WP信号没用,去掉

eMMC需要添加SD1接口,CD和WP信号无用,不需要添加

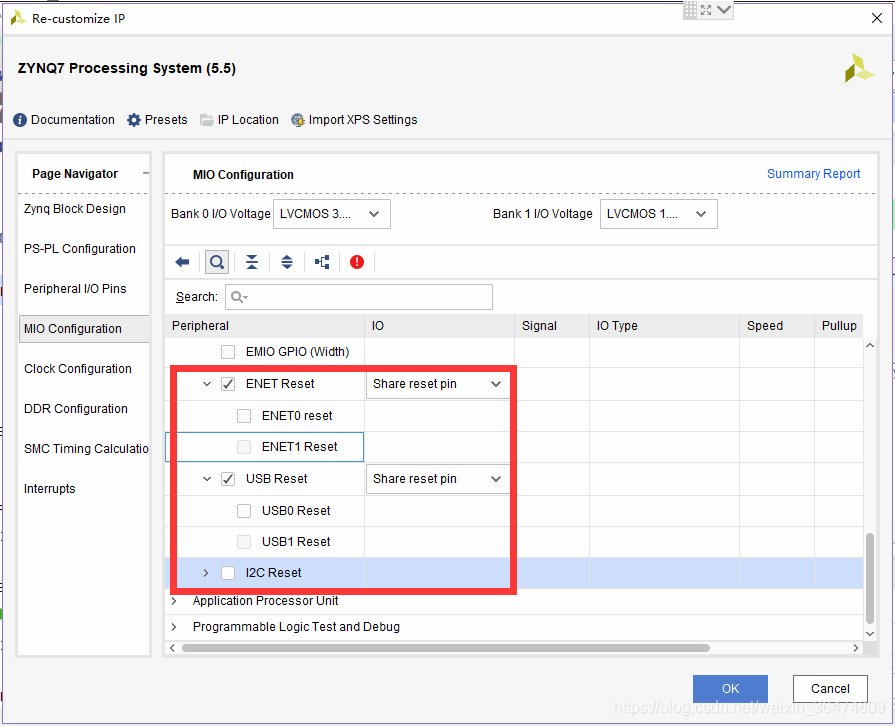

外设复位,ENET上电复位;USB复位在PL上,而这里只能选PS的MIO引脚,所以忽略;没有I2C,取消掉

其他默认

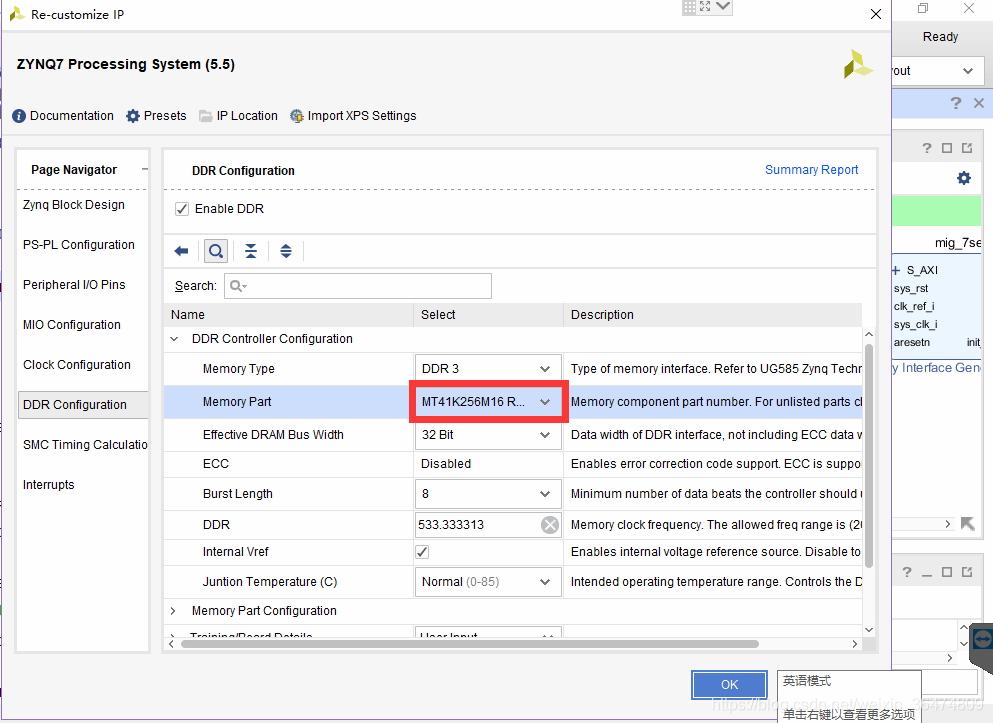

DDR配置

Memory Part选择MT41K256M16 RE-125

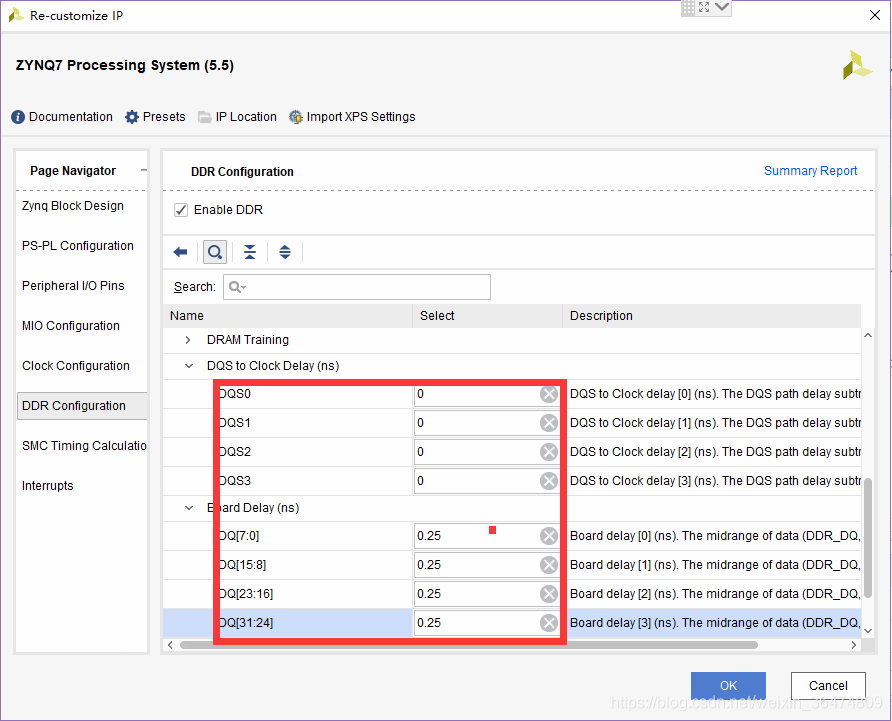

DQS to Clock Delay全部写0

Board Delay全部写0.25

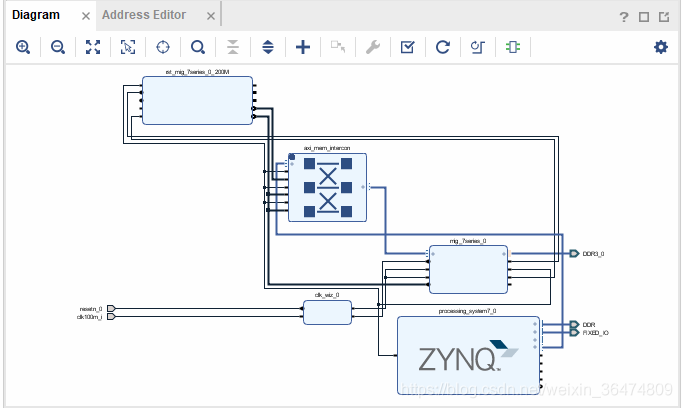

Block Design

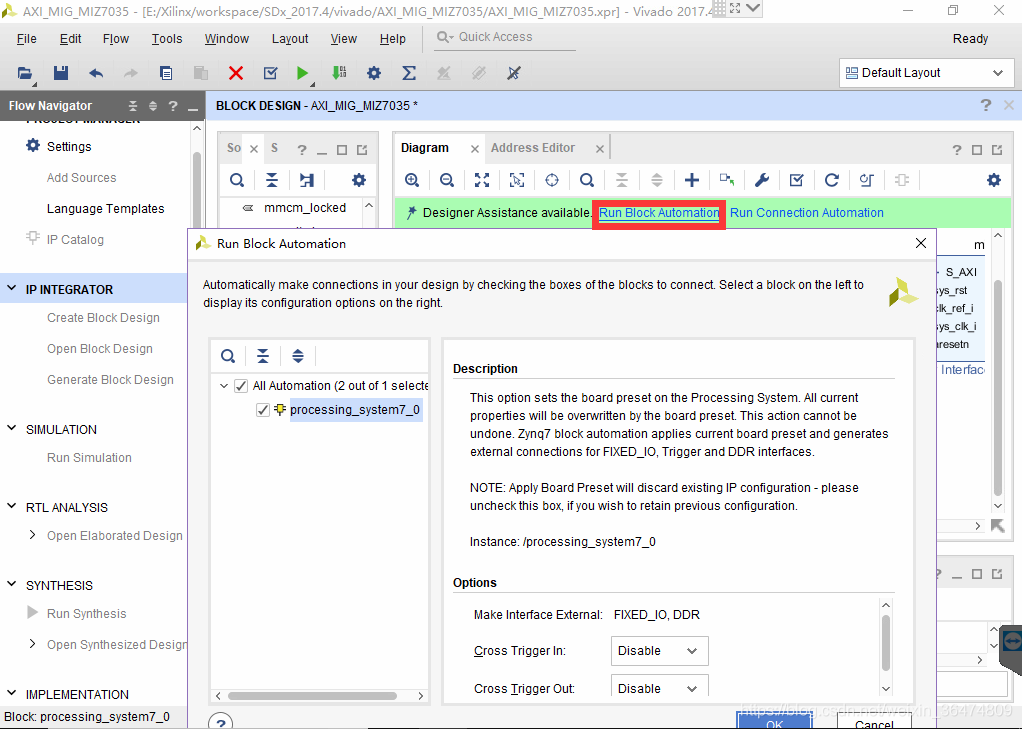

点击Run Block Automation,建立PS的接口

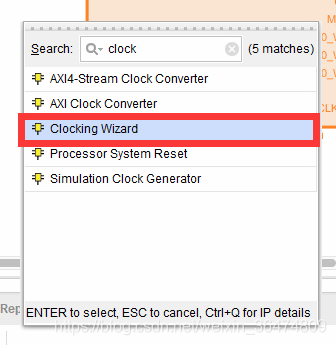

创建Clocking Wizard

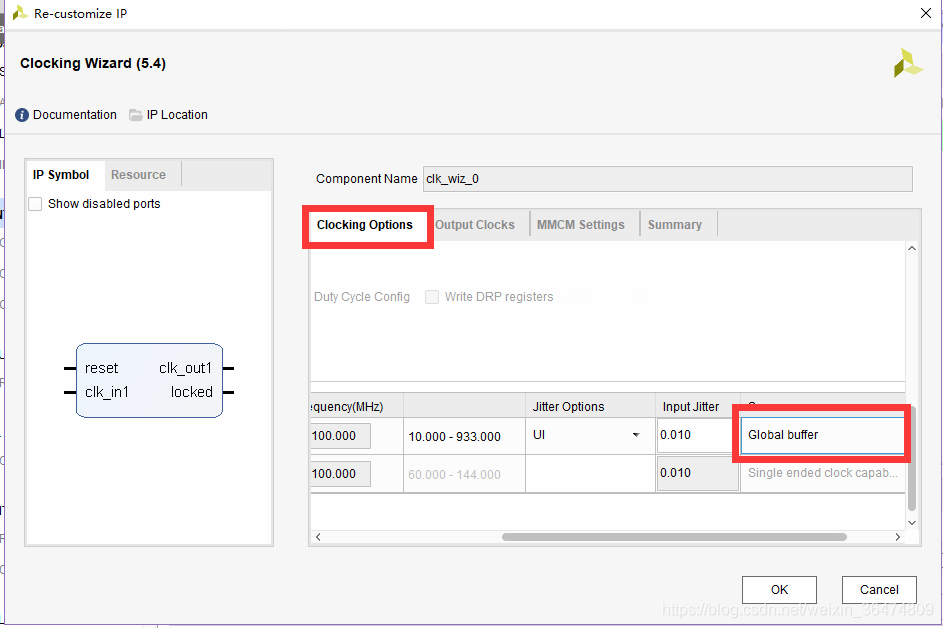

双击IP进行配置,外部GCLK的100MHz时钟,因为直接接入了时钟引脚,选择Global Buffer

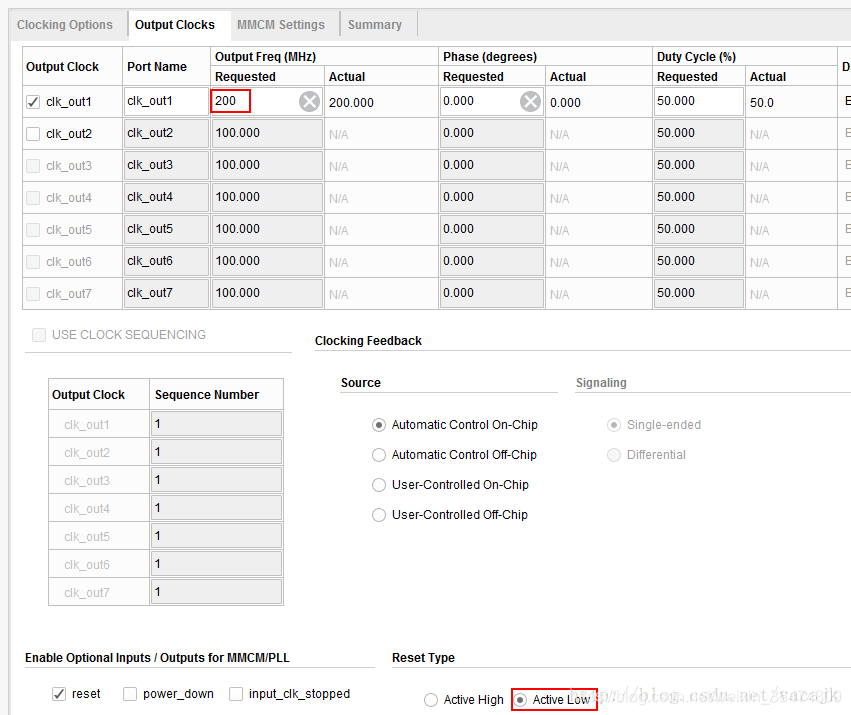

因为PL DDR3的参考时钟配置的是200MHz,这里让MMCM输出200MHz,并将Reset设置为低有效

对接口进行连接

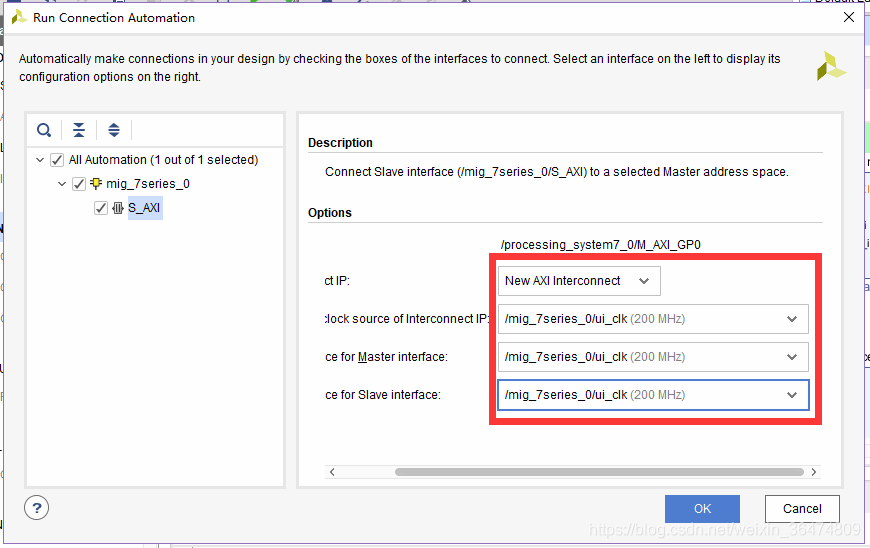

点击Run Connection Automation进行连接

时钟选择/mig_7series_0/ui_clk(200MHz)

重新进行连线

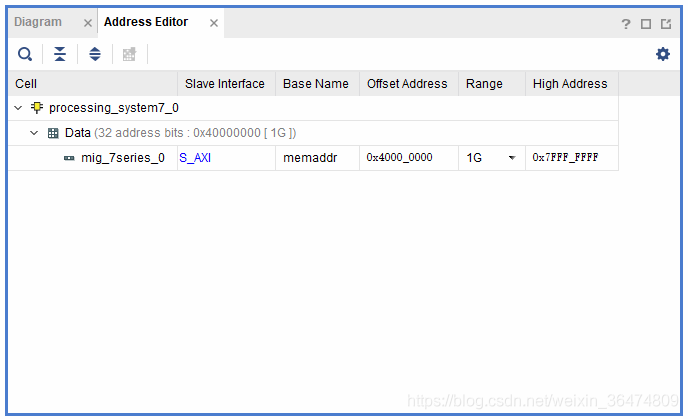

分配地址

新建IO约束文件MIZ7035_IO.xdc,内容如下

create_clock -name clk100m_i -period 10.00 [get_ports clk100m_i]

set_property VCCAUX_IO DONTCARE [get_ports clk100m_i]

set_property IOSTANDARD SSTL15 [get_ports clk100m_i]

set_property PACKAGE_PIN C8 [get_ports clk100m_i]

set_property PACKAGE_PIN H7 [get_ports rst_key]

set_property IOSTANDARD SSTL15 [get_ports rst_key]

set_property PACKAGE_PIN K10 [get_ports init_calib_complete]

set_property IOSTANDARD SSTL15 [get_ports init_calib_complete]

右键点击BD,Create HDL Wrapper,Generate Output Products

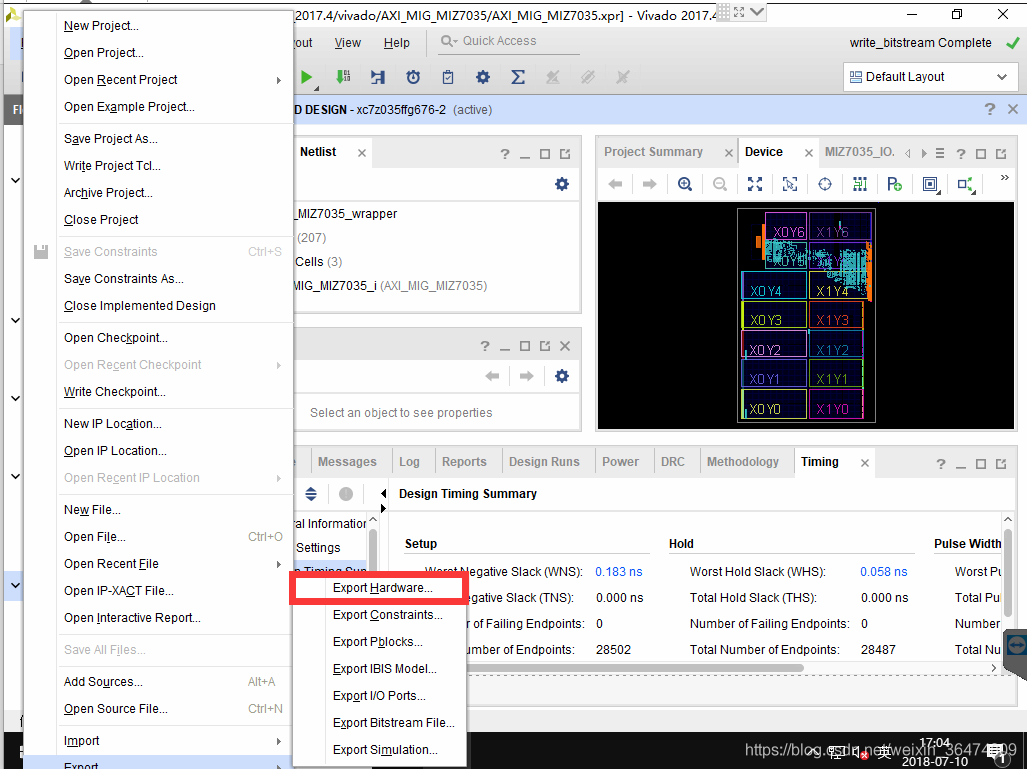

点击Generate Bitstream完成综合,生成bit文件

SDK

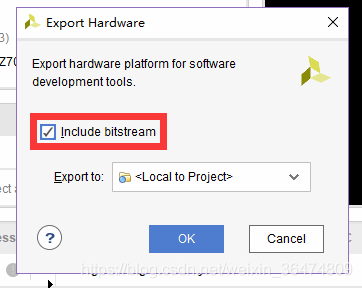

导出Hardware

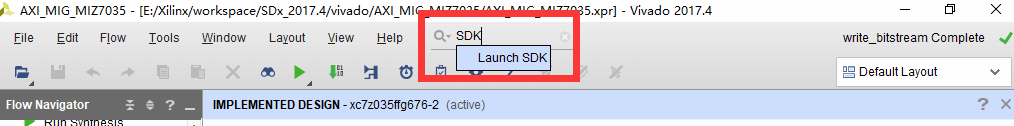

启动SDK

启动界面

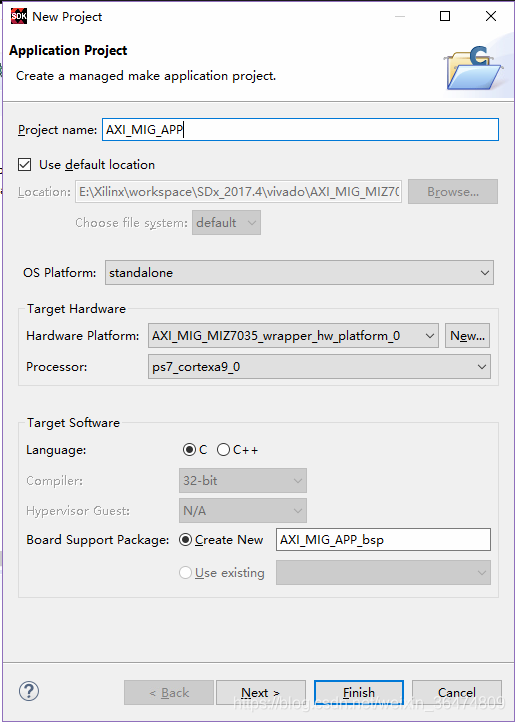

创建Application工程

点击Next

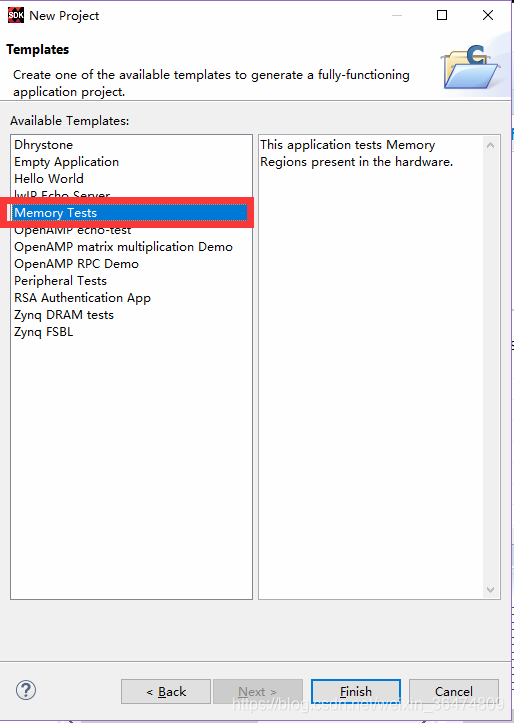

选择Memory Test

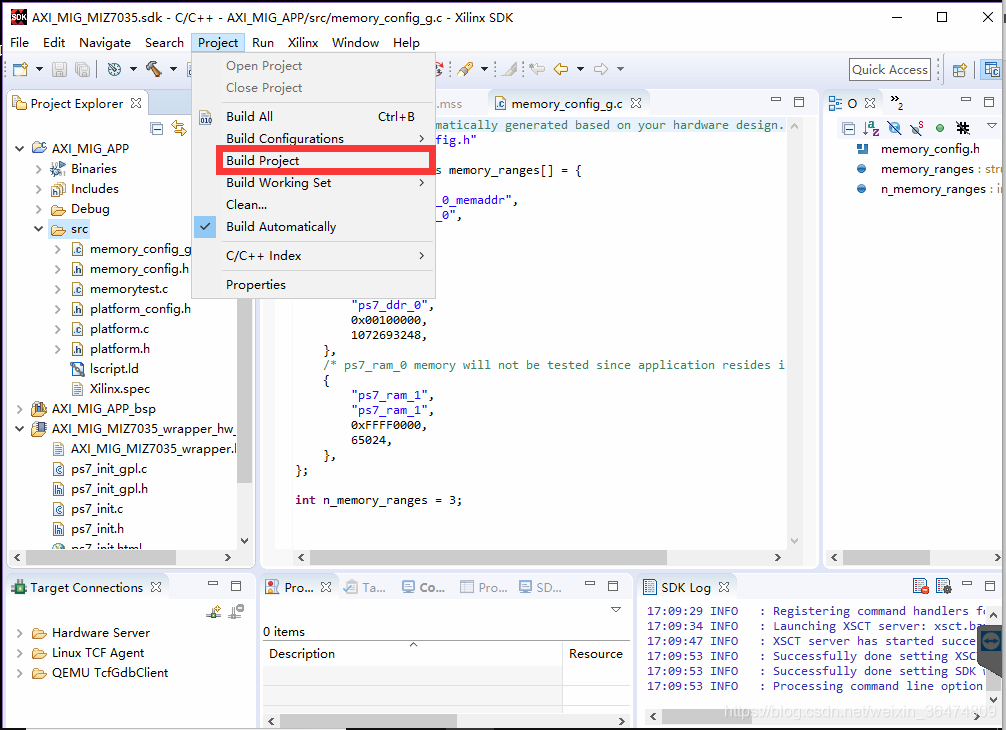

编译工程

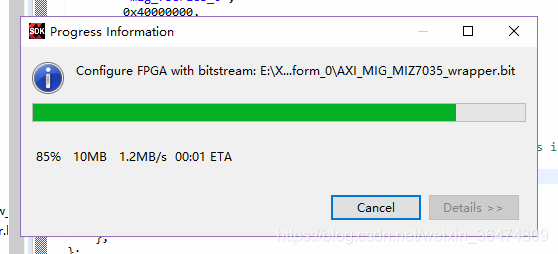

烧写FPGA

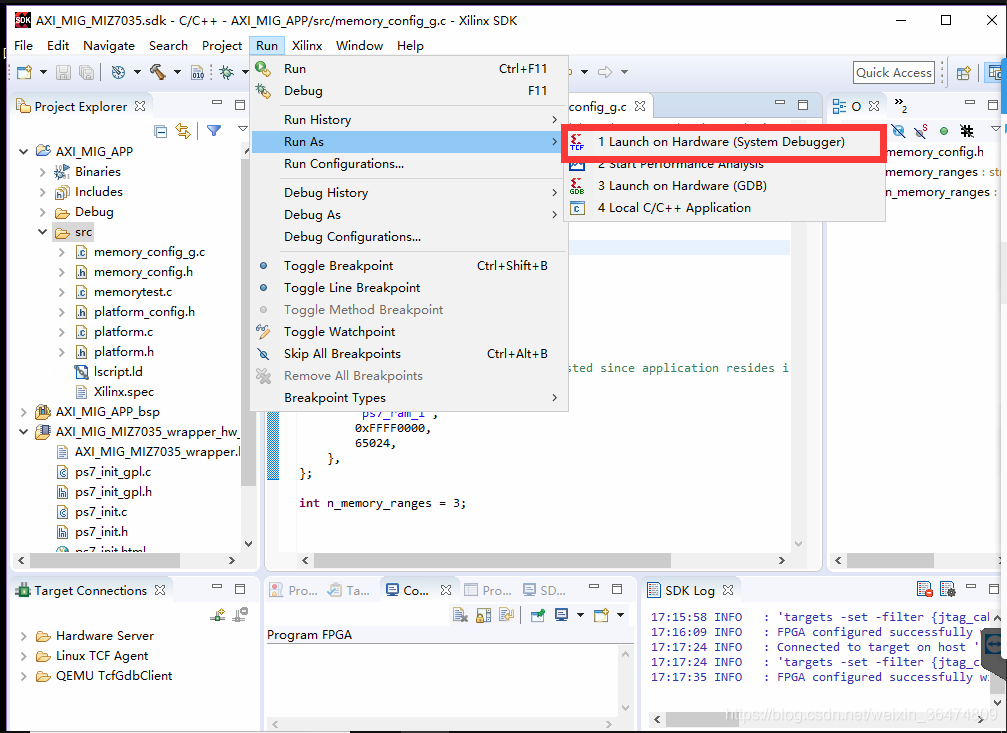

运行Application

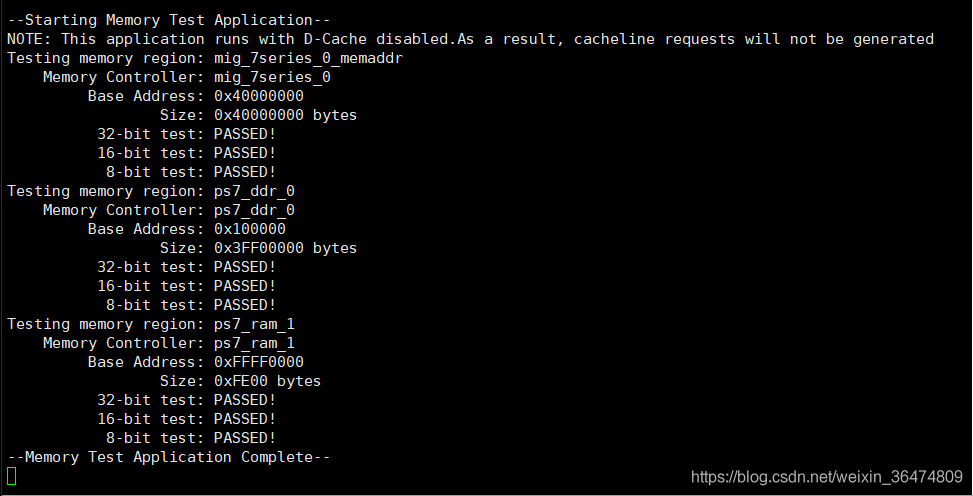

连接串口终端,打印如下信息