LDO的探索之旅

1.线性稳压器

1.1 工作原理

LDO是线性稳压器的一种,先来介绍线性稳压器。

线性稳压器,顾名思义,开关管工作在线性区的输出电压稳定的电路。与开关电源是相对应的,开关电源的开关管工作在开关状态。

以下面的线性稳压器原理图为例来说明工作原理。

工作原理:若输入电压增加,输出电压增加,Vbe减小,ib减小,Uce增加,Uo减小,从而维持输出电压稳定。若负载增加,输出电压增加,同上分析。

三极管和稳压管之间的电阻作用是限制流过稳压管的电流,避免稳压管过电流击穿。

线性稳压器的特点:

- 开关管工作在线性区 ,噪声问题小,也没有电压电流交叉损耗

- 导通损耗大

- 体积小,后级不需要电感

- 降压电路

2. LDO

LDO:Low dropout 低压差稳压器

LDO是线性稳压器的一种,只不过压差比较小,一般把压差小于200mV的线性稳压器叫LDO.

2.1 LDO分类

LDO的最大优点是实现输出很好的跟随输入.

LDO分类:主要有NPN LDO(严格讲叫NPN线性调节器),PNP LDO,NMOS LDO,PMOS LDO

2.1.1 NPN LDO

工作原理:当输出分压低于Vref时,PNP饱和导通,而Q2的NPN由于Vc>Vb所以放大状态,同理Q1 NPN也成放大状态。当分压高于Vref时,Q1导通程度减小,输出得不到足够的电压供给,电压降低。

此电路有如下特点:

- PNP给NPN提供偏置

- 工作电流小

- dropout电压2Vbe(0.7+0.7)+Vcesat(0.3V) ,所以输入输出电压差大

- 静态电流随负载电流的变化而变化,主要是影响NPN,PNP的导通程度

2.1.2 PNP LDO

工作原理:将NPN换为PNP,其他原理类似。

- PNP比NPN drop out电压低

- 饱和导通电流大,输入电流大

- PNP导通压降小

- 负载调整率差,因为是饱和导通

- 需要加输出电容,因为阻抗比较大,这会增加零极点。

2.1.3 NMOS LDO

将NPN换为NMOS,即变成NMOS LDO.

特点如下:

- 需偏置电压以上拉 N-FET

- 接地引脚电流不随输出负载电流而变化;

- 不需要任何的输出电容器(但为了动态响应更好还是使用一个)

2.1.4 PMOS LDO

将NMOS换为PMOS,即为PMOS LDO。

特点如下:

- 要求输出电压高于传输元件的 VGS 需求;

- 要求谨慎地选择输出电容数值和 ESR 额定值;

- 为了实现相似的 RDS(on) 性能, PMOS 晶体管所需的晶片面积将大于 NMOS 晶体管;

- 较大的晶片面积将影响定价,并有可能对性能产生影响

2.2 LDO 相关参数

由于最近要进心LDO芯片测试,以TI的技术文档为参考,进行详细剖析。

1.Dropout压差

压差电压是保持输出稳定的输入输出最小压差值。压差值越小,性能越好。

dropout的变化跟器件本身有关。

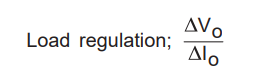

2.负载调整率

负载变化,输出电压变化。变化的电压除以变化的电流即为负载调整率。负载调整率越小,输出电压受负载变化的影响越小。从0到满载变化最worse。

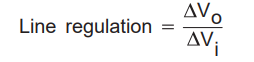

3.线性调整率

输入变化,输出电压变化。变化的输出电压除以变化的输入电压即为输入调整率。线性调整率越小,输出电压受输入电压变化的影响越小。

4.效率

输入功率包括负载和静态功率

一般静态电流Iq远小于Iload,所以其效率一般为Vo/Vin,所以输入输出电压差越大,损耗越小,效率越高,跟负载关系不大。

5.静态电流

LDO无载时维持稳压器工作电流,主要是流经GND的电流。静态工作电流为输入电流与输出电流之差。

静态电流来源于各种偏置电流如误差放大器电流 ,采样电阻电流,门极驱动电流这些都是对功率输出没有意义的,只会降低效率。

BJT型LDO的静态电流跟负载有关,负载越大,静态电流越大,因为三极管是电流驱动型,而mos型的LDO静态电流跟负载几乎没有关系,因为是电压控制器。

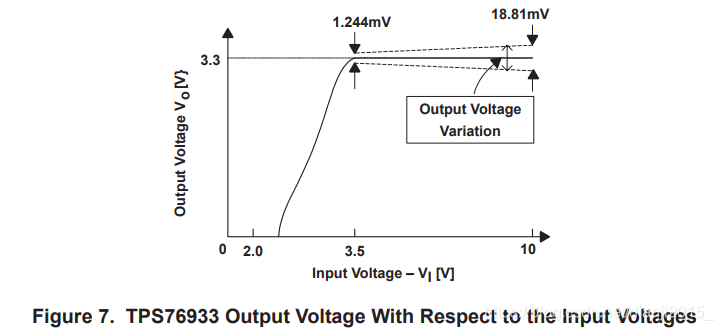

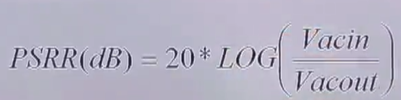

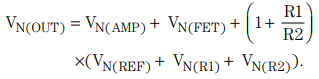

6.PSRR

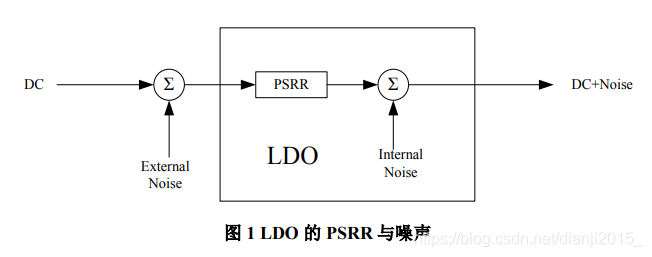

PSRR(power supply rejection ratio)电源抑制比.

表征稳压器对输入电压纹波噪声的抑制。是输入与输出交流分量的比值,越大,抑制噪声效果越好,受负载,pcb布局,频率电压等的影响

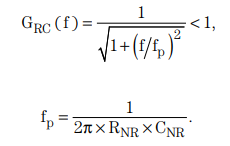

噪声来源于带隙(band gap)参考电压源和误差放大器,加一个低通滤波器可减小噪声。

PSRR的测试可以把LDO当作滤波器,注入纹波不能太小,否则精度不高,输入电容会衰减高频纹波,需减小输入电容.

测试方法:在LDO的输入电压中加入一定频率和峰值的交流电压,测量LDO中峰峰值,

7.精度

输出电压与实际电压的差。

8.噪声

LDO噪声非常小,一般只有几百个uV。可以在输出加上0.01uF和4.7uF的电容滤除。

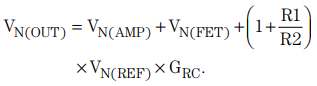

LDO噪声来源:

LDO 的噪声分为 LDO 内部的噪声和 LDO 外部的噪声。LDO 内部的噪声来自于内部电路的带隙基准源,放大器以及晶体管。LDO 外部的噪声来自于输入,其中带隙基准源产生的噪声为主要噪声。

LDO 噪声抑制方法:

- 降低误差放大器的带宽,但是降低带宽会使 LDO 的动态性能

降低。 - 在带隙基准源和误差放大器之间加低通滤波。

- 在反馈电阻 R1 上增加前馈电容CFF。CFF 越大,输出噪声就越小。频率越高,输出噪声越小。一般选择几十pF,按厂家的手册来。

2021.5.18

PS:最近好几次都碰到芯片测试时,LDO有纹波或者振荡的情况。并且有稳定的频率,但是LDO又不是DCDC,所以纹波到底来自于哪里呢?

1)来自参考电压源

为了减小参考电压上的噪声,有的LDO会加入一路 noise-reduction (NR) 引脚。如下图所示。

加入RC后,噪声幅值减小。电容的值一般为pF级。

2)来自反馈环路各种噪声

2.3 LDO 设计

2.3.1 LDO的设计要点

- 确定dropout电压

- 选择合适的拓扑 根据PSRR,静态功耗等设计参数

- 确定封装以满足散热

需要避免Vin<Vo+Vdrop,否则会产生如下影响 - 动态性能差

- 负载调整率差

3.环路补偿

3.0 LDO的小信号模型

以PNP型LDO为例说明。下面是PNP LDO 等效电路图。

LDO的传递函数可以分为三个部分考虑:

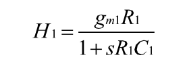

1)误差放大器带来的传递函数

里面的组成部分主要是运放,将其当作单级跨导运放来分析。

传递函数为

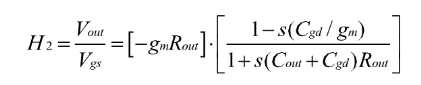

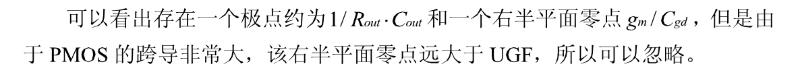

2)驱动电路带来的传递函数

驱动管的小信号模型如下:

传递函数为

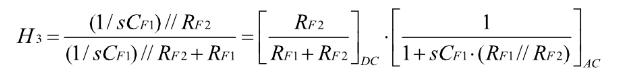

3)反馈带来的传递函数

传递函数为

总结如下

Z1,P3比较大,可以忽略。

P1中C1为运放输出点的等效电容,P2中等效电阻为PMOS管电阻,反馈电阻和负载电阻的并联。负载电阻变化时,输出极点就会变化。

总的来说,LDO自身有两个极点,一个是误差放大器输出电阻电容带来的,一个是输出电阻电容带来的。

3.1 NPN调节器补偿

NPN调节器的输出阻抗很小,所以极点频率高。

- 环路增加一个主极点补偿

P1是环路中加补偿电容产生的,主极点一般为100Hz - P2为功率极点,电路固有

- 相位裕量比较大

3.2 PNP LDO补偿

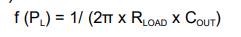

1.PNP需要加输出电容,所以会与负载形成一个极点。极点频率如下:

2.内部补偿极点为P1

3.PNP驱动带来的功率极点为P2

4.为了有足够的相位裕量需要增加零点,

零点是电容ESR带来的,零点频率为:

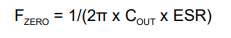

从上面可知输出电容及其ESR的选择极为重要,会影响PNP LDO的稳定性。

典型的ESR范围如下:

太大不稳定,一般>10Ω。

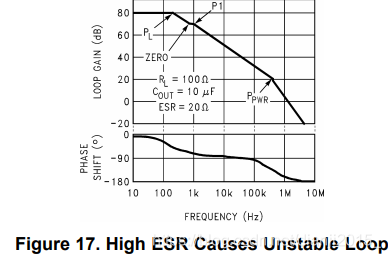

假设ESR太大,导致零点频率为P1或者PL,相当于没改变,相位裕量还是很小。如下图所示:

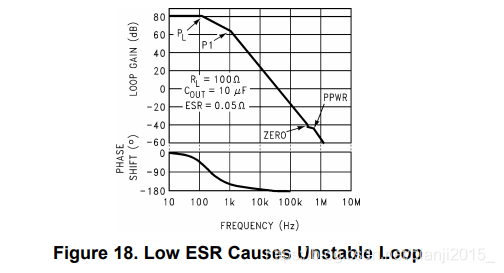

太小 ,也不稳定

假设ESR太小,一般<50mΩ,零点频率到达功率极点,那对穿越频率的相位裕量一点帮助都没有,所以也不稳定。

对于输出电容的选择,一般选择4.7uF的钽电容,ESR只有1Ω左右。

3.3 LDO环路测试

有两种方法:一是变压器注入,二是高精度注入

变压器注入如下:

注入纹波测试时,不能太小,否则测不准,不能采用大的输入电容,否则衰减高频纹波。

参考资料:

《Understanding the Terms and Definitions of LDO Voltage Regulators》----TI

《AN-1148 Linear Regulators: Theory of Operation and

Compensation》----TI

《Understanding noise in linear regulators》-TI