makefile支持两种方式给变量赋值:

变量名=...

变量名:=...

两者的区别在于,“:=”的赋值立刻发生,而“=”的赋值只在调用“=”左边的变量时才发生。看下面的makefile例子:

CC1 = gcc

CC2 = g++

CMD1 = ${CC1}

CMD2 := ${CC2}

CC1 = g++

CC2 = gcc

#add @ before echo.

#see https://stackoverflow.com/questions/3707517/make-file-echo-displaying-path-string

all:

@echo ${CMD1}

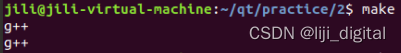

@echo ${CMD2}效果:

按理说,尽管在CMD1和CMD2赋值后,CC1和CC2的取值发生了交换,但是CMD1 和CMD2不应受影响才对。但是,由于CMD1采用=赋值,所以CMD1后面的

CC1=g++还是起了作用。

在调用@echo ${CMD1}时,其实指令首先展开为

@echo ${CC1}然后读取CC1当时的取值,再次展开:

@echo g++反过来说,CMD2采用 := 来取值,所以CMD2的取值在调用 := 时就确定了,与后来CC2的变化无关。

版权声明:本文为liji_digital原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。