1. Single Root I/O Virtualization (SR-IOV)特性和限制

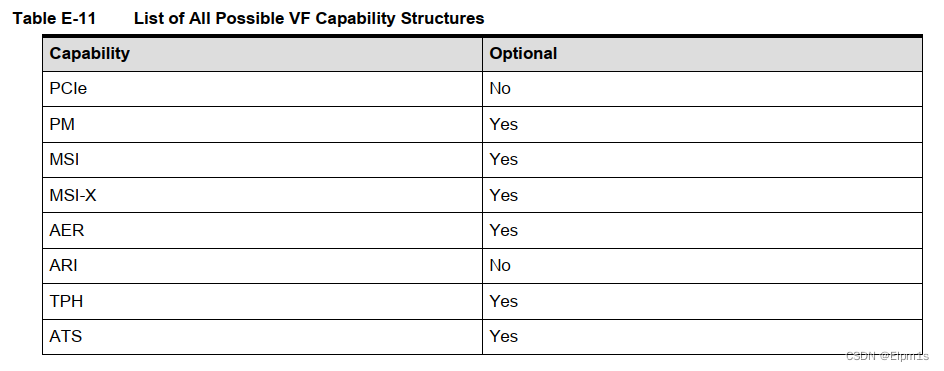

每个VF支持:

- Error Handling

- PCI Express Capability

- ARI Capability

- AER Capability (optional)

- PM Capability (optional)

- MSI Capability (optional)

- MSI-X Capability (optional)

当SRIOV使能时,必须使能MSI或MSI- x Capability

作为PCIe控制器支持:

- 最大32个PFs (CX_NFUNC)

- 最小2个内部VFs (CX_NVFUNC =SUM {CX_MAX_VF_n})

- 最大256个内部VFs (CX_NVFUNC =SUM {CX_MAX_VF_n})

- 当需要超过256个VFs 时,通过可扩展IOV接口(CX_EXTENSIBLE_VFUNC =1)提供外部vf。在这个版本中,不能同时拥有内部和外部vf。

- PFs上VFs的可编程分配

- 支持两组VF Stride,在PF0 .SR-IOV能力结构中,主机软件通过控制寄存器的ARI Capable Hierarchy bit进行选择

- VF Stride必须是2的幂(1, 2, 4, 8, 16, …)

- VF Offset可以是>= 1的任何数字

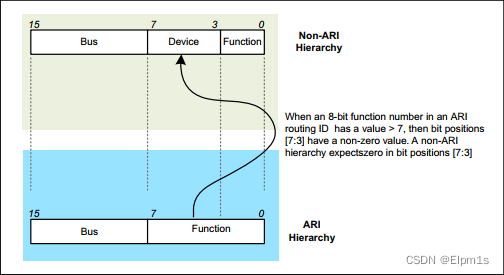

- 当PFs数量大于8个时,routing ID TLP报头字段格式为ARI

- 支持TLP处理提示

- 控制器将以非零设备号为目标的CFG请求作为不受支持的请求处理

- DMA模块支持SR-IOV

- AXI bridge模块支持SR-IOV

ARI机制

取消了Device Number字段,合并到Function Number字段中,这样Routing ID便变成了8-bit Bus Number + 8-bit Function Number的格式,最多支持的Bus数量不变,支持的Function数量增大到256个

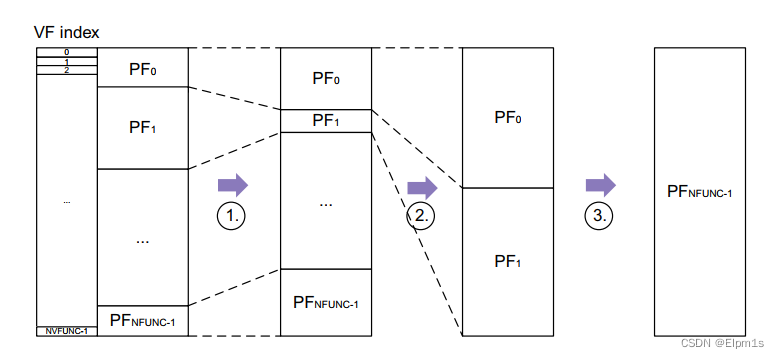

可编程虚拟功能分配

■ Static (DYNAMIC_VF_ENABLE =0)

■ Programmable (DYNAMIC_VF_ENABLE =1)

在coreConsultant中配置控制器时,可以通过设置每个PF的CX_MAX_VF_N参数来确定分配给每个PF的vf数量。这被称为静态VF分配,它假定您的固件不打算更改此分配

但是, programmable VF allocation允许您在重置时更改VFs的分配,方法是写入每个PF中的InitialVFs寄存器,以使用不同的值覆盖CX_MAX_VF_N的默认值

在重置时,常量CX_MAX_VF_n, n=0… 31在每个PF的SR-IOV capability中初始化InitialVFs寄存器。 您的固件在每个PF的SR-IOV capability中重新编程InitialVFs字段。在重新映射之前,必须禁用所有vf。

您的主机软件可以将所有vf分配给任何特定的PF,或者将这些vf分发到不同的PFs子集。下图以VF-to-PF分配修改三次为例。

- 分配给PF0和PFnfunc-1的VFs数量增加,而PF1的VFs数量减少。

- 所有vf平均分布在PF0和PF1上,没有vf分配给其他PF.s

- 所有vf被分配给PFnfunc-1。

2. Programming View

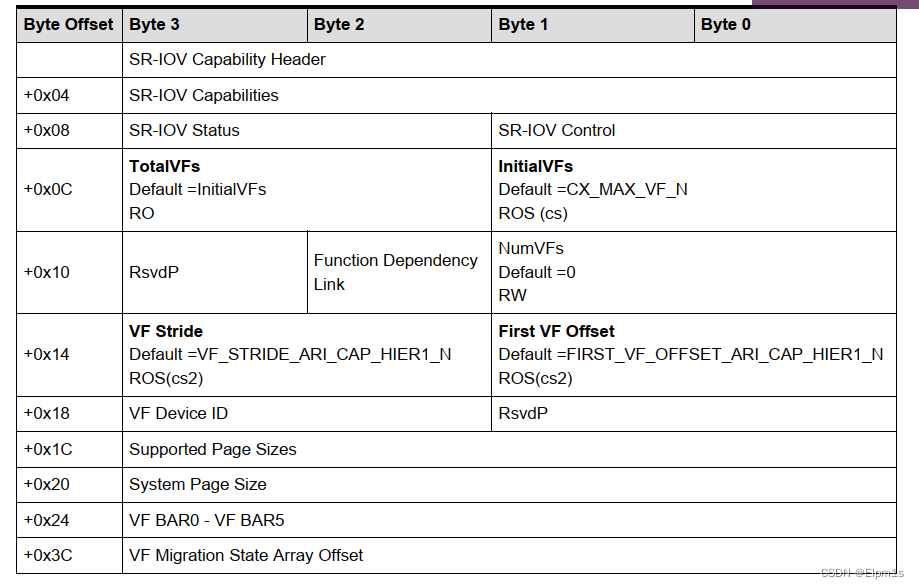

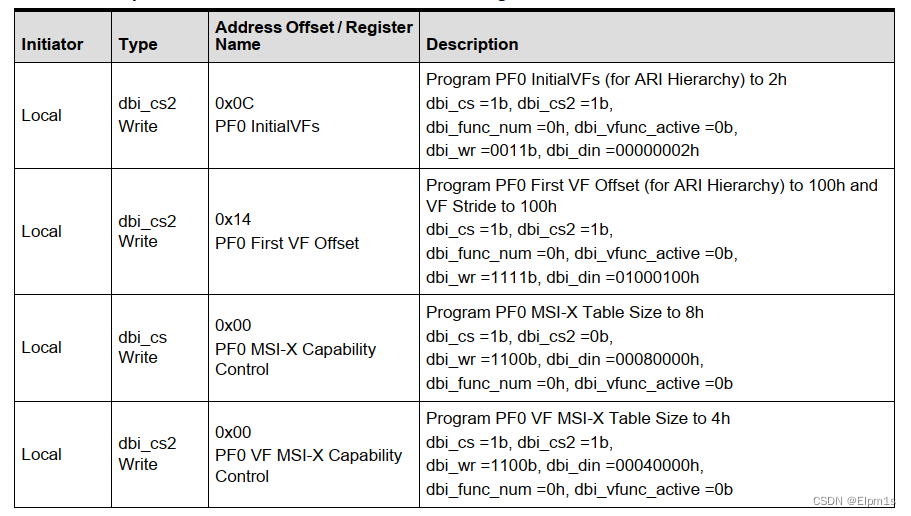

假定DYNAMIC_VF_ENABLE =1,因此,控制器使用InitialVFs寄存器的内容,而不是cx_max_vf_n参数,来确定分配给pf的vf。

复位后,在到远端伙伴的PCIe链路建立之前,您可以通过DBI重新编程InitialVFs、VFStride和First VF Offset寄存器(参见下表)。在最后一次更新InitialVFs后,控制器自动重新计算VF到PF的映射,然后在256个时钟周期后即可运行。在枚举过程中,RC主机发现每个PF中的SR-IOV能力结构,在稍后的阶段,它可以通过启用vf和写入NumVFs寄存器来在每个PF中分配可变数量的vf来编程SR-IOV功能

假设您的PCIe系统有一个ARI-Capable层次结构,并且您已经将SR-IOV控制寄存器的ARI Capable层次结构位设置为1。因此,您必须使用CS2来访问正确的VF Stride和First VF Offset寄存器。

3. Bus Numbering Overview

Routing IDs, requester IDs, and completer IDs 是16位标识符,传统上由三个字段组成 an 8-bit bus number, a 5-bit device number, and a 3-bit function number.使用ARI, 16位字段被解释为两个字段,而不是三个:一个8位总线号和一个8位函数号,设备号字段被消除——因为它总是零,这种新的解释使ARI设备支持多达256个功能,而不是8个功能。内存或I/O请求使用普通BAR寻址指向VF。当一个

VF BAR在目标EP中匹配,然后识别父PF和子VF。配置请求使用ARI-capable Bus.Device.Function (BDF) 指向VF。

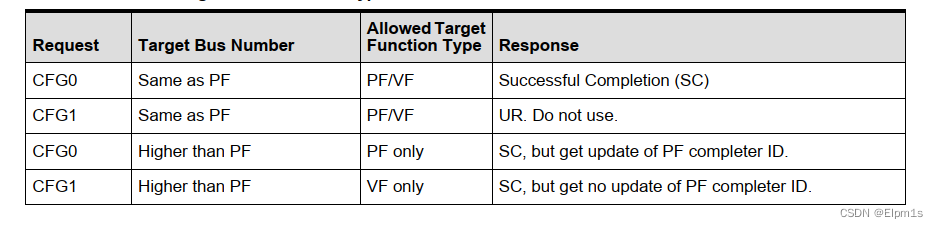

CFG Handling

在SR-IOV使能的EP中,一个VF可以比PF占用更高的总线号。为了防止PF completer ID不必要的更新,所有CFG写请求到更高总线号上的VF必须使用CfgWr1。

4. Routing ID Generation Examples

本节使用四个例子来展示控制器如何使用不同的设置分配function和bus number,编号由PFs和VFs、First VF Offset和VF Stride的数量决定。您的主机软件必须为设备中的每个PF读取VF Stride和First VF Offset寄存器,并计算分配给该设备的总线号的数量,然后继续编号下一个设备/总线。PF从0开始编号,而VF从1开始编号。第一个PF的第一个VF表示为PF0 VF1。pf和vf的路由id计算规则如下:

■ Function number (FN) for PFj is j, where j =0,1,2,…CX_NFUNC-1

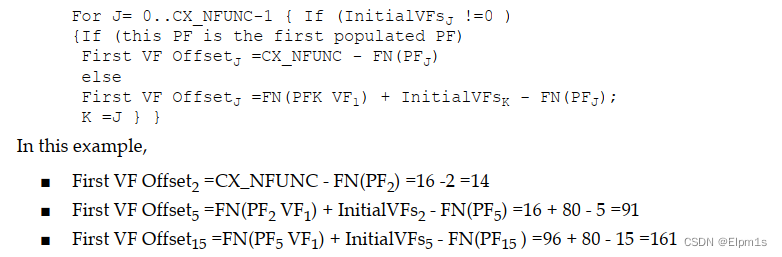

■ FN for PFj VFi is {FN(PFj)+ First VF Offsetj + (i -1)* VFStridej}%256, where i =1,2,…InitialVFsj

在某些情况下(参见示例3和示例4),First VF Offset的默认值不适用,您必须重新编写它

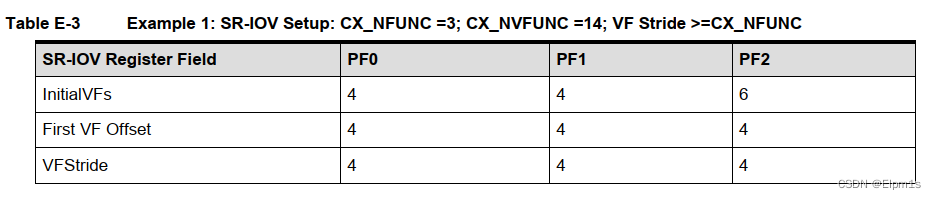

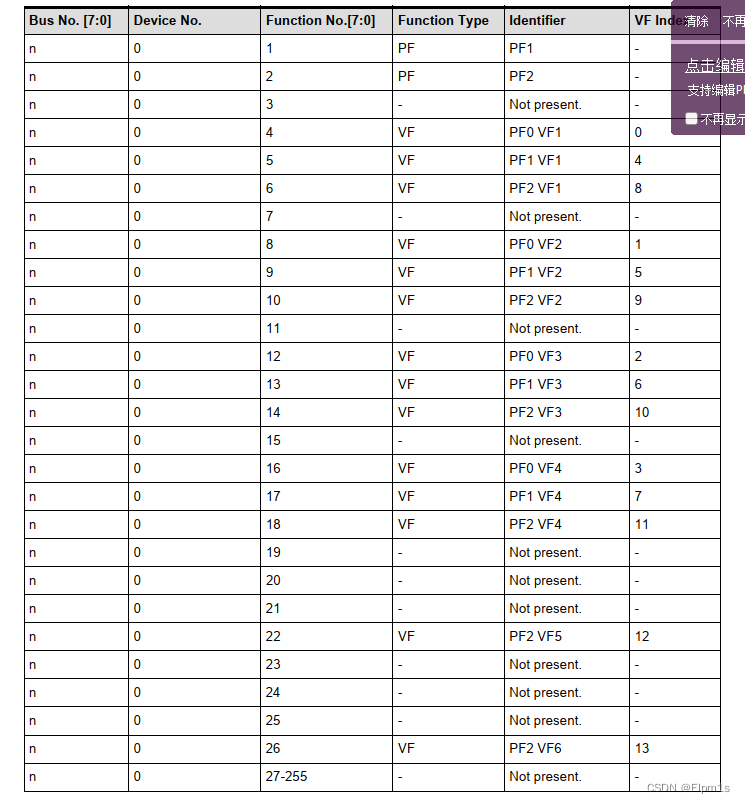

例1:

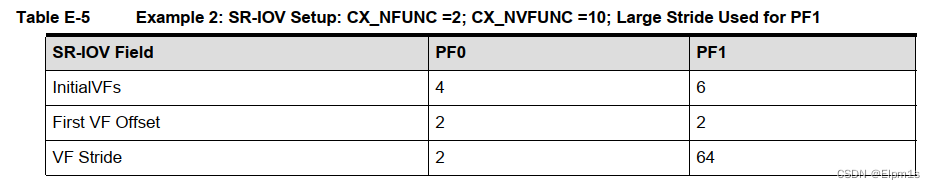

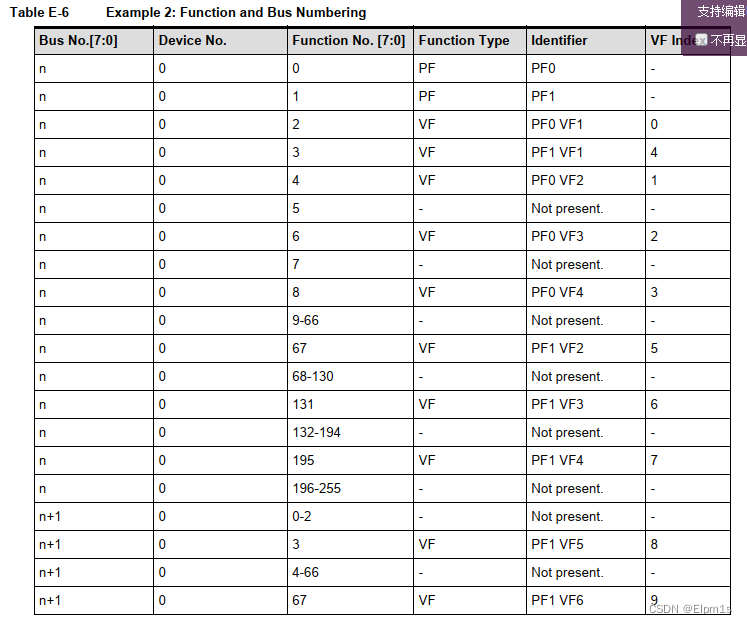

例2:

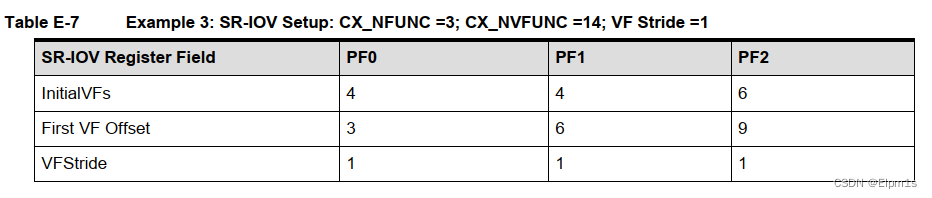

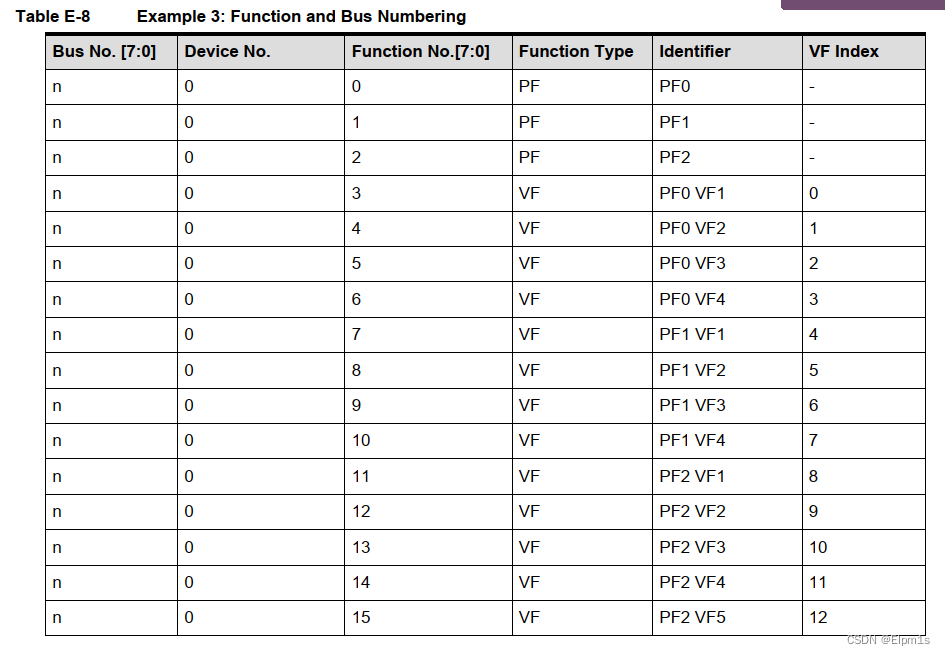

例3:

使用最小VF步幅1。 First VF Offset的默认值不适用,必须通过DBI重新编程,才能建立PCIe链路。

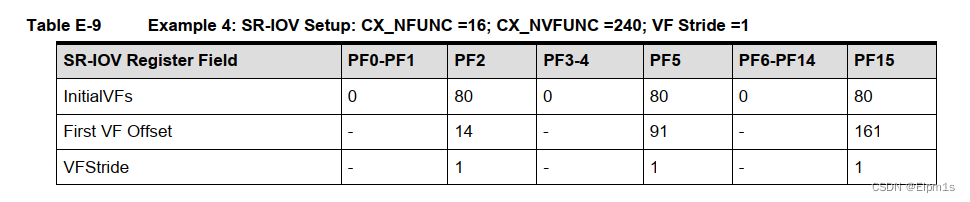

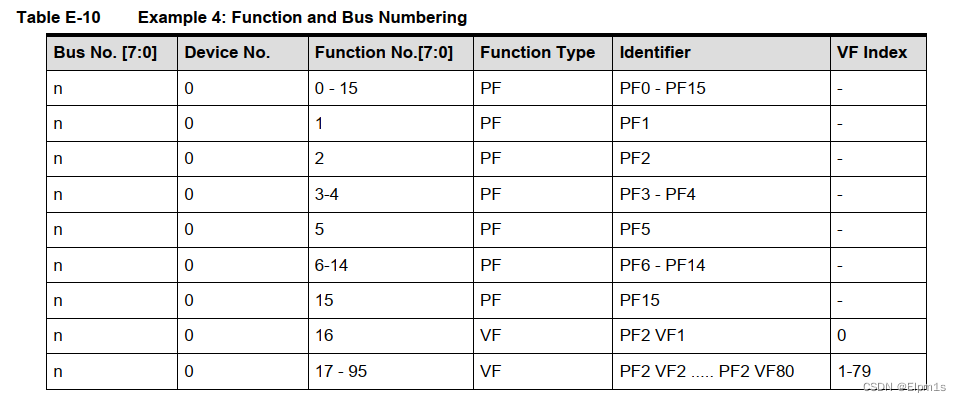

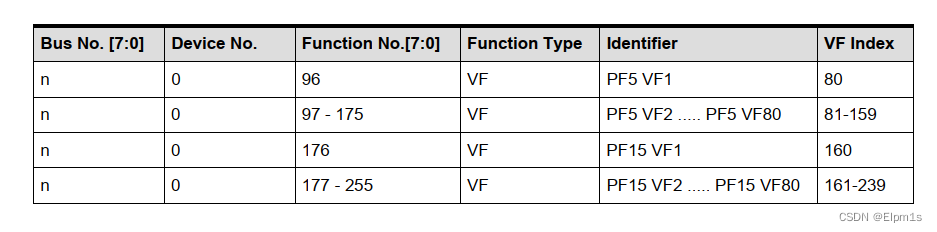

例4:

在本例中,许多pf是未填充的,并且没有为它们分配vf。 First VF Offset的默认值不适用,必须重新编程,在建立PCIe链路之前,通过DBI进行如下操作:

5. VF Capability Configuration

每个VF都有自己的一组capability结构,其中大部分是可选的。许多默认的VF capability寄存器字段继承自父PF。有关更多信息,请参阅各个VF寄存器的描述。

6. MSI / MSI-X Overview in SR-IOV

您必须在coreConsultant中配置控制器,以包括vf和pf的MSI-X功能结构。VF MSI能力结构是可选的,您只能在per-device的基础上包含它。您不能在per-PF的基础上包含它。即使MSI- x和MSI结构可以在同一设计中存在(被包括),在PFs和VFs中的软件一次只能启用一种。你可以做以下任何一件事:

- Enable MSI for PF but enable MSIX for VFs

- Enable MSI for VFs but enable MSIX for PFs

- Enable MSI for VFs and PFs

- Enable MSI-X for VFs and PFs

特定PF中的所有vf必须启用或禁用MSI。 MSI不是在每vf基础上启用的。 这同样适用于MSI-X。

6.1 Unique Per-VF Values

所有VF MSI寄存器(除了MSI控制寄存器中的一些字段)在给定的PF中可以对每个VF有不同的值。

除VF MSI-X Control 寄存器外,单个PF中的所有VF MSI-X寄存器都具有相同的值,并且是只读的。VF MSI-X Control 寄存器的MSI-X表大小字段(PCI_MSIX_CAP_ID_NEXT_CTRL_REG.pci_msix_table_size)必须对PF内的所有vf具有相同的值。要写入它,必须对父PF中的相同寄存器执行DBI_CS2写入(即断言DBI_CS2输入,或用于AXI桥的CS2地址位)。

除了VF TPH Requestor Capability 寄存器(TPH_REQ_CAP_REG_REG)之外,单个PF中的所有VF TPH寄存器都具有相同的值,并且是只读的。要写入它,必须对父PF中的相同寄存器执行DBI_CS2写入(即断言DBI_CS2输入,或用于axis桥的CS2地址位)。

6.2 Default Values

VF MSI capability寄存器字段的默认值与PF相同,没有专门的VF配置参数来设置VF MSI capability 寄存器字段的默认值。VF MSI-X capability 寄存器字段的默认值来源于专用的VF配置参数。(在硬件中不能修改Read-Only VF MSI-X Table Offset、Table BIR、PBA的值和PBA BIR寄存器。因此,在配置时必须使用配置参数仔细设置这些寄存器的值)

6.3 MSI and MSI-X Generation Interface

您的应用程序可以请求控制器使用MSI接口发送一个MSI。您可以使用相同的接口发送MSI-X,其中您的应用程序还必须提供MSI-X地址和数据。MSI-X capability structure指向驻留在特定BAR下的内存空间中的MSI-X表和Pending Bit Array (PBA) 结构。在系统初始化期间,主机系统软件将MSI-X地址和数据值存储在位于应用程序内存空间的MSI-X表中。

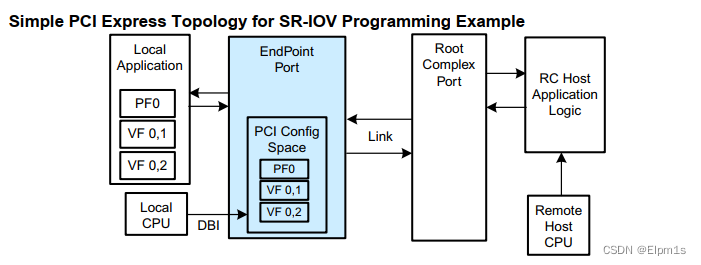

7. Programming Example

本节提供了一个在ep(没有axis Bridge)设置SR-IOV的示例,如下所示

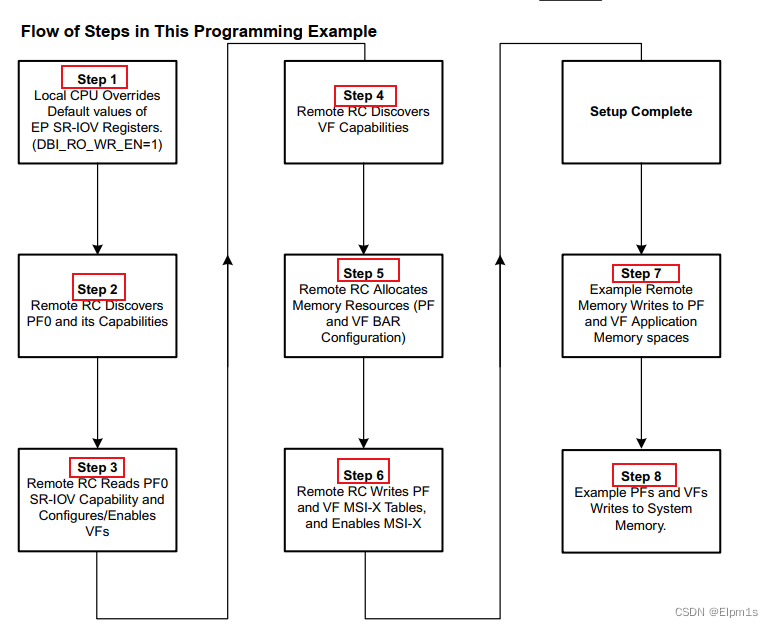

本示例中的步骤流程如下:

Step1:

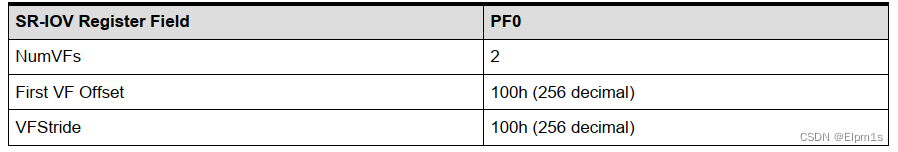

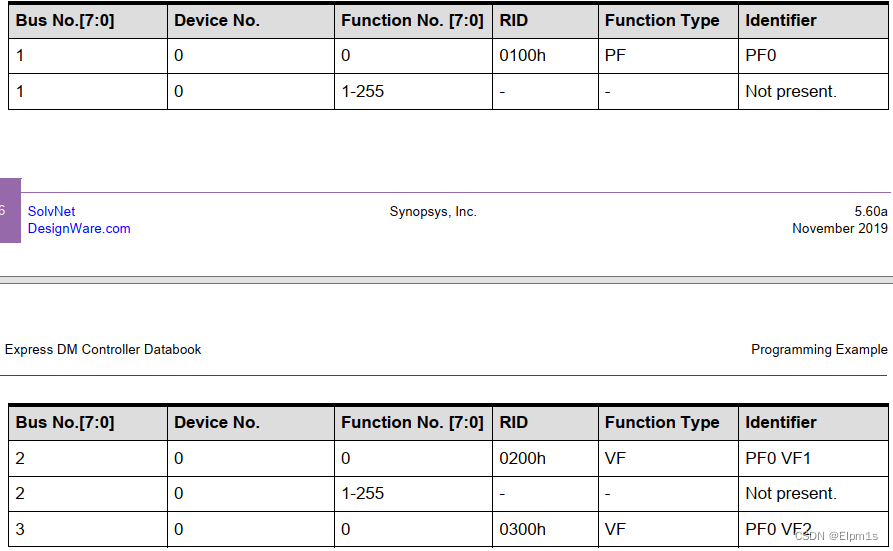

下表总结了上表中寄存器值设置对总线和功能编号的影响。

下表总结了上表中寄存器值设置对总线和功能编号的影响。

下表显示控制器如何分配BDF

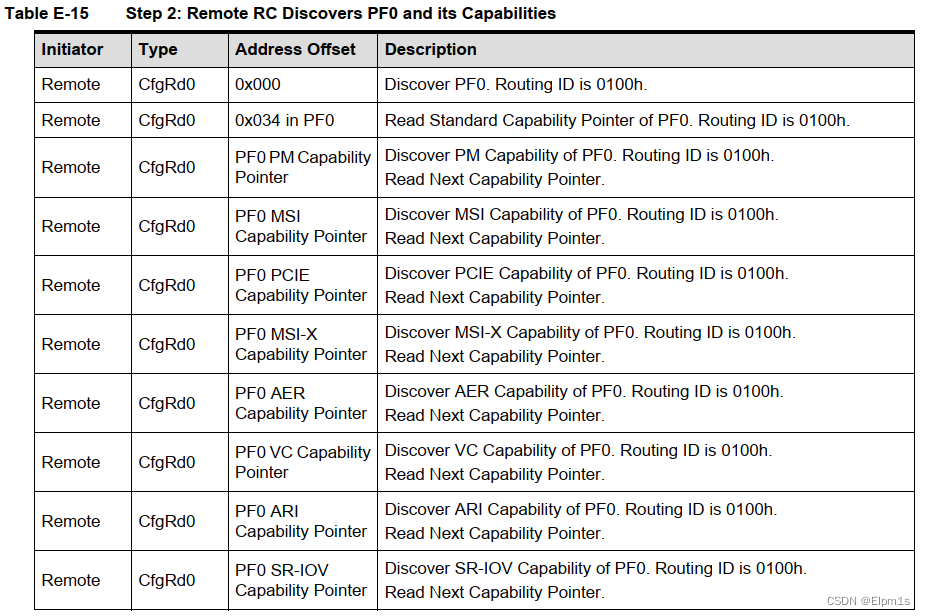

Step2:

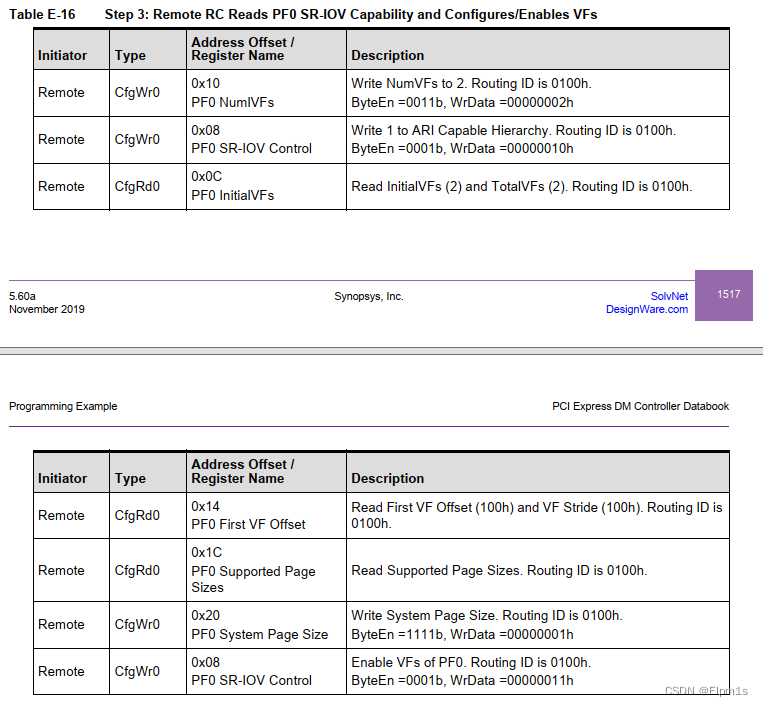

Step3:

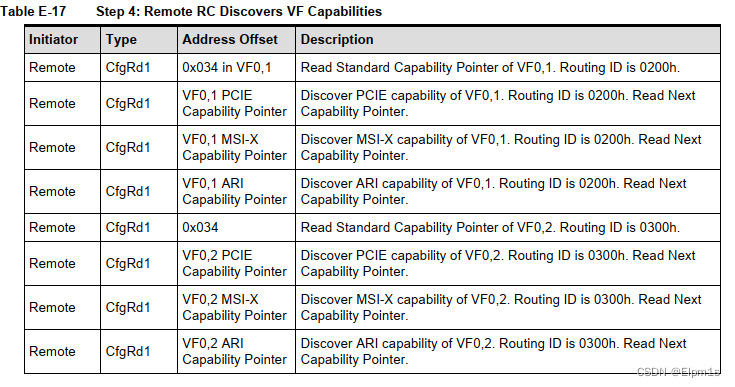

Step4:

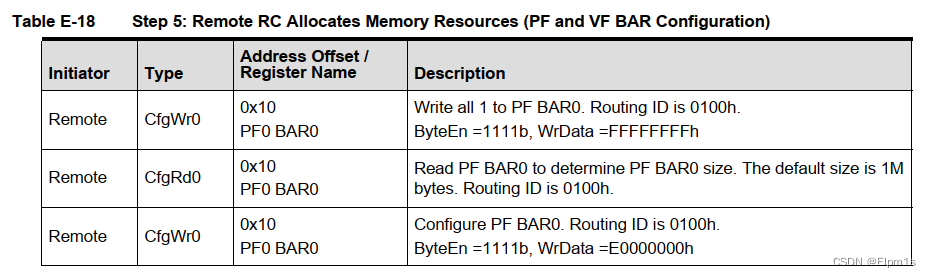

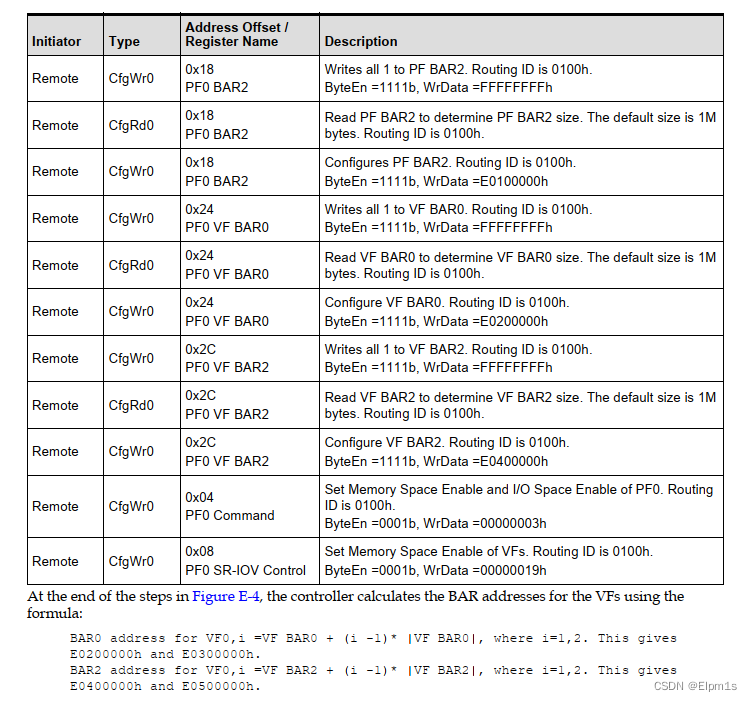

Step5:

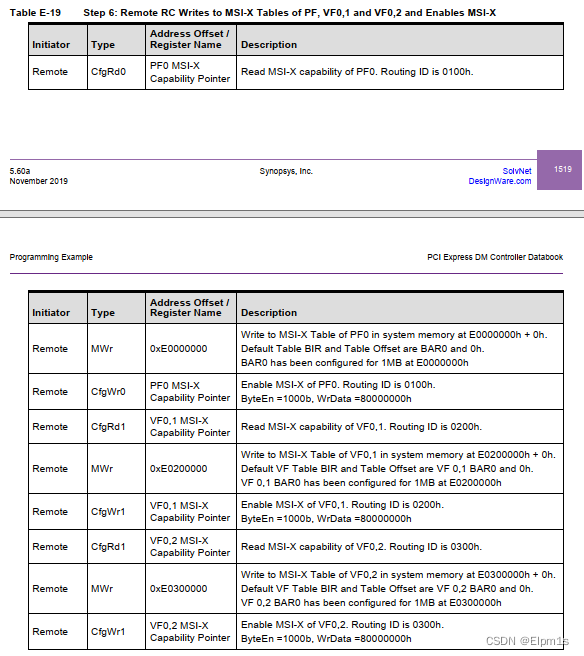

Step6:

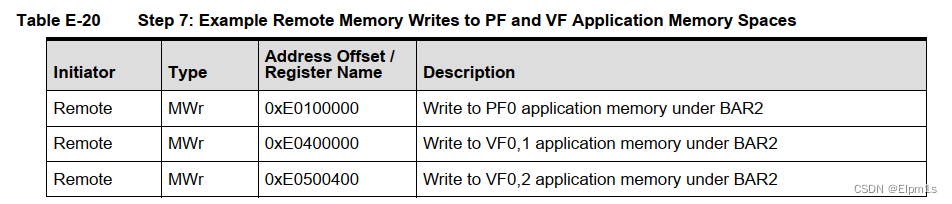

Step7:

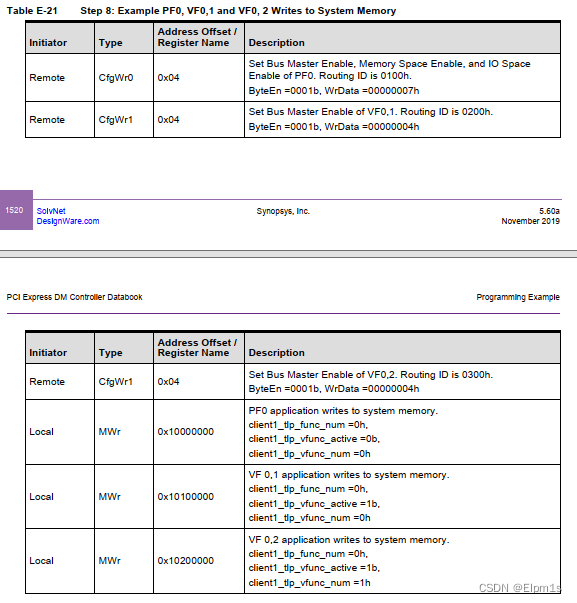

Step8: