目录

1.SV和Verilog数据类型的区别

Verilog中,数据类型分为两类:variable和net,对于这两类,它们都是4值逻辑,即可能的状态有:0,1,x,z

SV中,数据类型有2个属性:type和data type

type:表明该数据是variable型还是net型

data type:表明数据是4值逻辑还是2值逻辑

variable型既可以是4值逻辑,也可以是2值逻辑;而net型只能是4值逻辑。

SV中,新引入了logic的数据类型,其原因是在搭建TB时对于每一个信号相对于TB是reg还是wire是要严格区分的,声明错误会导致问题;为了方便声明信号,引入了logic,使用logic类型的信号不用管是reg还是wire,但logic不能表示多驱动信号,如inout,inout信号一般用wire表示。logic一般在接口中用的比较多,并且其还可以在initial,always,assign中使用。

2.SV内建数据类型

2.1SV为何要引入2值逻辑?

这主要是为了验证服务的,2值逻辑只能产生0/1,而TB产生的激励一般也只有0/1而不产生x/z的激励,并且2值逻辑可以节省内存,使仿真速度加快。

2.2根据2/4值逻辑,SV可将数据类型分为如下:

四值逻辑(默认值x):integer、reg、logic、net-type(例如wire,tri)(四值数据偏向于硬件,因为实际电路中的信号除了0/1,也可能是未知态x或者高阻态z)

二值逻辑(默认值0):byte(8)、shortint(16)、int(32)、longint(64)、bit(1)(二值数据偏向于软件,因为软件中大多数都是0/1)

2.3 2/4值数据的相互转化

program example1;

bit[2:0] A=3'b011;

logic[2:0] B=3'b0xz;

initial begin

A=B;//A=3'b000,可见4值逻辑中的x/z转化成2值逻辑会成为0

end

endprogram

program example2;

bit[2:0] A=3'b011;

logic[2:0] B=3'b0xz;

initial begin

B=A;//B=3'b011,可见2值逻辑中的0/1转化成4值逻辑还是对应着0/1

end

endprogram

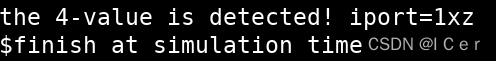

当我们使用monitor监测DUT的输出时,一般采用的都是四值变量来接收DUT的输出,这样才能知道DUT输出的所有状态;当我们不小心使用了2值变量来连接DUT的输出,若DUT产生x/z则会被转换成0,而我们将永远也不会察觉,SV提供了一个方法来监测x/z的产生:$isunknown,它可以在变量出现x/z时返回1:

program test;

logic[2:0] iport=3'b1x1;

initial beign

if($isunknow(iport)==1)begin

$error("the 4-value is detected !! iport=%0b",iport);

end

end

endprogram仿真结果如下:

根据有/无符号,SV可将数据类型分为如下:

有符号类型:byte、shortint、int、longint、integer(32位)

无符号类型:bit、reg、logic、net-type(例如wire,tri)

program example3;

logic [7:0] logic_vector = 8'b1000_0000;//无符号

bit [7:0] bit_vector = 8'b1000_0000;//无符号

byte signed_vector = 8'b1000_0000;//有符号

initial begin

$display(“logic_vector= %d ”,logic_vector);//128

$display(“bit_vactor = %d ”,bit_vector);//128

$display(“signed_vector= %d ”,signed_vector);//-128

end

endprogrambit[7:0]是否和byte等价?

当然不等价,bit是无符号位,而byte是有符号位,最高位会成为符号位,若讲有符号数据和无符号数据混用会导致错误的结果,如下:

program example4;

byte signed_vector = 8'b1000_0000;//有符号

bit [8:0] result_vector;//无符号

initial begin

result_vector = signed_vector

$display(“@1 result_vector= 'h%x ”,result_vector);//180

result_vector = unsigned'(signed_vector);

$display(“@2 result_vector= 'h%x ”,result_vector);//080

end

endprogram这里需要着重强调的是,8位的有符号数据赋值给9位的无符号数据后,符号位仍然体现了出来,1000_0000赋值给9位无符号位是0_1000_0000,而符号位体现了出来导致最高位是1,因此整个是1_10000_0000,用16进制表现出来就是180;然后将有符号数据强制无符号化后赋值给9位数据,由于没有符号位,所以9位无符号数据为0_10000_0000,所以16进制为080。

2.4位宽不一致会导致什么问题?

program example5;

logic [3:0] x_vector = 4'b111x;

bit [2:0] bit_vector;

initial begin

$display(“@1 x_vector= 'b%b ”,x_vector);//'b111x

bit_vector = x_vector;

$display(“@2 bit_vector= 'b%b”,bit_vector);//'b110,可见位宽不一致会将最高位舍弃

end

endprogram