一、振荡器OSC和锁相环PLL模块

锁相环是一种控制晶振使其下你跟对于参考信号保持恒定的电路。主要作用是通过软件实时配置片上外设时钟

譬如当30MHz的OSCCLK信号经锁相环倍频后,倍频倍数可通过PLLCR[DIV]设置,可设置为10,经过PLL后的信号变为300MHz,因为28335的时钟频率为150MHz,所以需要将PLLSTS[DIVSEL]设置为2,可得300/2=150MHz时钟信号。

二、各种时钟信号

1.外设时钟

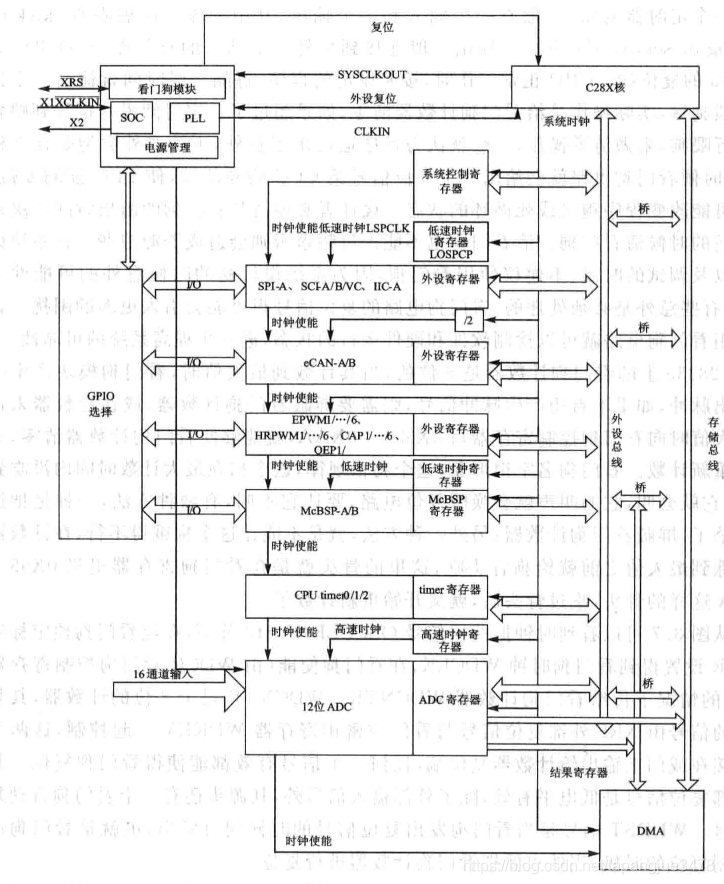

下图是系统控制及外设时钟,CLKIN是经过PLL模块后送往CPU的时钟信号,经过CPU的分发,作为SYSCLKOUT送至各个外设,因此SYSCLKOUT=CLKIN

在28335进行开发时,通常会使用到一些外设,因此需要给外设提供时钟信号。因此,在系统初始化的时候,就需要对使用到的各个外设的时钟进行使能,使能代码如下所示:

SysCtrlRegs.PCLKCR0.bit.ADCENCLK=1; //使能ADC的时钟

SysCtrlRegs.PCLKCR1.bit.ECAP1ENCLK=1; //使能SCIA的时钟

SysCtrlRegs.PCLKCR3.bit.GPIOINENCLK=1; //使能GPIO的时钟

对于低速时钟寄存器LOSPCP和高速时钟寄存器HISPCP,可以通过给寄存器设值,来设置时钟,具体配置如下所示:

A)LOSPCP:

LOSPCP=0时,LSPCLK=SYSCLKOUT

LOSPCP≠0时,LSPCLK=SYSCLKOUT/(2LOSPCP)

B)HISPCP:

HISPCP=0时,HSPCLK=SYSCLKOUT

HISPCP≠0时,HSPCLK=SYSCLKOUT/(2HISPCP)

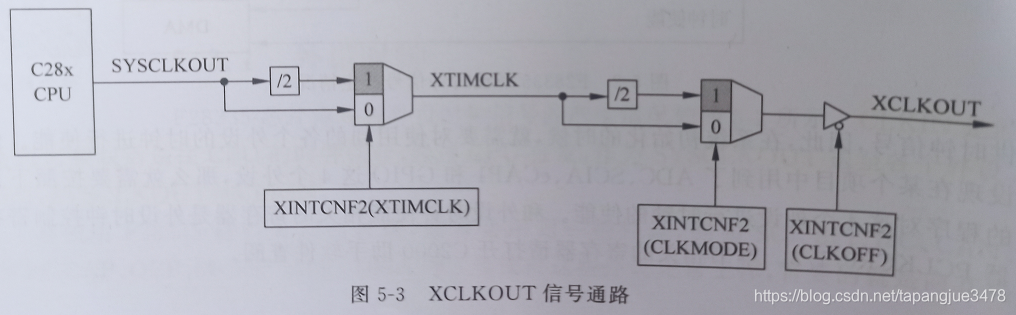

2.XCLKOUT信号

28335提供了一路可以输出到芯片外部的时钟信号,即XCLKOUT,通过对SYSCLKOUT分频可以得到不同的时钟频率,XCLKOUT的信号如图所示:

经过配置,XCLKOUT可以等于SYSCLLKOUT,也可以为其1/2或者1/4,如果不适用XCLKOUT信号机,可以通过XINTCNF2寄存器中的CLKOFF位将其关闭。

三、对于EALLOW和EDIS的说明

为了提高安全性能。TI的DPS对很多关键寄存器做了保护处理,DSP由于在上电复位之后,状态寄存器基本上都是清零,而这样的状态下正式上述特殊寄存器禁止改写的状态。为了能够对这些特殊寄存器进行初始化,所以再对上述特殊寄存器进行改写之前,先要执行“EALLOW”,在设置完成后,执行“EDIS”