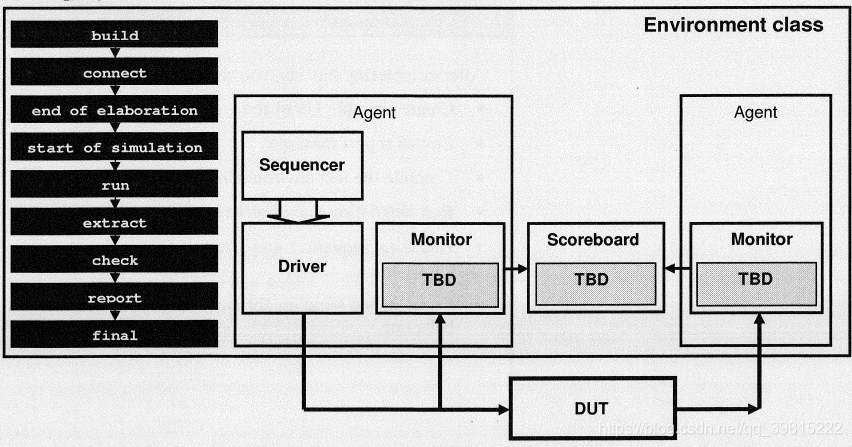

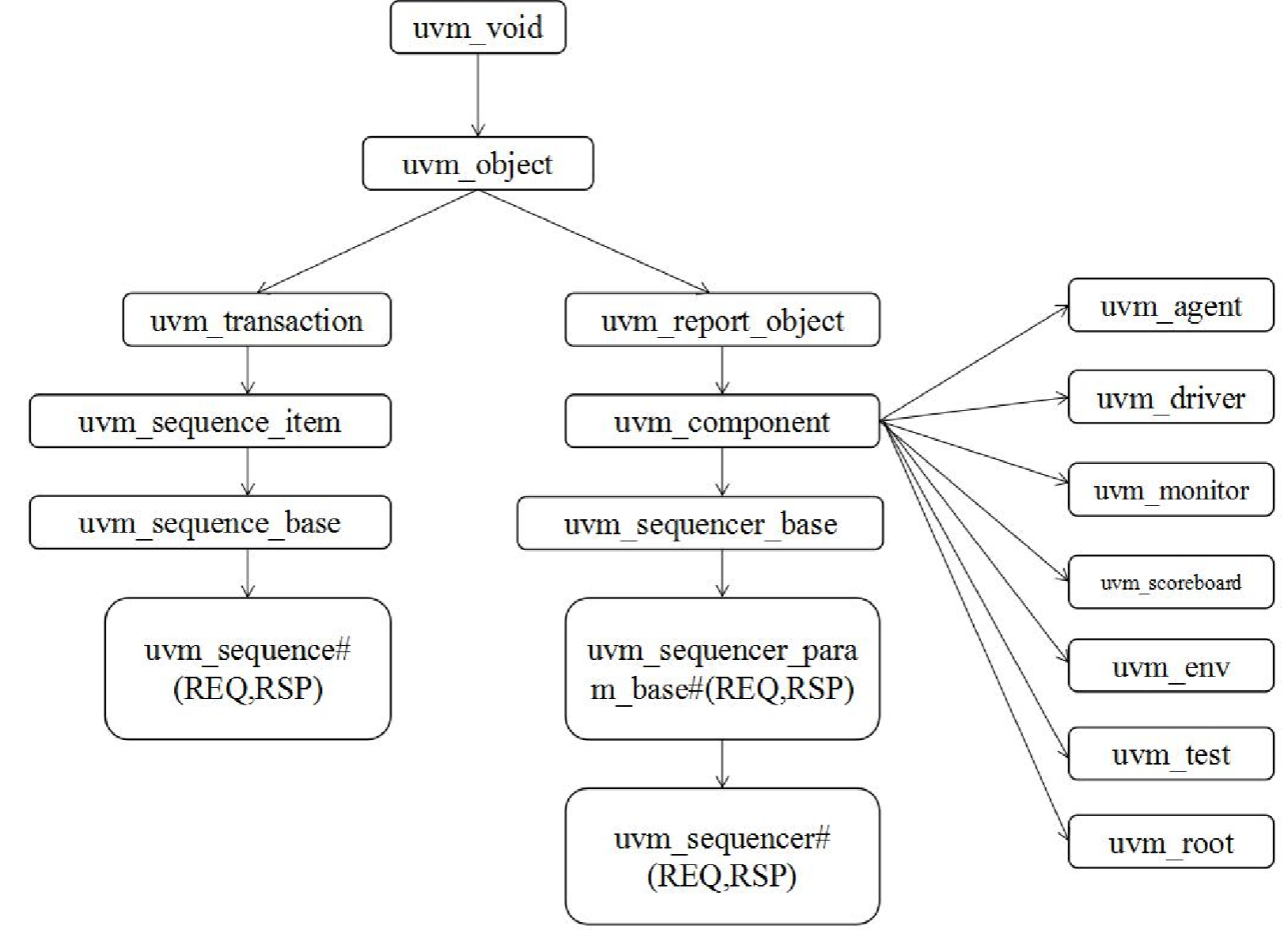

UVM验证平台可以看成是由多个模块组合在一起,通过把这些模块放在一起利用接口和DUT连接起来,从而最终实现验证的目的。如图为一个完整的UVM验证平台框图,下图中每一个组件(即UVM中的component)就是一个类。

这些模块不是简单的函数或者过程,而是一个个实实在在的对象文件,这些对象内部会包括一些function或者task等来协作完成整个验证平台的运行

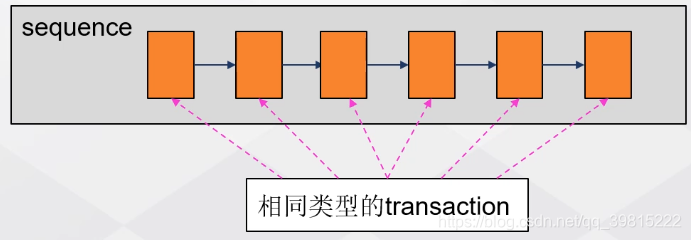

sequence是产生transaction(事务)的组件,属于平台外的,但由于和testbench关系较大,所以一并讨论。

0. sequence组件

事务反生器,即产生transaction。transaction不能算是testbench中的组件,只是各组件间的数据流。

- 基类

- uvm_sequence_item

该类可以派生事务级的transaction类,这是使验证平台相互连通的重要组件。

为了使transaction能随机化,需要给每个成员指定为rand。

transaction和driver类是不同的,它是有生命周期的,他在仿真的某一时间产生,经过driver驱动,在经过testbench中的参考模型处理,最终由scoreboard比较完成后,其生命周期结束。 - uvm_sequence

产生事务发生器,即派生出sequence,并可以在定义时产生一系列transaction对象(一般来说,一个sequence产生一种类型的transaction)。它不属于验证平台的部分,但是却能给验证平台提供激励。

- task

- body()

sequence中最重要的部分就是其中的task: body(),作用是产生和控制transaction。当一个sequence启动之后,会自动执行body中的代码。

- 宏

- `uvm_do(ptr)

该宏在UVM中比较常用,作用是:

(1)创建transaction对象,调用一次即产生一次对象,即产生完整地使平台运行的一个包。

(2)将其随机化

(3)最终将其送给sequencer。

ptr为指针,可通过该指针访问创建的事务对象。driver取走这个transaction后,uvm_do并不会立刻返回执行下一次uvm_do,而是等待在那里,直到driver返回item_done信号。

1. testcase

在testbench中首先需要创建一个测试案例,它用来实例化和配置environment,使env模拟不同的配置环境,执行不同的测试行为;指定测试的sequence

若一个功能点的testcase的env配置完成,则不能改动,若要改动或修复则需重新配置env。

2. environment组件

env组件可以将testbench中所有组件封装在一起,在该类中可以实例化多个agent,reference model,scoreboard等,并将其互连。

注意:一旦该组件定义完成,后续不得轻易对其更改,若更改须重新验证所有的testcase。因此在定义时最好事先配置好interface,使env就有可配置性。

- 基类

- uvm_env

可以派生出可以实例化testbench中各组件类的容器类。和driver一样,容器类在仿真中是一直存在的,可以使用uvm_component_utils宏来实现factory的注册

3. agent组件

agent中可以实例化sequencer,driver,monitor等组件,并将这些组件连接起来。

- 模式

- active

需要实例化sequencer、driver、monitor,连接sequencer和driver。

该状态是agent的默认状态,在代码中,is_active是agent内建的变量,默认值为UVM_ACTIVR。 - passive

该模式下只有monitor,因此没有驱动DUT的能力,但可以用来捕获DUT的输出信号并转化为transaction。

- 基类

- uvm_agent

4. sequencer组件

用来启动sequence,并将transaction对象发送给driver。绝大部分功能由UVM实现

- 基类

- uvm_sequencer(transaction)

作用:

(1)sequence在向sequencer发送transaction时,会先发一个请求,sequencer把这个请求放在一个仲裁队列中,并检测仲裁队列里是否有某个sequence发送transaction的请求

(2)检测driver是否申请transaction

5. driver组件

激励驱动,从sequencer接收transaction对象,并转化为DUT可接收的pin级信号,再按照DUT总线接口协议要求驱动DUT。

- 基类

- uvm_driver(transaction)

6. monitor组件

driver类负责把transaction级别的数据变成DUT的端口级别,并驱动给DUT;monitor的行为与其相对,用于收集DUT的端口数据,并将其转换为transaction交给后续的组件reference model,scoreboard处理。

monitor要通过TLM_port和其他组件相连。

- 基类

- uvm_monitor

7. reference model组件

模拟DUT的功能行为,根据输入的激励产生相应的结果,并交给scoreboard。

无直接调用基类,均由uvm_component扩展

8. scoreboard组件

比较reference model和DUT的输出结果是否一致,从而判断DUT的功能是否正确;同时可以将功能覆盖率收集嵌入到该组件中。

- 基类

- uvm_scoreboard