脉动阵列

脉动阵列(Systolic Array)是H. T. Kung在1982年提出的1,一种由众多简单的PE(Processing Element,处理元件)按规则排列的硬件架构,本身的核心概念是让数据在运算单元的阵列中进行流动,减少访存的次数,并且使得结构更加规整,布线更加统一,提高频率。

1. 二维矩阵

例子X ∗ W = Y X*W=YX∗W=Y

[ X 11 X 12 X 13 X 14 X 21 X 22 X 23 X 24 X 31 X 32 X 33 X 34 X 41 X 42 X 43 X 44 ] ∗ [ W 11 W 12 W 13 W 14 W 21 W 22 W 23 W 24 W 31 W 32 W 33 W 34 W 41 W 42 W 43 W 44 ] = [ Y 11 Y 12 Y 13 Y 14 Y 21 Y 22 Y 23 Y 24 Y 31 Y 32 Y 33 Y 34 Y 41 Y 42 Y 43 Y 44 ] \left[ \begin{matrix} X_{11} & X_{12} & X_{13} & X_{14} \\ X_{21} & X_{22} & X_{23} & X_{24} \\ X_{31} & X_{32} & X_{33} & X_{34} \\ X_{41} & X_{42} & X_{43} & X_{44} \\ \end{matrix}\right] * \left[ \begin{matrix} W_{11} & W_{12} & W_{13} & W_{14} \\ W_{21} & W_{22} & W_{23} & W_{24} \\ W_{31} & W_{32} & W_{33} & W_{34} \\ W_{41} & W_{42} & W_{43} & W_{44} \\ \end{matrix}\right] = \left[ \begin{matrix} Y_{11} & Y_{12} & Y_{13} & Y_{14} \\ Y_{21} & Y_{22} & Y_{23} & Y_{24} \\ Y_{31} & Y_{32} & Y_{33} & Y_{34} \\ Y_{41} & Y_{42} & Y_{43} & Y_{44} \\ \end{matrix}\right]⎣⎢⎢⎡X11X21X31X41X12X22X32X42X13X23X33X43X14X24X34X44⎦⎥⎥⎤∗⎣⎢⎢⎡W11W21W31W41W12W22W32W42W13W23W33W43W14W24W34W44⎦⎥⎥⎤=⎣⎢⎢⎡Y11Y21Y31Y41Y12Y22Y32Y42Y13Y23Y33Y43Y14Y24Y34Y44⎦⎥⎥⎤

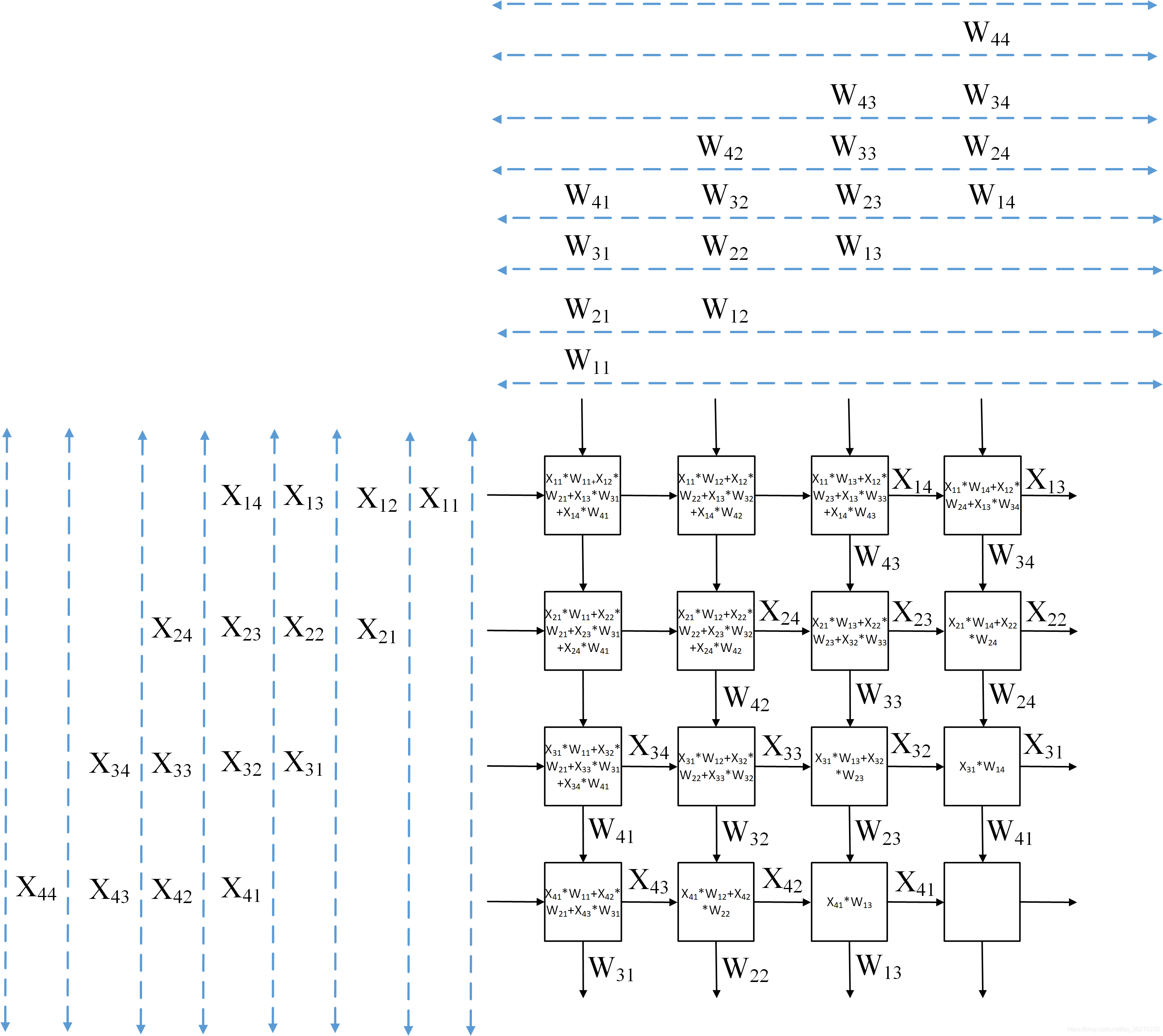

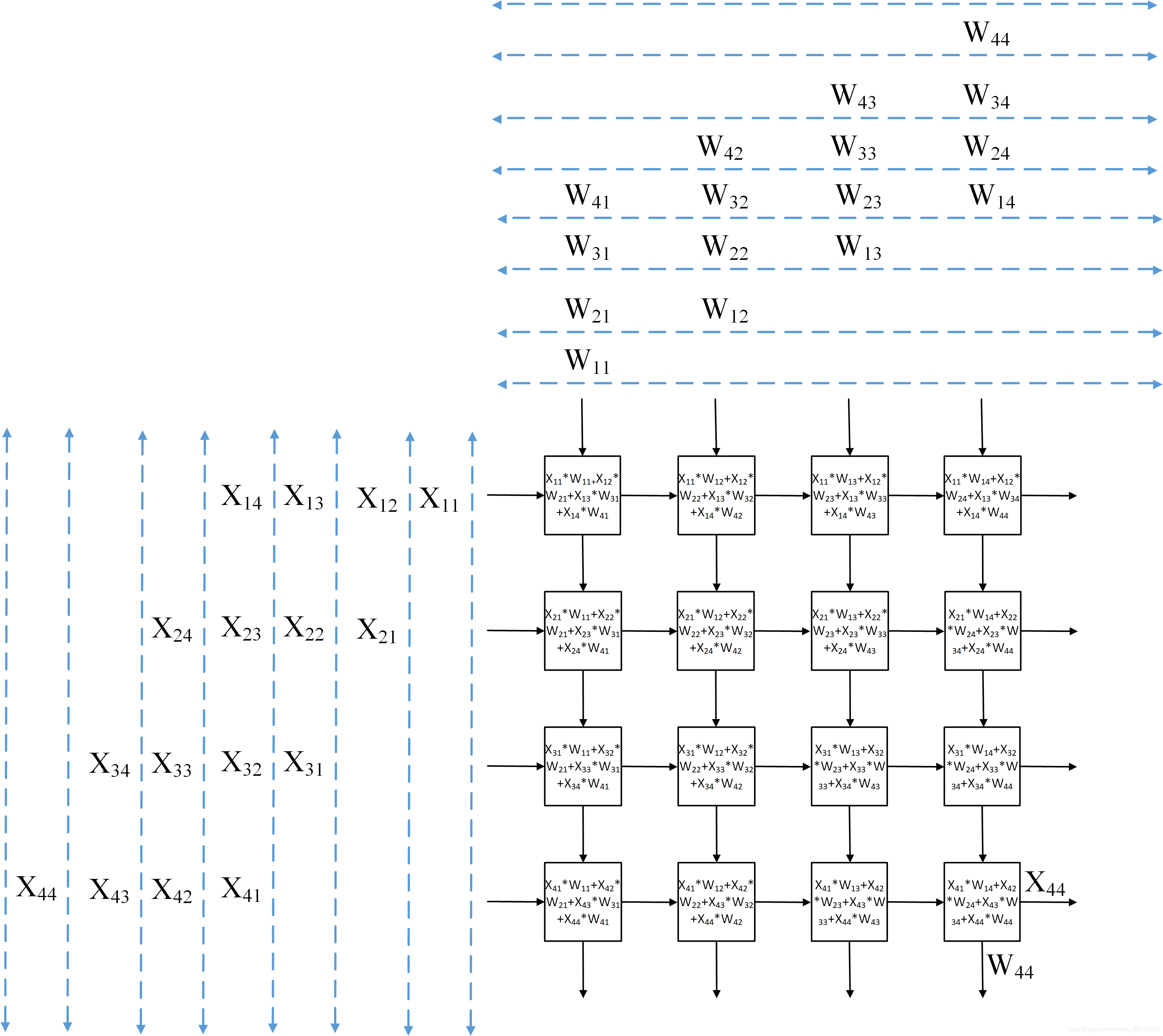

2. 二维脉动阵列实现方法

- 二维脉动阵列实现方法主要有两种,重点讲一下第二种方法。

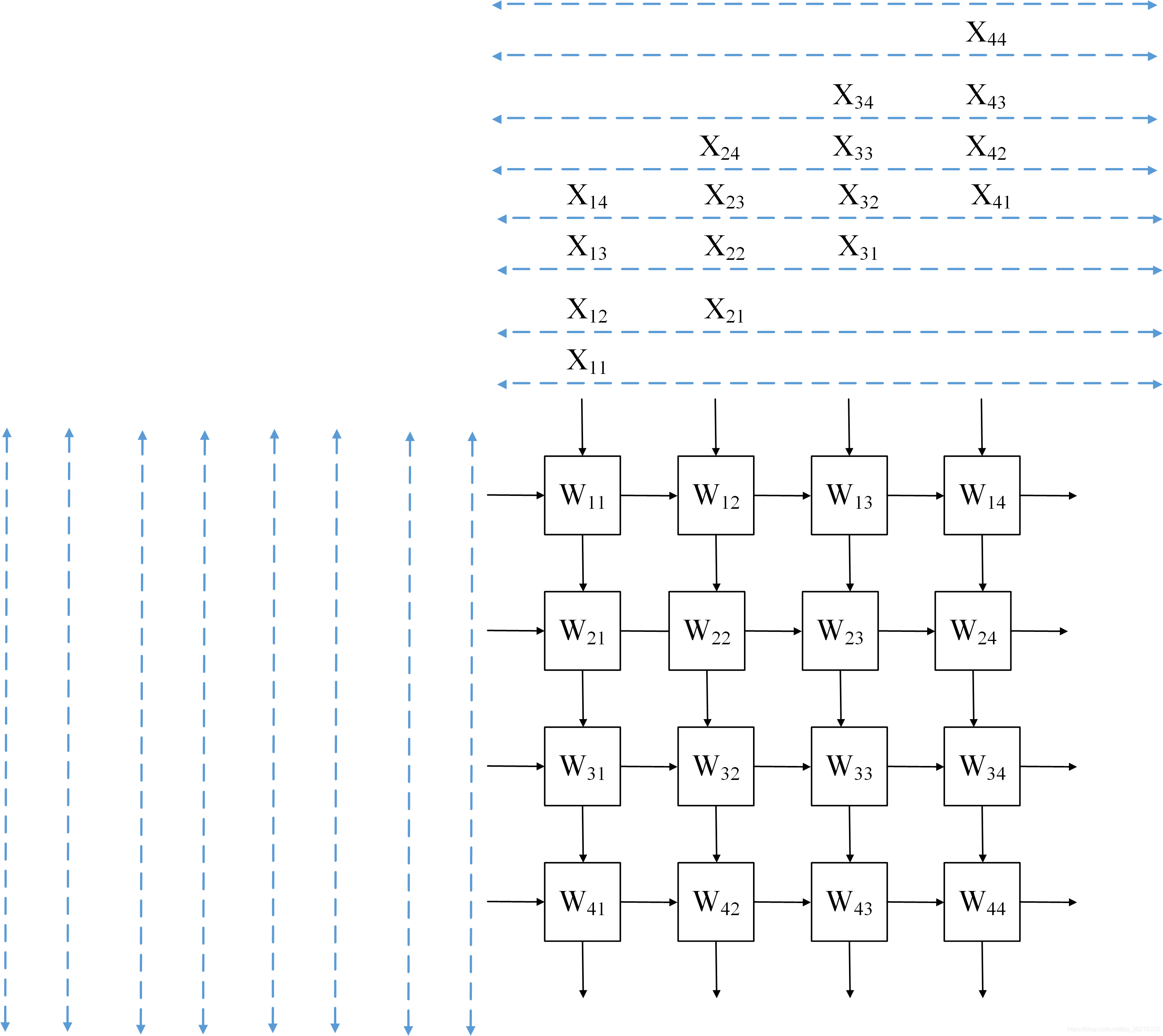

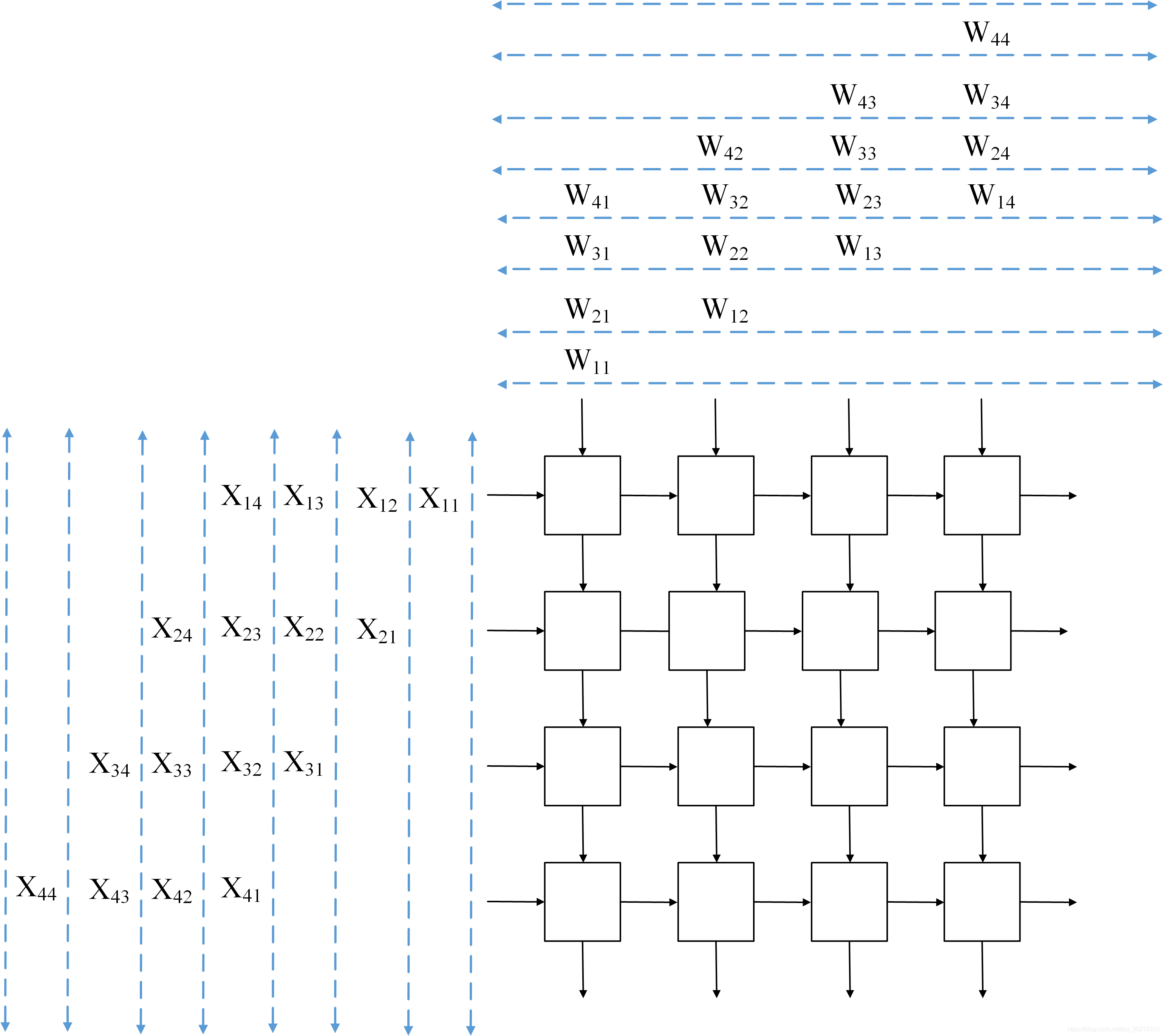

- 一个矩阵W存入PE(Processing Element,处理元件),X和Y的元素将分别沿垂直与水平方向自上而下和自左至右有节奏地流动,W的元素则按它们的原行列顺序存入阵列的相应行列位置上的PE中,每一PE存入矩阵W的一个元素。

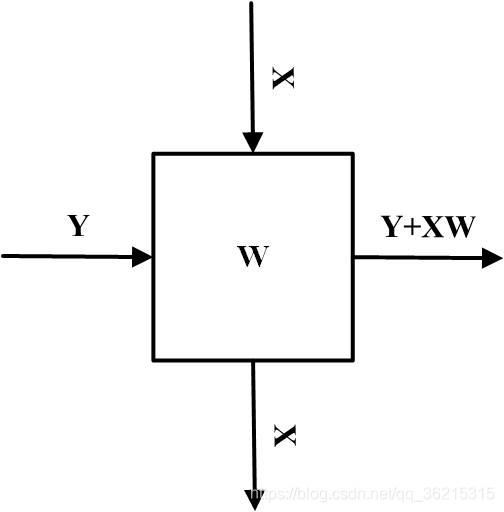

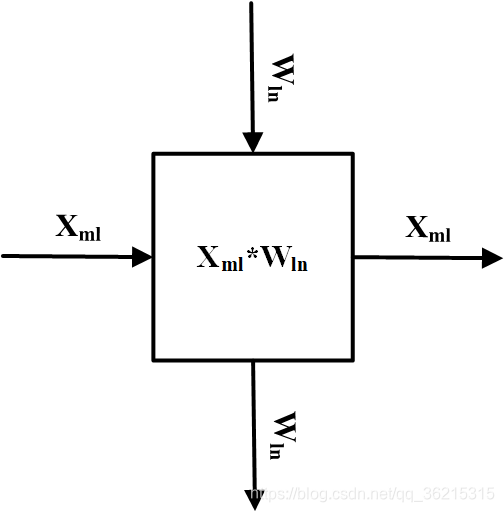

PE:

二维脉动阵列:

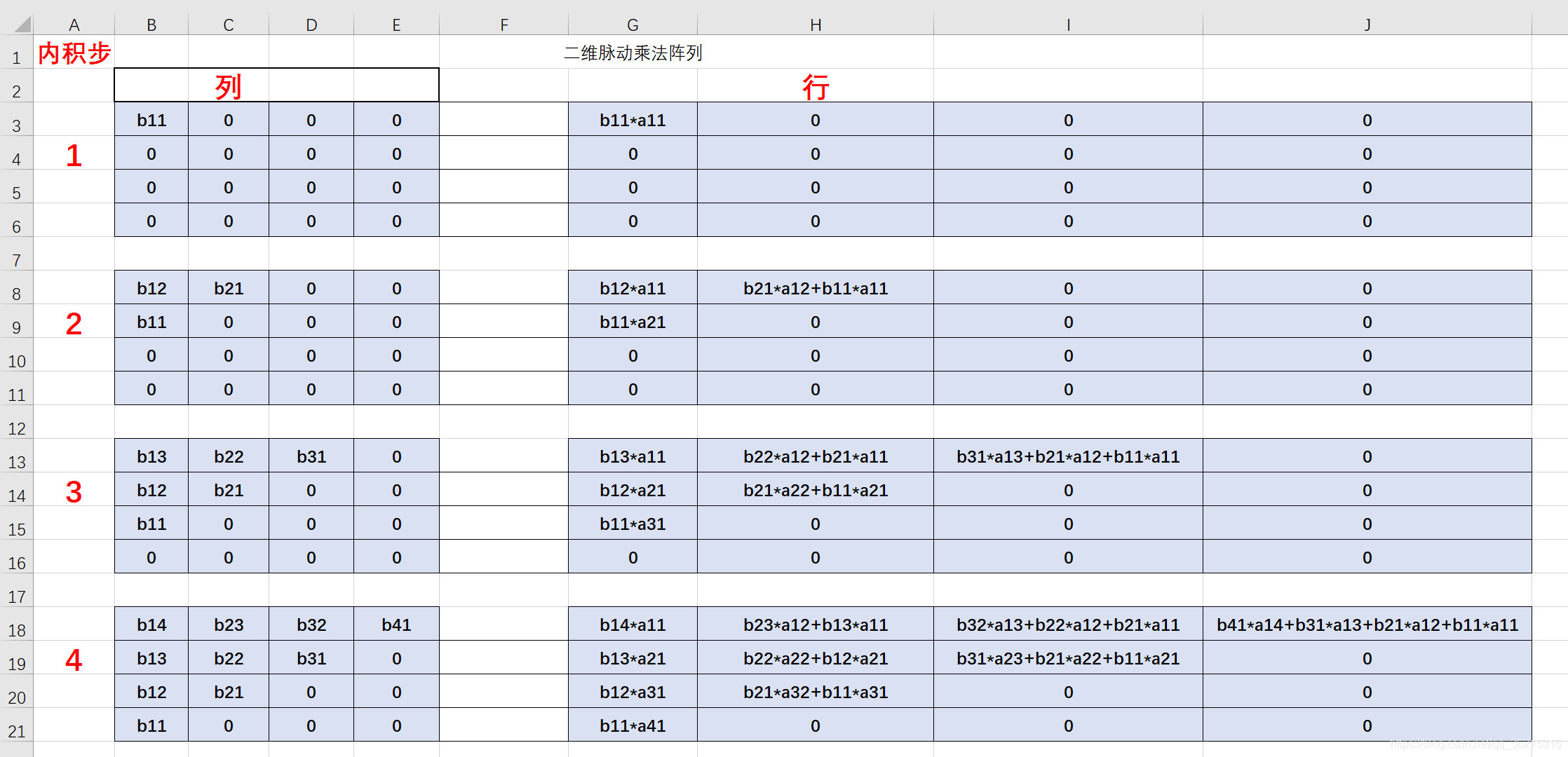

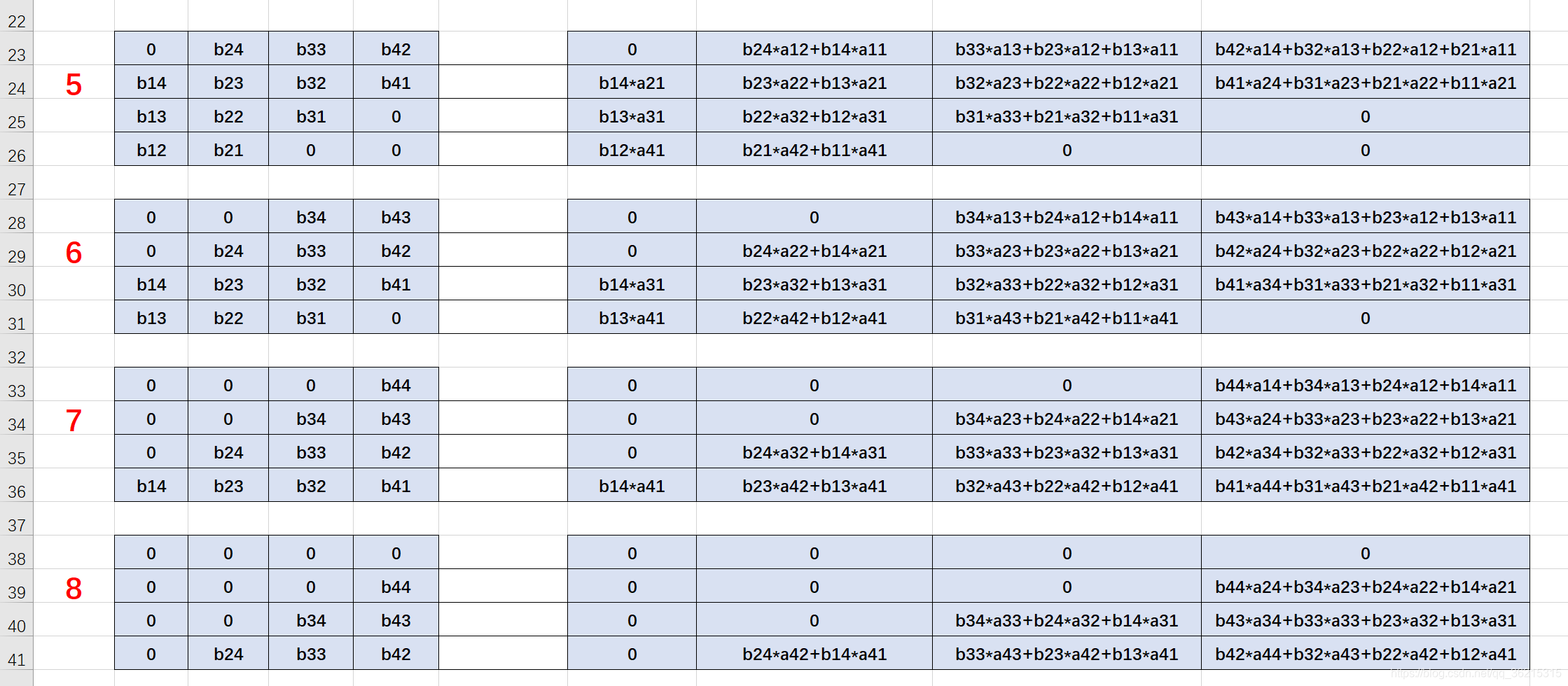

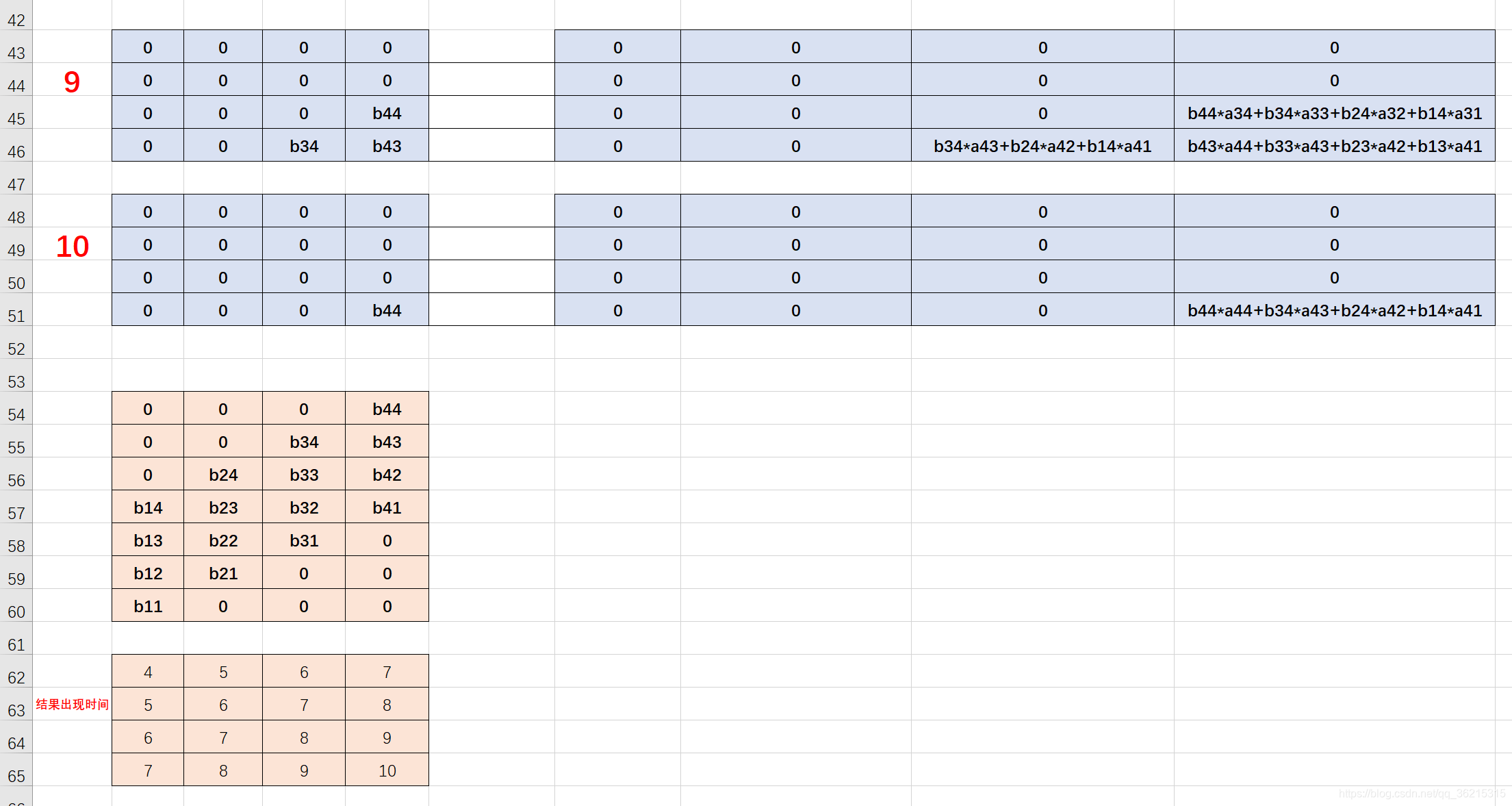

这里就用放一下之前用excel保存的结果:

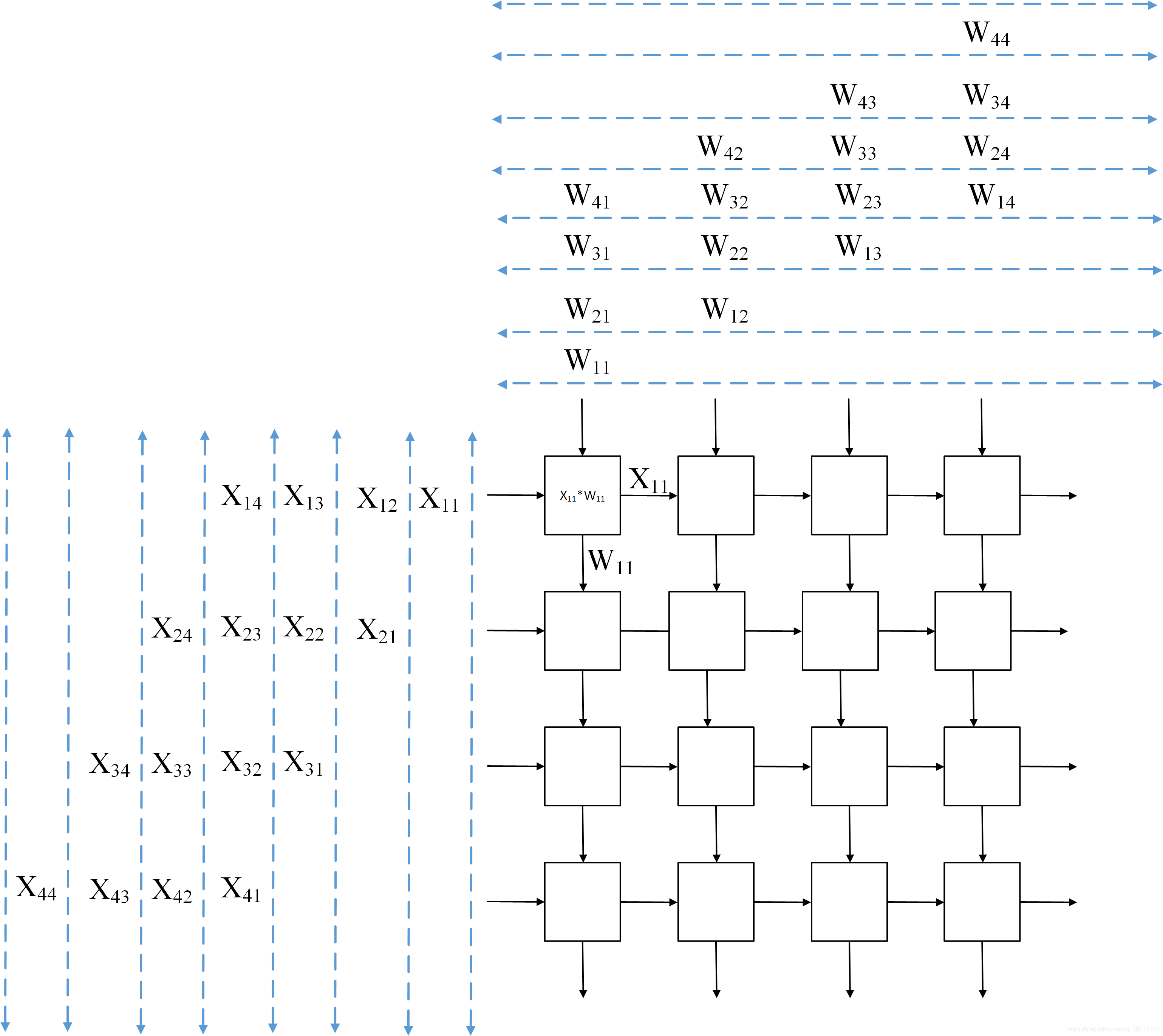

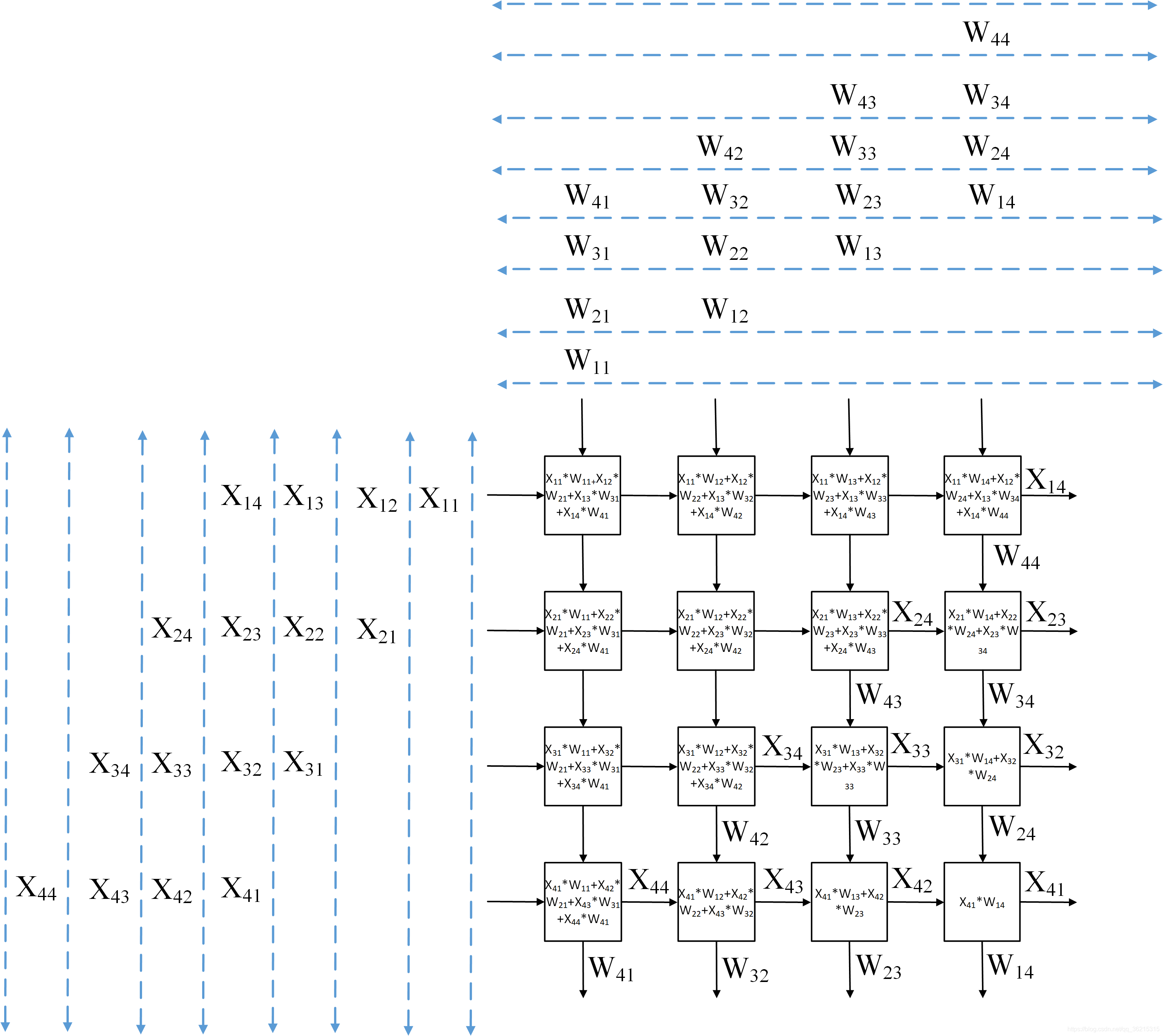

- 在脉动阵列中流动的是X,W,而每一步的Y保存在每个PE或者cell中,每一个PE就是一个乘加器MAC。X以行输入,W以列输入。

PE:

二维脉动阵列:

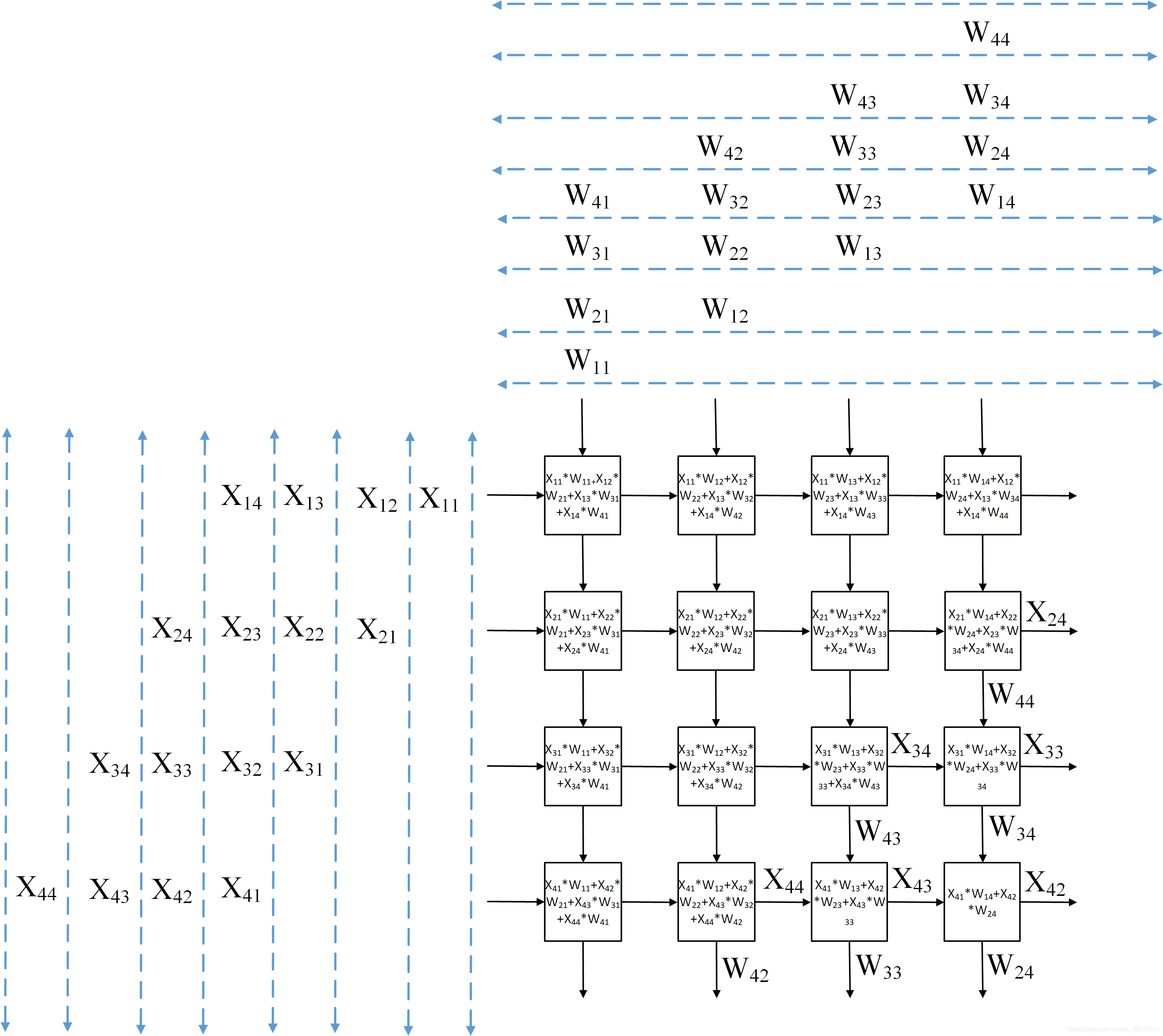

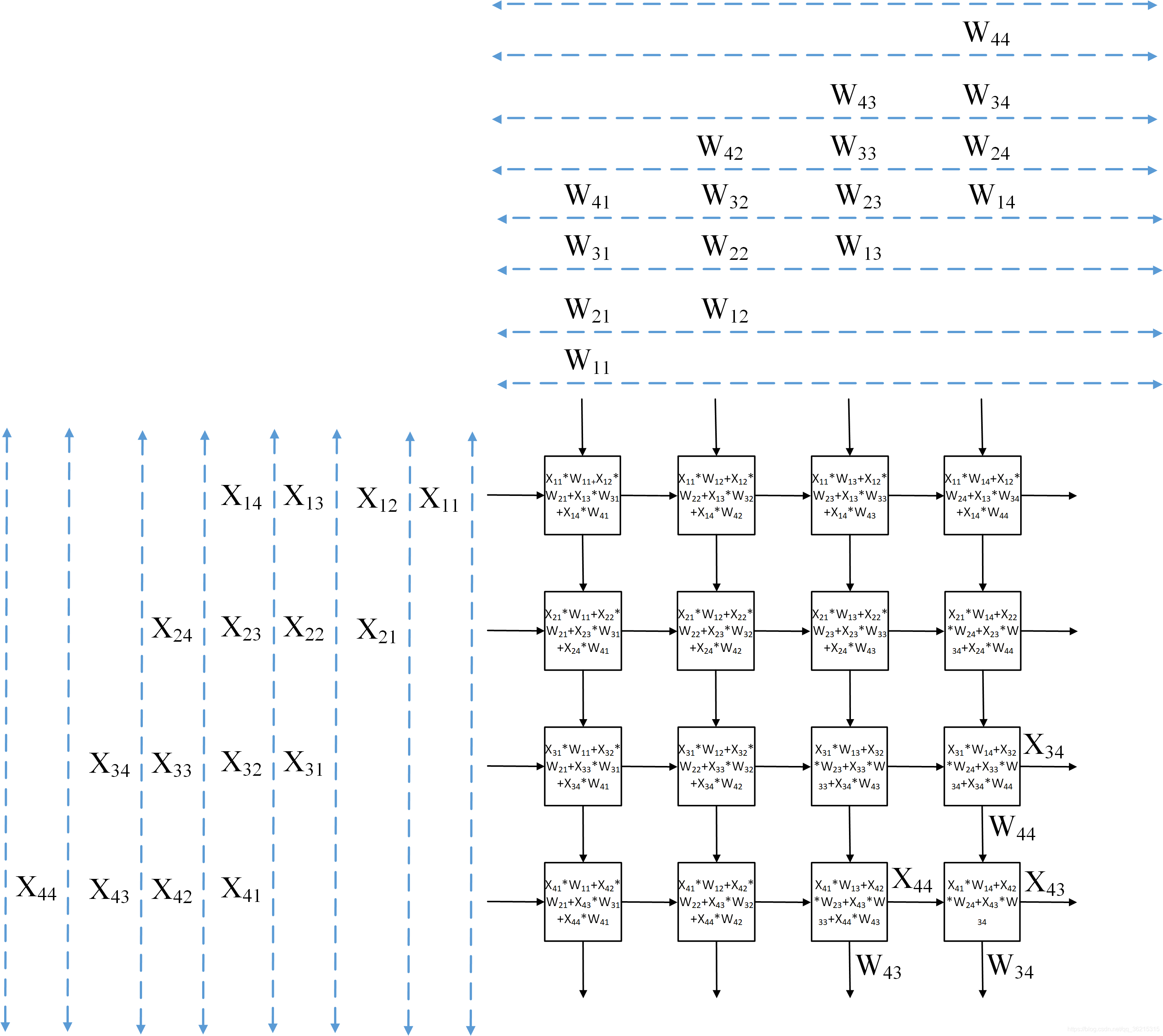

过程分析

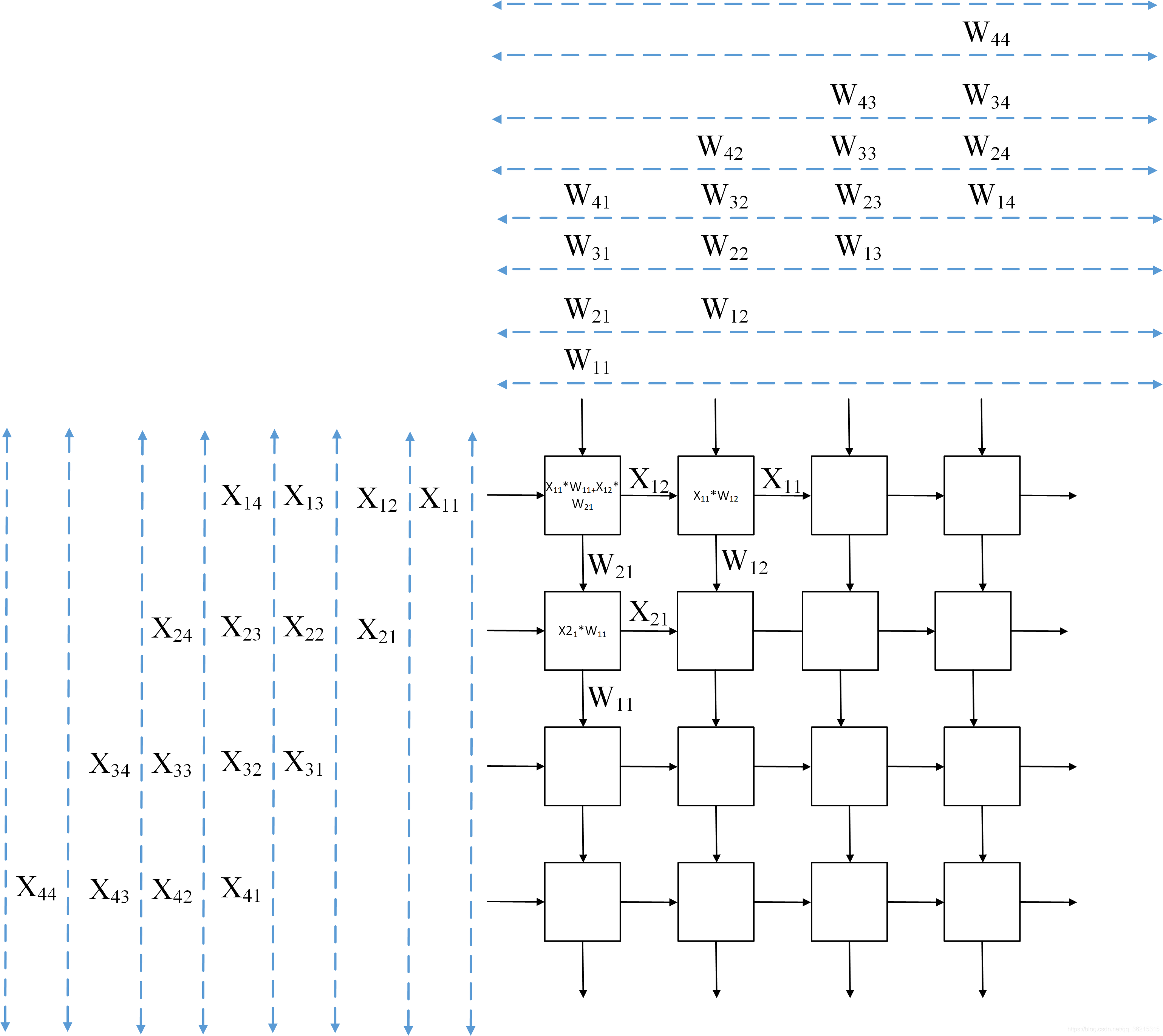

Step1:

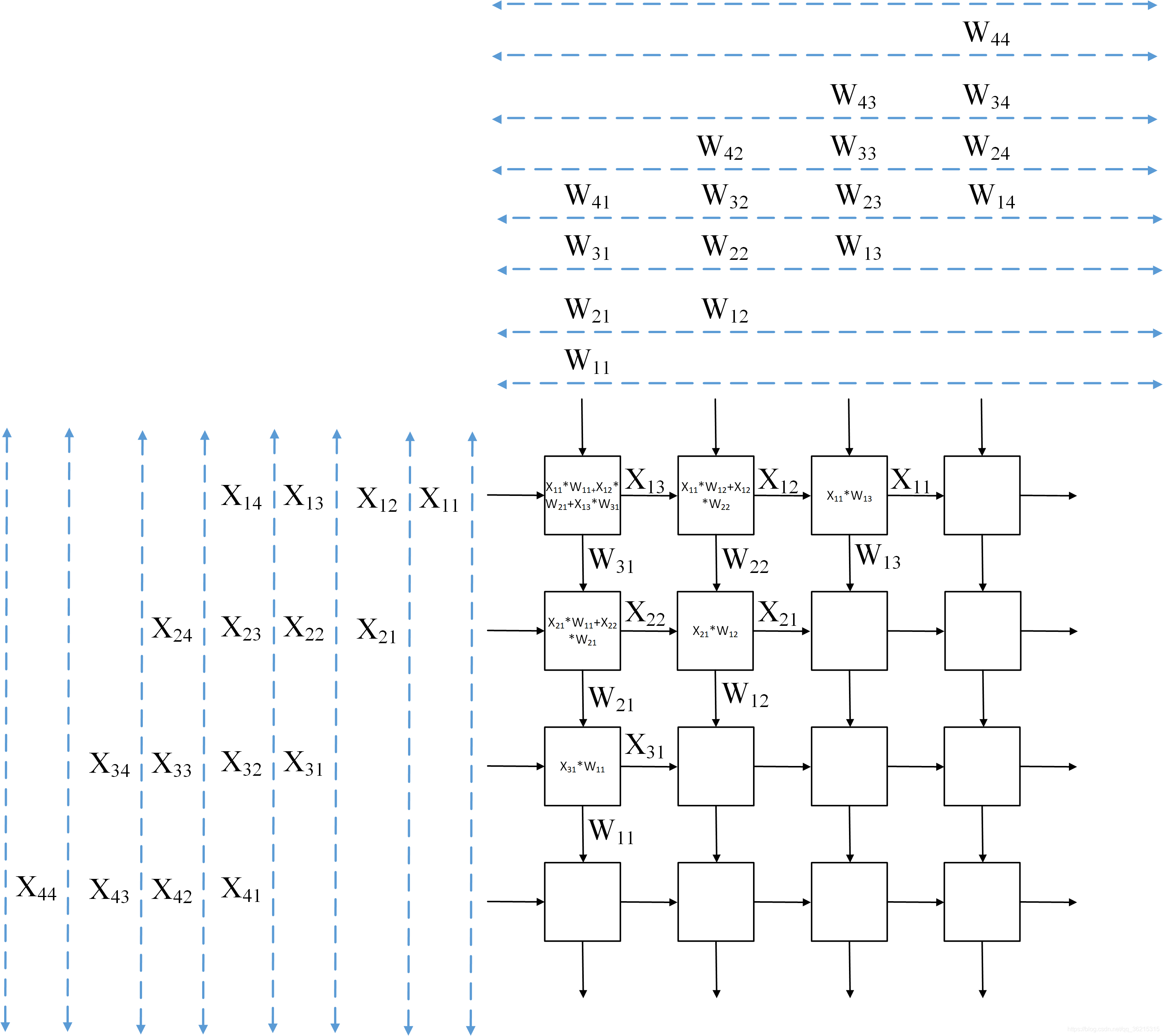

Step2:

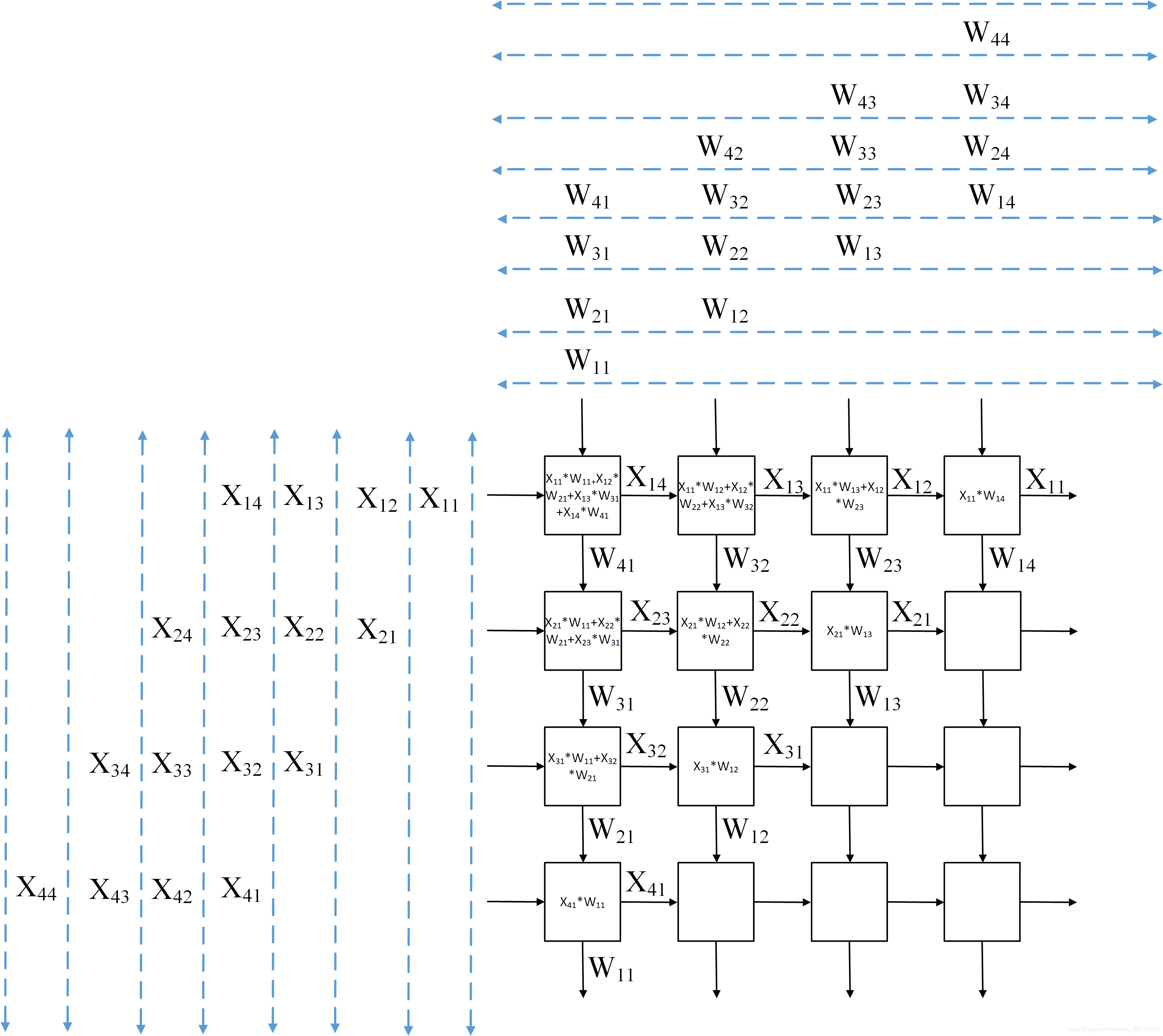

Step3:

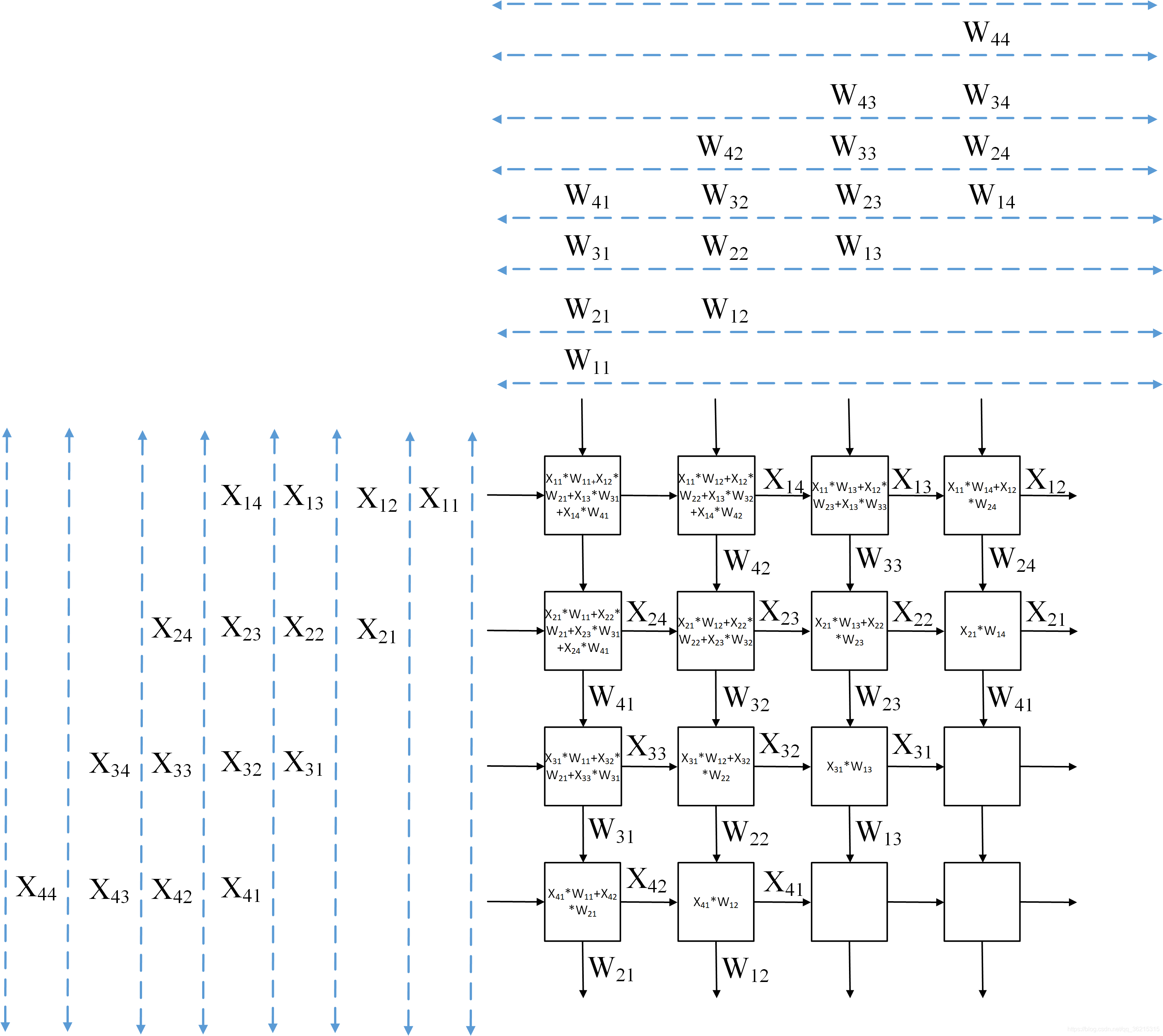

Step4:

Step5:

Step6:

Step7:

Step8:

Step9:

Step10:

- 方法总结

这两种方式大同小异,只是选择固定和流动的数据不一样。基本上,就是在W, X, Y三个变量中固定其中一个在PE单元,其余的两个数据在脉动阵列中进行传递。

3. 脉动阵列的特点

- 每一个节点(PE)都是相同的,但个别也可以不同。

- 每个PE只与其邻近的PE进行通信,PE之间的通信具有局部性,而且通信是规则的。

- 每个PE都有其局部的储存器,也就是PE的某些边带有延时,延时在硬件上对应于寄存器。

- 所有PE由统一的时钟同步工作。

- 以上特点造成PE之间的高度流水化、规则化,因此系统吞吐率非常大且易于VLSI的实现。

4. 脉动阵列性能评估

当矩阵为X m , l X_{m,l}Xm,l,W l , n W_{l,n}Wl,n,Y m , n Y_{m,n}Ym,n时,可得到下面结果。

- 所需PE阵列数目:m ∗ n m*nm∗n

- 计算时间内积步表示: n + m + l − 2 n+m+l-2n+m+l−2

- 计算效率:E p = 1 n ( m + n + l − 2 ) E_p=\frac{1}{n(m+n+l-2)}Ep=n(m+n+l−2)1

5. 参考文献

1: H. T. Kung, "Why systolic architectures?"