一、要求

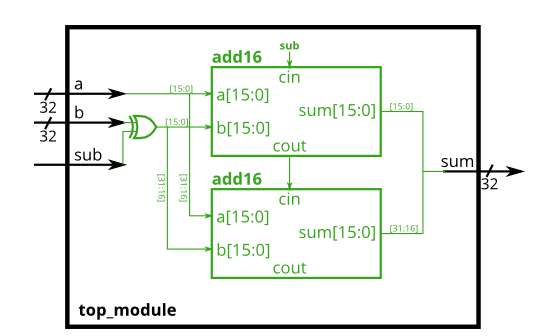

用16位的加法器设计一个加法器,减法器。当sub为1时,是减法;当sub为0时是加法。

二、原理

- 当sub为1的时候:

第一个加法器的进位输入为1,经过异或门,将b和sub按位取异或其实是将b按位取反,相当于进行的运算是: a + ~b + 1,得到的结果就是a-b。

- 当sub为0的时候:

第一个加法器的进位输入为0,经过异或门,将b和sub按位取异或,b的人值不变。相当于进行的运算是: a + b + 0,得到的结果就是a+b。

代码

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0]sum

);

wire [31:0]xor_1;

wire [15:0]sum_1;

wire [15:0]sum_2;

wire cout_1,cout_2;

//xor xor_gate(xor_1,b,sub);//逻辑或,我们这里的设计不应该是逻辑或,应该是下边的按位取或

assign xor_1 = b^{32{sub}} ;//按位异或

assign sum = {sum_2,sum_1};

add16 u1_add16(

.a(a[15:0]),

.b(xor_1[15:0]),

.cin(sub),

.sum(sum_1),

.cout(cout_1)

);

add16 u2_add16(

.a(a[31:16]),

.b(xor_1[31:16]),

.cin(cout_1),

.sum(sum_2),

.cout(cout_2)

);

endmodule

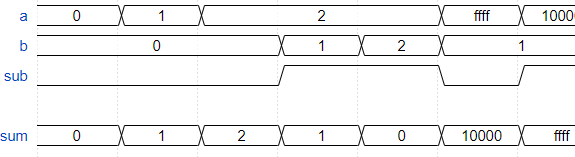

四、仿真波形

可以看出,当sub为0时,结果为a+b;当sub为1时,结果为a-b;

版权声明:本文为yang_jiangning原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。