FPGA学习笔记

AMBA总线2

1. APB简介

2. ASB简介

3. 对比

AMBA总线2

1. APB简介

APB(AMBA外设总线,the Advanced Peripheral Bus) 是本地二级总线(local secondary bus),主要用于低带宽的,低功耗的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB桥。

其特性包括:2个clockcycle传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号,不需要arbiter,以及一些request/grant信号。

APB桥将来自AHB/ASB的信号转换为合适的形式以满足挂在APB上的设备的要求。APB桥要负责锁存地址、数据以及控制信号,同时要进行二次译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

APB的总线信号经改进后全和时钟上升沿相关,这种改进的主要优点如下:

更易达到高频率的操作

性能和时钟的占空比无关

STA 单时钟沿简化了

无需对自动插入测试链作特别考虑

更易与基于周期的仿真器集成APB传输过程:

① 系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

② 当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。

③ 系统进入ENABLE状态时,维持之前在SETUP 状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。

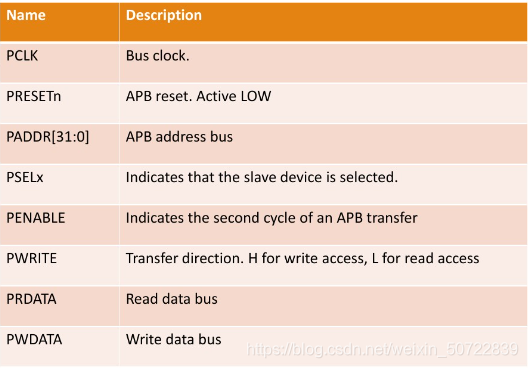

④ 传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。信号描述

Write transfer 写传输

需要2个clock cycle

第1个clock cycle:SETUP cycle

第2个clock cycle:ENABLE cycle

传输过程中,address/control/data信号都不变

传输结束后,PENABLE一定会变0

若接下来无其他transfer, address/write信号维持不变。Read transfer 读传输

除PWRITE=0外,其他的address/select等信号与write transfer时一样。

在读传输时,slave必须在ENABLE cycle给APB bridge 提供data,以便最后采样。

APB Slave 与APB Bridge在设计APBslave时,可以选择在以下两种情况latch write data:

① PSEL=1时的任何一个cycle

② PSEL=1时,PENABLE的上升沿

Read data,可在PWRITE = 0, 而PSEL=1, PENABLE =1时,去drive read data bus。

2. ASB简介

ASB(AMBA系统总线,the Advanced System Bus),是第一代AMBA系统总线,同AHB相比,它数据宽度要小一些,它支持的典型数据宽度为8位、16位、32位。适用于连接高性能的系统模块。它的读/写数据总线采用的是同一条双向数据总线,可以在某些高速且不必要使用AHB

总线的场合作为系统总线。可以支持处理器、片上存储器和片外处理器接口及与低功耗外部宏单元之间的连接。主要特征:

流水线方式

数据突发传送

多总线主设备

内部有三态实现

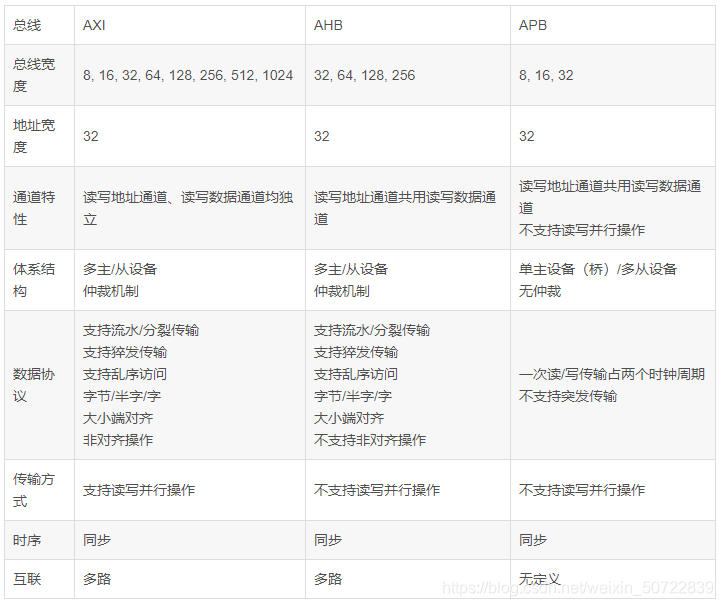

3. 对比

[参考资源] https://wenku.baidu.com/view/382b16a1cc1755270622087d.html

【注】:个人学习笔记,如有错误,望不吝赐教,这厢有礼了~~~