1、GPIO外设

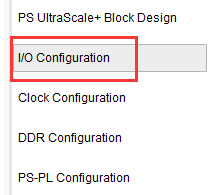

1)EMIO

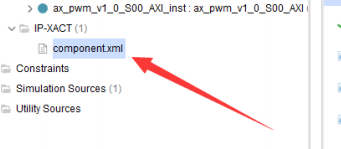

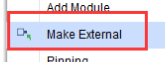

部分寄存器参考UG1085,BAKN0-BANK2为MIO78个,BANK3-BANK5 EMIO(扩展接口,再PL端)96个,IO配置里设置EMIO,生成cpu核上点击多出的GPIO_0端口右键选择Make External,将端口信号导出。点击引脚并修改引脚名称。保存设计。

![]()

打开vitis软件,建立工程,通过example进行设置,找到对应EMIO号,调整软件设计,再生成文件下载。

![]()

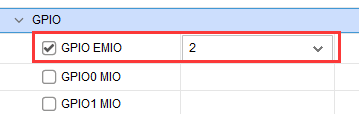

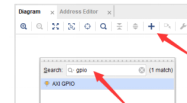

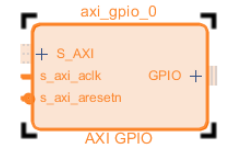

2)AXI_GPIO IP核

vivado的block工程,新增一个GPIO的IP核,双击的“axi_gpio_0”配置参数,设置宽度,勾选enable dual channel可以设置GPIO2

![]()

![]()

点击“Run Connection Automation”,可以完成部分自动连线,选择要连接的端口,点击OK

![]()

![]()

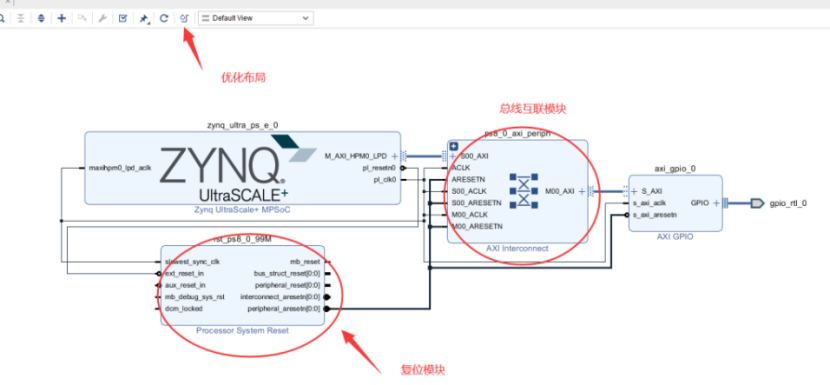

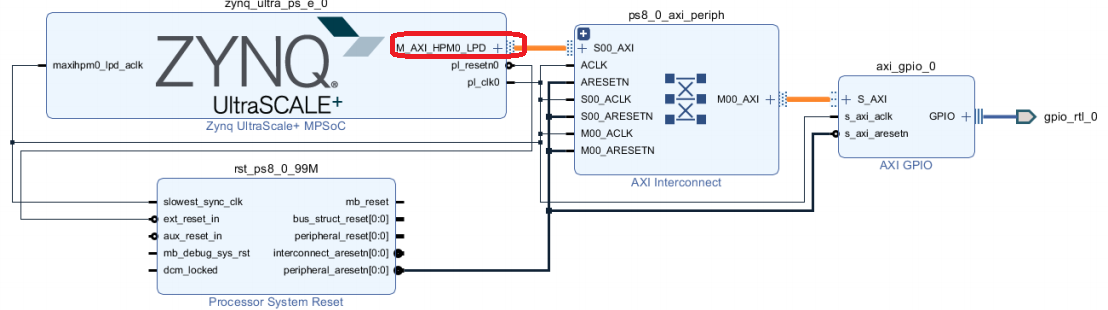

点击“Optimize Routing”,优化布局,此时多了两个模块,一个是 Processor System Reset模块,提供同一时钟域的复位信号。另一个是AXI Interconnect 模块 为AXI总线互联模块,用于AXI 模块的交叉互联。出现了ZYNQ的 HPM0_LPD 口,此总线为PS访问 PL 端数据,复位信号由ZYNQ 的复位输出提供,最好是每个时钟域都加一个复位模块,可以根据模块下面的名称搜索添加IP核。

点击多出的GPIO端口右键选择Make External,将端口信号导出,在框中修改名称,

上面设置一个IP核一个端口,可以多个设置IP核增加不同的GPIO,如果需要连接外部中断,受灾在GPIO核上勾选使能中断,再双击CPU核,增加PL-PS的设置中断。用线互联

![]()

![]()

![]()

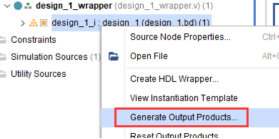

保存设计,点击xx.bd,右键Generate Output Products

注意查看生成的Verilog文件,看名字,要与约束文件中名字一致,点击generate,生成应硬件文件导出,打开vitis。

2、自定义IP

vivado里点击菜单“Tools->Create and Package IP...”挂在AXI4上,设置名称核存储位置。

![]()

![]()

需要修改IP,选择IP,右键Edit in IP Packager,可以填写工程名称和路径,这里默认,点击“OK”此时Vivado 又另外打开了一个新的工程, 添加核心代码(add source)。

![]()

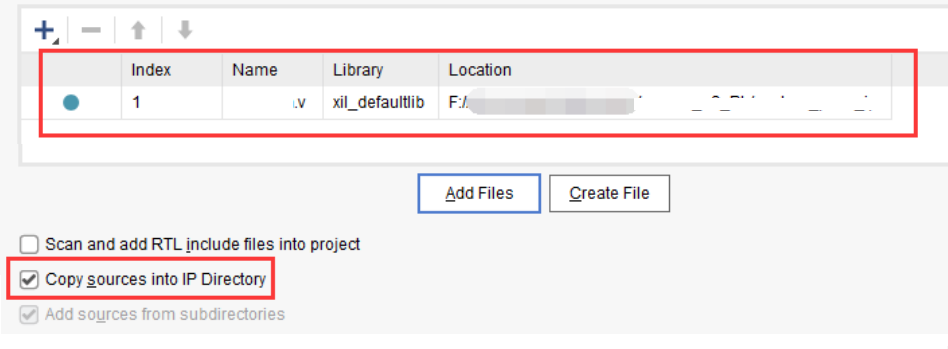

新建或者添加已有的代码

顶层文件内添加一个输出口,下面代码中在例化“ax_XX_V1_0_S00_AXI”,中添加要输出端口的例化,修改“ax_xx_v1_0_s00_AXI.v”文件,添加 相同输出端口,这个文件是实现AXI4 Lite Slave

![]()

![]()

![]()

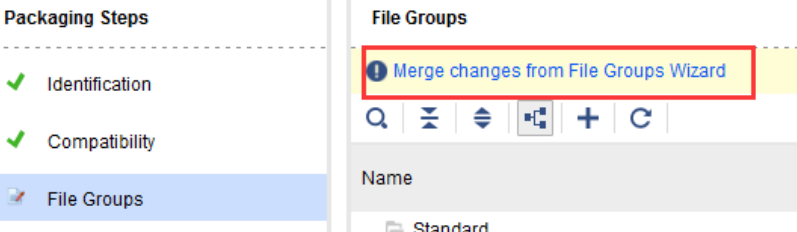

双击“component.xml”文件,找到没有对号的file groups栏,点击merge changes from groups wizard,在“Customization Parameters”选项中点击“Merge changes form Customization Parameters(没有对号都点一遍)

![]()

点击“Review and package”里的“Re-Package IP完成 IP的修改

添加自定义IP 到工程,点击“+”,搜索IP名称,双击,弹出框,点击Run Connection Automation,自动完成连接。导出输出端口,保存设计,并Generate Output Products

![]()

添加xdc文件分配管脚,与硬件上一致,编译生成 bit 文件,导出硬件