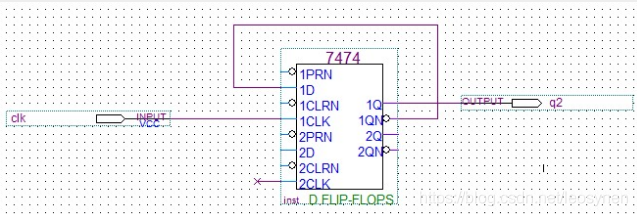

将D触发器的D端连接D触发器的输出QN端,就构成了一个由D触发器形成的2分频电路。多个D触发器级联得到4、8、16分频。

代码如下所示:

module D_ff_4div(clkin,reset_n,clkout);

input clkin,reset_n;

output clkout;

wire in1,in2,clkin_2;

reg out;

reg clkout_1;

assign in1=~clkout_1;

assign clkin_2=clkout_1;

assign in2=~out;

assign clkout=out;

always@(posedge clkin) //由第一个D触发器构成的2分频程序;

begin

if(!reset_n)

begin

out<=0;

clkout_1<=0;

end

else

clkout_1<=in1;

end

always@(posedge clkin_2) //由第二个D触发器构成的2分频程序,时钟输入为上面的输出;

begin

if(!reset_n)

out<=0;

else

out<=in2;

end

endmodule

版权声明:本文为leosynen原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。