提示:以下是本篇文章正文内容,下面案例可供参考

Module

1.连接信号到Module

//第二种写法是更加提倡的,因为这样会更加清楚对应关系

module_a u_name(a,b,c);

module_a u_name(.in1(a),.in2(b),.out(c));

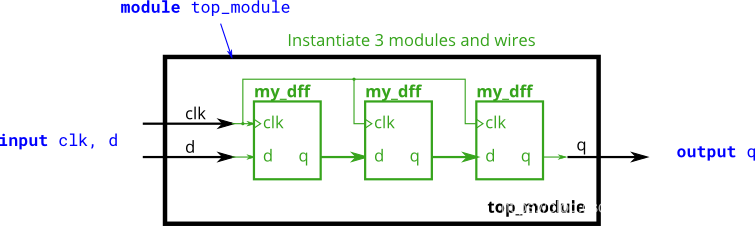

2.实例化多个module

//注意到连接各个模块的时候需要使用到wire来连接

//如果是并联连接就不需要如此麻烦

module top_module ( input clk, input d, output q );

wire wire1,wire2;

my_dff u_my_dff1(.clk(clk),.d(d),.q(wire1));

my_dff u_my_dff2(.clk(clk),.d(wire1),.q(wire2));

my_dff u_my_dff3(.clk(clk),.d(wire2),.q(q));

endmodule

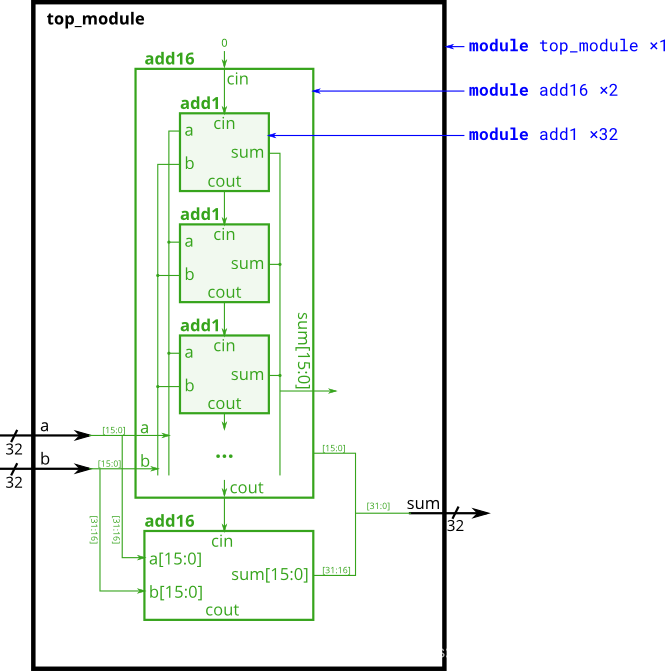

3.模块嵌套调用

//通过嵌套模块来实现32位加法器

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

//module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

wire cin1,cout1,cout2;

wire [15:0] sum1,sum2;

assign cin1 = 0;

add16 u_add16_1(.a(a[15:0]),.b(b[15:0]),.cin(cin1),.sum(sum1),.cout(cout1));

add16 u_add16_2(.a(a[31:16]),.b(b[31:16]),.cin(cout1),.sum(sum2),.cout(cout2));

assign sum = {sum2,sum1};

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

always @(*)begin

if(cin == 0)

begin

if(a == 1 && b == 1)

begin

cout = 1;

sum = 0;

end

else

begin

cout = 0;

sum = a+b;

end

end

else

begin

if(a == 0 && b == 0)

begin

cout = 0;

sum = 1;

end

else

begin

cout = 1;

sum = ~(a^b);

end

end

end

// Full adder module here

endmodule

版权声明:本文为qq_37858023原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。