序:

本篇内容,基于阅读J. Bhasker • Rakesh Chadha著作《Static Timing Analysis for Nanometer Designs》后进行的总结以及自己的观点和感想,如有不正确的地方,还请指点。读者有微电子基础将更好理解内容。(图片内容绝大部分直接引用书中)

写到这里的时候,发现有人对全本书都进行过翻译。有点想放弃了,但是转念一想,自己何不也写一遍,对比别人单纯翻译的,应该会有更加深入的理解把。

Standard cell library

本章节主要介绍library cell中的时序信息,这个cell可以是standard cell, an IO buffer, or a complex IP such as a USB core. 库单元的描述不仅仅包括时序信息,还有面积和功能等属性。这些虽然和时序无关,但是和综合阶段有关。本章节主要介绍时序和power相关的计算。

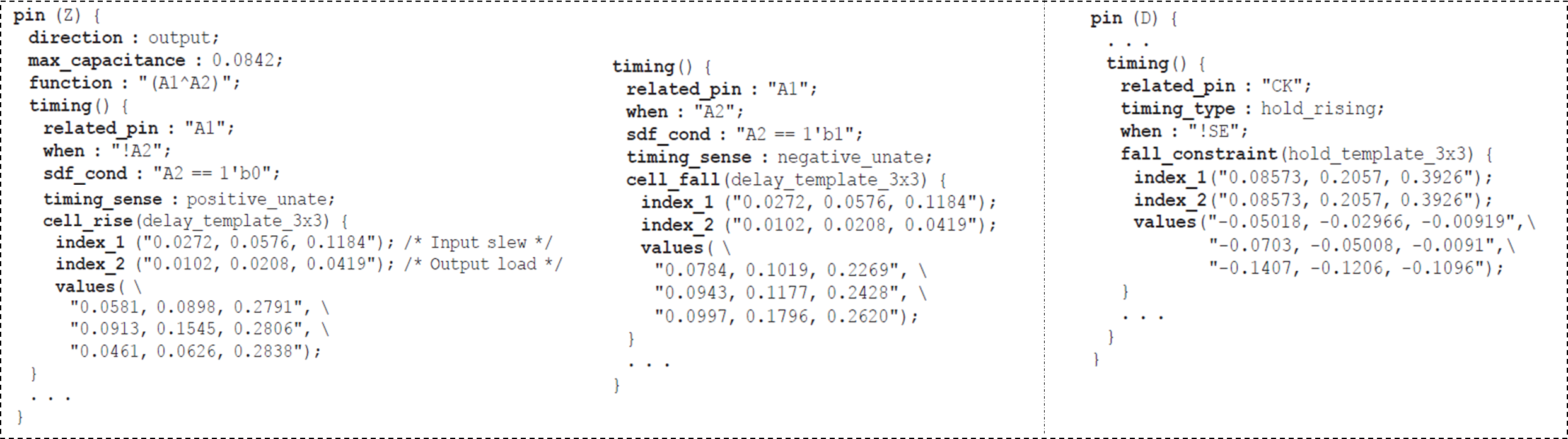

4. State-Dependent Models

很多的组合逻辑cell ,输入和输出之间的timing arcs取决于其中某些引脚的逻辑状态,状态决定了输入和输出之间是positive还是negative或者是non的单边类型。比如二输入的xor/xnor单元,一个引脚确定了,那么另一个输入引脚于输出之间的timing arcs状态就可以确定。这种有多个输入引脚且timing arcs类型取决于输入引脚的时序类型叫做状态相关模型。

如下如左侧所示,为一个组合逻辑,二输入异或门单元。如库中描述,当A2为0时,A1到Z的timing arc为正单边类型,cell rise的值取决于input rise trans和output load。当A2为1时,A1到Z的timing arc为负单边类型。使用“when”来指定和状态相关的条件。同理也会有A1为0或者1时,从A2到Z端的时序模型。sdf_cond指定生成sdf时候相应的时序弧条件。

状态时序模型还应用于时序单元,许多时序单元会使用状态相关的时序模型指定建立时间或保持时间的时序约束。上图右侧为时序单元的时序模型描述,使用装态相关的时序模型进行保持时间约束的scan DFF。当SE为有效状态时候,有一组hold timing 的模型,当SE为无效状态时候,有另外一组。需要注意,如果对于hold timing的状态时序模型描述不包含单元的某个状态,则选用非状态相关的时序模型的保持时间。如果没有用于描述保持时间的非状态时序模型,那么timing arc将没有hold time。另外,可以为时序库中单元的任何属性指定状态相关模型,如leakage_power, cell_rise等等。

5. Interface Timing Model for a Black Box

本小节介绍black box的IO接口时序弧,前面有讲到reg2reg的timing arc,IO接口的时序弧有三类:

- 输入端口到输出端口的组合逻辑时序,FIN2FOUT

- 输入端口到reg的时序,

- reg到输出端口的时序

另外还有异步输入时序,如输入端口ARST到UFF0的异步清零引脚,这类似于recovery 和removal time check。除了时序外,black box的外部时钟引脚上还可以进行min pulse check。此外还可以定义内部节点,并在这些内部节点上定义generated clock,从而指定在这些节点之间的时序弧。这种时序,常常见于在一个大的chip里面,对其中一个小的blk进行sta check,那么blk的引脚出就是IO引脚。

6. Advanced Timing Modeling

NLDM,时序取决于输入tran time和输出负载电容。实际的单元输出负载不仅仅包括电容,还有电阻。NLDM的使用是忽略了输出电阻的情况,把输出符在当作了纯的电容。这种模型使用于输出无电阻(基本不可能)以及输出电阻很小可以忽略不记的情况。当存在的电阻不可忽略的时候,通过“有效”电容法获得等效的电容从而保证单元输出延迟与具有RC互联的单元延迟相同的改进NLDM模型。

但是随着特征尺寸的不断缩小,时序波形变得高度非线性,互联电阻会导致较大的不准确性。各种建模方法为单元输出驱动器提供了额外的精度。 从广义上讲,这些方法通过使用等效电流源对驱动器的输出级进行建模来获得更高的精度。 这些方法的示例是 - CCS(复合电流源)或 ECSM(有效电流源模型)。 例如,CCS 时序模型通过使用随时间变化和电压相关的电流源为单元输出驱动器建模提供了额外的精度。 通过指定接受引脚电容和不同场景下输出充电电流的详细模型来提供时序信息。 接下来描述 CCS 模型的细节。

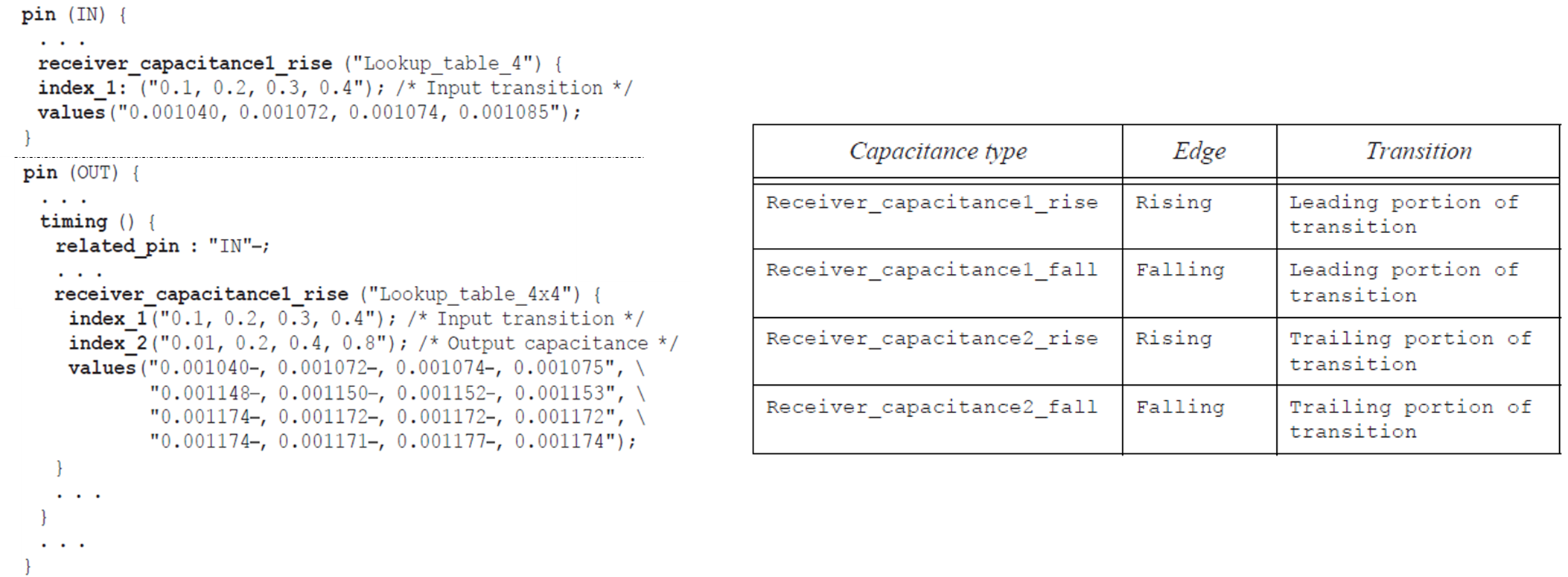

6.1 Receiver Pin Capacitance

receiver pin cap对应NLDM模型中的输入引脚电容。和NLDM模型中引脚电容不同的是,CCS model允许在trans 波形的不同位置对receiver pin cap的定义。由于互连 RC 和密勒效应引起的等效输入非线性电容,接收器电容值在转换波形上的不同点发生变化。因此电容在波形的inital部分和trailing部分被分别建模。接受引脚电容可以指定为pin level的,也可以指定为timing arc levle的。pin level就像NLDM中的一样,所有通过这个pin的时序弧都使用这个电容值,而timing arc level指的是为不同的timing arc指定不同的电容模型。

下图左上,pin(IN)为pin level,index1指定了input trans,cap与其线性相关。下图左下pin(OUT)为timing arc level。根据input trans和output cap以二维表格的形式来指定。输入引脚IN上波形初始部分(这个怎么判断的呢,是那个‘-’判断的吗????)的接收引脚上升电容,该电容取决于输入引脚IN上的过渡时间和输出引脚OUT上的负载。上图右侧总结了四种不同类型的receiver cap 类型。当然可以在pin level将他们指定为一维表格,或在timing arc level将他们指定为二维表格。

6.2 Output Current

ccs模型中,非线性时序表现为输出电流大小。输出电流是一个input trans和output load元素组合决定的。给定一个index_1: input trans和index_2: output cap,对应得到values这个电流波形,其实是一堆值得合集。那么应该选择哪个值呢,由index_3 时间值决定。如下为output current fall的模型。

reference_time 指的是输入波形越过延迟阈值的时间。综上所述,对于给定一个input trans和output cap,输出电流波形是时间的函数。类似的还有output_current_rise。

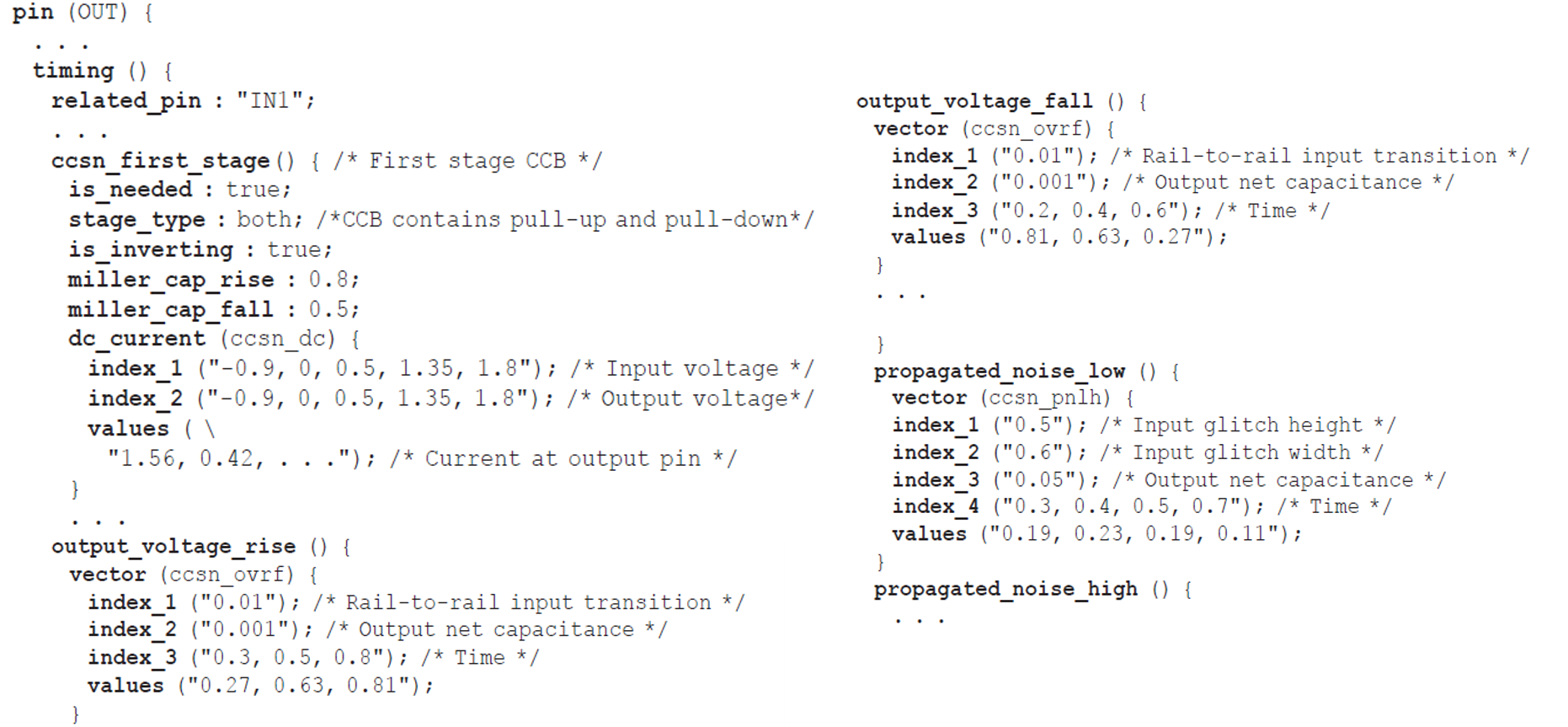

6.3 Models for Crosstalk Noise Analysis

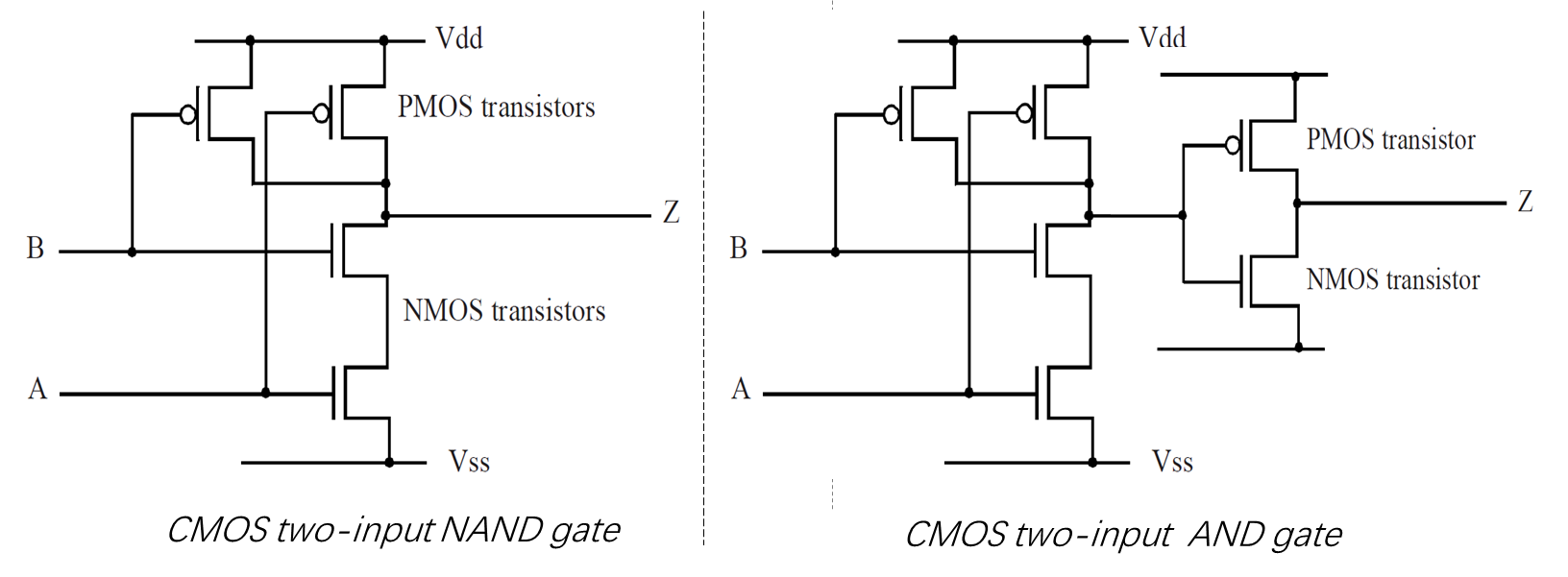

CCSN(CCS Noise) 模型,用于分析corsstalk noise(or glitch)的ccs模型。CCS Noise 模型是结构性模型,用于描述单元内不同的Channel connected blocks(CCB)。CCB指的是的是单元源漏沟道连接部分。例如单级单元像inverter,Nand和nor只包含一个CCB(整个单元只用一个沟道区进行连接)如下图左侧,多级的cell如and/or cells,包含多个CCB,如下图左侧所示。

通常,只对cell input drive的第一级CCB和drive cell output的最后一级CCB进行CCSN模型的描述。通过稳定状态电流,输出电压和传播噪声模型进行描述。对于单级的组合逻辑单元如nand和nor,CCS模型会对所有的timing arc进行描述。这些cell只有一级CCB,因此模型描述是从输入到输出。

如下所示为一级CCS noise model例子。ccsn_first_stage表明这是nand cell的第一级CCB。因为nand cell只有一级CCB,所以is_needed几乎始终为true(除了antenna cell这种非功能性的cell)。stage_type中的both表示改级CCB同时具有上拉和下拉结构。miller_cap_rise/fall分别表示输出上升和下降时的miller 电容值。dc_current 值的是输出直流电流随着输入和输出电压的变化情况。电压和电流的单位通常为V和mA,在库中指定。对于与非门IN1到OUT的CCS noise 模型示例,当输入电压为-0.9v,输出电压为0v时,根据查找表输出直流电流为0.42mA。output_voltage_rise/fall分别包含CCB输出上升和下降的delay信息。index_1指定了rail-to-rail的input trans,index_2指定了output cap,index_3 指定超过阈值电压的百分比(0.9v的30%,70%,90%)。那么delay就是时间的函数。在每个多维表格中,电压交叉点(voltage crossing points)都是固定的。p’ropagated noise,propagated noise high/low模型通过指定多维表格提供了噪声的传播信息。这些模型表征了串扰噪声/毛刺从CCB的输入到输出的传播。表征时,输入使用了对称三角波。模型包括了index_1:输入毛刺幅值,index_2: 输入毛刺宽度,index_3: CCB输出电容,index_4: 时间,value指定了CCB输出电压(或者称为通过CCB传播的 噪声)

二级单元的噪声模型,于一级单元的一样,其CCS噪声模型通常被描述为时序弧的一部分。由于这些单元包含两个CCB,因此在库中的描述分别需要ccs_first_stage/ccsn_last_stage分别指定前后两级。这两级的的噪声模型分别独立。

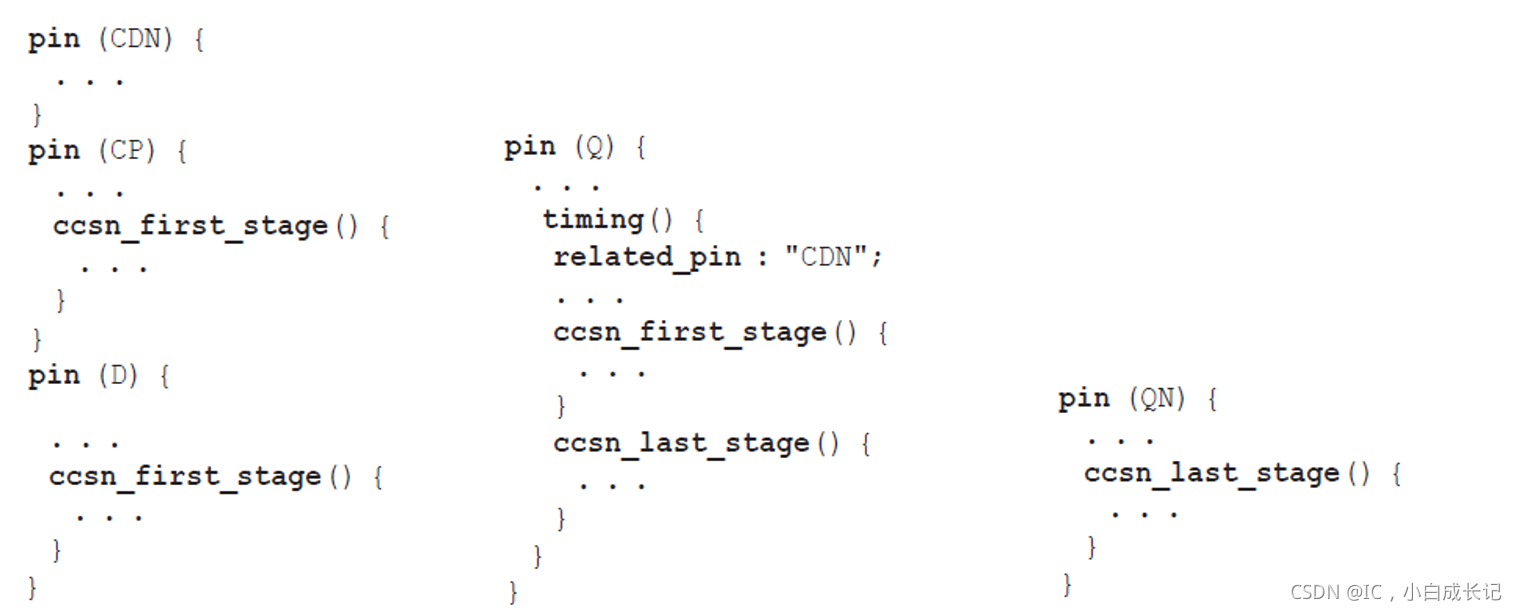

多级单元和时序单元的噪声模型:复杂的组合逻辑单元或者时序单元的CCS噪声模型通常描述为引脚中一部分内容。而前面提到的单级或者二级单元的CCB 噪声模型,通常在一对引脚上描述,作为时序弧的一部分。复杂的多级和时序单元通常由所有输入引脚的 ccsn_first_stage 模型和输出引脚的另一个 ccsn_last_stage 模型描述。 这些单元的 CCS 噪声模型并不描述为时序弧的一部分,而是为引脚指定。通常,多级单元描述可以将一些 CCS 噪声模型指定为引脚对时序弧的一部分,而其他一些噪声模型可以通过引脚描述指定。如下图所示:

请注意,上面触发器单元的一些 CCS 模型是通过引脚定义的。 那些通过引脚描述的输入pin指定为 ccsn_first_stage,输出引脚 QN 的 CCS 模型被指定为 ccsn_last_stage。 此外,两级 CCS 噪声模型被描述为 CDN 到 Q 的时序弧的一部分(此处的两级应该是什么?)。因此,此示例表明单元可以将 CCS 模型指定为引脚描述的一部分和时序组的一部分。