matlab中产生FIR滤波器和测试数据并导入到FPGA中仿真。

1.生成测试数据。采样率fs=20MHZ,正弦信号f0=1MHZ,f1=4MHZ.matlab代码如下:

fs=20e6;

f0=1e6;

f1=4e6;

N=16;

t=1/fs:1/fs:1;

%s=simout(1:500:length(simout));

s0=sin(2*pi*f0*t);

s1=sin(2*pi*f1*t);

s=s1+s0;

s=s(1:10240); %%截取10240点方便导入FPGA

ss=s/max(abs(s));

fss=20*log10(abs(fft(ss)));

sss=fss-max(fss);

%x=0:length(sss)-1;

x=1:length(sss)-1;

sss=sss(1:(length(sss)-1));

x=x/length(x)*fs;

plot(x,sss);

Q_si=round(s*(2^(N-1)-1));

fid=fopen('F:\shuzixinhao\fir_test1\fir_xs.txt','w');

for i=1:(length(s))

B_si=dec2bin(Q_si(i)+(Q_si(i)<0)*2^N,N);

for j=1:N

if B_si(j)=='1'

tb=1;

else

tb=0;

end

fprintf(fid,'%d',tb);

end

fprintf(fid,'\r\n');

end

fprintf(fid,';');

fclose(fid);

2.FIR滤波器使用FDATOOL产生。具体的采样率20MHZ,Fpass=2MHZ,Fstop=6MHZ.导出到工作区。

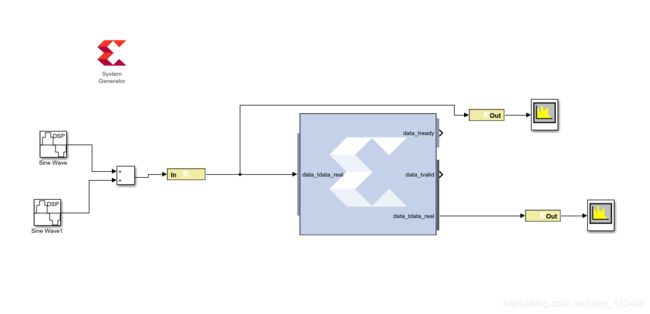

3.使用simulink搭建FIR滤波器仿真。

(1)sine wave模块:使用的是Dsp System ToolBox-->Sources中的,两个sine的Freq分别是1E6,4E6,sample time=1/20e6.

(2)system generate模块:FPGA clock period=50ns(20MHZ),

UG948.pdf中:

The current design samples the input at a rate of 20 MHz. If the input is sampled at 6 times the

current frequency, it is possible to perform all calculations using a single multiplier.

如果FPGA clock period=8.33ns(120MHZ),sample time=1/20e6,那么在FPGA使用该FIR,乘法器资源可以减到原来的1/6.

4.FPGA中导入matlab文件数据并仿真:

module sim_test(

);

reg clk,rst;

reg[15:0] din;

wire[33:0] dout;

initial begin

clk=1'b0;

forever #25 clk=~clk;

end

initial begin

rst=1'b1;

#200 rst=1'b0;

end

reg[15:0] mem[10239:0];

integer i;

initial begin

$readmemb("G:\ex_digital_signal\fir_xs.txt",mem);

i=0;

#400;

repeat(10239)begin

i=i+1;

din=mem[i];

$display("Memory[%d]=%b",i,din);

#50;

end

end

fir_test1 fir_test1(

.clk (clk),

.rst (rst),

.din (din),

.dout (dout)

);

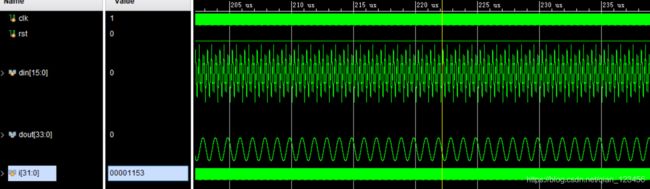

仿真波形:

输入信号的1M+4M的波形,dout是滤波后的1MHZ波形。

vivado数据导入到matlab中网上的方法: