目录

Verdi所用的.fsdb文件(打开-kdb和-fsdb选项)

VCS,QuestaSim均是FPGA常用仿真软件,下文将分别介绍这两款软件的使用流程及相关命令。

VCS

仿真流程包括Analysis,Elaboration和Simulation。

Analysis

作用:

编译文件(vhdl,verilog,system verilog等),检查语法错误,生成中间文件;

命令:

vhdlan [vhdlan_options] file1.vhd file2.vhd % vhdl files

vlogan [vlogan_options] file1.v file2.v % verilog files

vlogan -sverilog [vlogan_options] file1.sv file2.sv file3.v % system verilog files

常用编译选项:

-full64:64bit模式去做编译;

-work library:将所用的library映射到WORK库,如altera ip的library;

-l compile.log:指定编译所产生的log文件路径;

-f filelist:指定某一类型文件的filelist;

-timescale=time_unit/time_precision:指定仿真时间单位和精度,仅限于vlogan;

-vhdl08:指定vhdl语言版本,仅限于vhdlan;

-optimize:减少部分vhdl的检查来改善仿真性能(如下),缩减仿真时间,仅限vhdlan;

缺省算数溢出见检查(Arithmetic overflow)

缺省约束检查(Constraint checks)

缺省数组赋值大小兼容性检查(Array size compatibility at assignment)

缺省下标越界检查(Subscripts out of bounds)

缺省整数负指数检查(Negative exponents to integer)

-no_opt:不采用优化(optimize)选项,全检查;

-kdb:生成Verdi KDB数据库;

-smart_order:自动识别文件的依赖关系,filelist的文件顺序可以任意放置,仅限vhdlan;

Elaboration

作用:

构建实例层级,生成二进制可执行文件;

命令:

vcs [elab_options] [libname.]design_unit

libname:module/entity所在的库名,可省略;

design_unit:top module/entity/configuration name;

常用选项:

-licqueue:如果license不可用则保持等待状态,直至license可用;

-full64:使用64bit mode;

-file filename:指定包含elaboration选项的文件;

-gui:使用GUI的方式仿真;

-l elab.log:指定elaboration所产生的log文件路径;

+notimingcheck:忽略设计时序检查;

-override_timescale=time_unit/time_precision:指定仿真时间单位和精度;

-kdb:生成Verdi KDB数据库;

-notice:显示详尽的诊断信息;

-debug_acess+option:指定调试模式,常用:-debug_acess+pp,-debug_acess+all +vcs+dumpvars:指定VCD文件,相当于$dumpvars函数;

+vcs+vcdpluson:相当于$vcdpluson函数;

-suppresses message_ID:屏蔽一些告警信息的显示;

-error message_ID:屏蔽一些错误信息的显示;

-lca:使用“VCS限制用户使用功能”

Simulation

作用:

运行二进制可执行文件,启动仿真,支持interactive模式和batch模式;

interactive模式支持两种使用方式:1)GUI上启动仿真:simv -gui

2)DVE打开波形文件:dve -vpd vpdfile_name

命令:

executable [runtime_options] %executable为可执行文件,一般默认为simv

常用选项:

-gui=dve:打开DVE GUI界面,启动仿真;

-gui=verdi:打开Verdi GUI界面,启动仿真;

+vpdfile+filename:指定VPD文件的名字;

+ntb_random_seed=value:设置随机变量的种子;

-reportstats:捕获CPU的运行数据;

-ucli:启用ucli命令行模式如:simv -ucli -do dump_vpd.tcl,dump_vpd.tcl如下;

dump_vpd.tcl dump -file tb_top.vpd -type VPD dump -add tb_top -aggregates -fid VPD0 run-debug_pp:推荐生成VCD/VPD 文件的最佳配置,综合考虑debug性能和时间;

-debug:debug能力好于debug_pp,花费时间长;

-debug_all:最好的debug性能,花费时间最长;

(类似于+debug_access+options)

VCS生成波形文件(debug模式)

DVE所用的.VPD文件

1) 使用Verilog System Tasks生成

在testbench加入如下代码

initial begin $vcdplusfile("tb_top.vpd"); $vcdplusonend end2)添加选项命令生成

Elaboration:+vcs+vcdpluson

Simulation:+vpdfile+sim.vpd(不指定名字,默认vcdplus.vpd)

3)使用UCLI方式:仿真选项中加入-ucli -do dump_vpd.tcl

dump_vpd.tcl:

dump -file tb_top.vpd -type VPD dump -add tb_top -aggregates -fid VPD0 run打开波形文件:dve -vpd tb_top.vpd

Verdi所用的.fsdb文件(打开-kdb和-fsdb选项)

1)使用使用Verilog System Tasks生成

在testbench中加入如下代码:

2)使用UCLI方式:仿真选项中加入-ucli -do dump_fsdb.tclinitial begin $fsdbDumpfile("tb_top.fsdb"); $fsdbDumpvars(0,tb_top); enddump -file tb_top.fsdb -type FSDB dump -add tb_top -aggregates -fid FSDB0 run打开波形文件:verdi -ssf tb_top.fsdb -nologo

Questa SIM

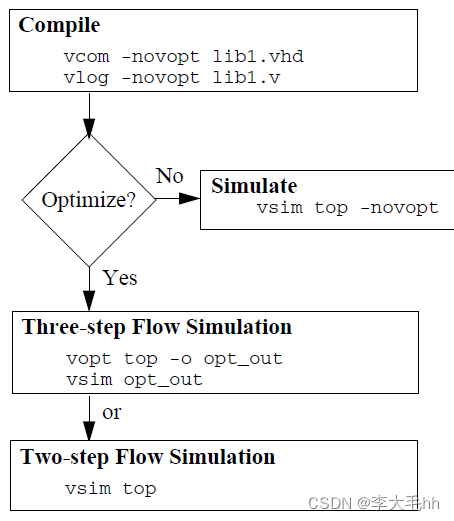

核心流程包括Compile,Optimization(可选),Simulation。

Compile

命令:

vlog [options] <filename> <filename>... % verilog,system verilog files

vcom [options] <filename> <filename>... % vhdl files

常用选项:

-64:使用64bit模式编译;

-2008:指定VHDL语言版本,仅限于vcom;

-l:指定生成的log路径;

-f:指定编译文件的filelist;

-work library name:将编译目标编译到指定库中;

-novopt:编译时不作优化;

-lint:编译时作语义检查,如访问数组的范围越界等;

-quiet:过滤一些加载库的信息,使得log信息更简洁;

-incr:增量编译,只编译相对上次编译有改动的文件,仅限于vlog;

-timescale=time_unit/time_pre:指定仿真时间单位和精度;

-cover:使能覆盖率检查;

Optimization(可选非必要)

命令:

vopt [options] testbench_name -o executable_name

常用选项:

+acc :保留仿真中某个模块的可见性;

+acc:所有的模块都可见;

+acc+mod1:mod1模块可见;

-override_timescale=1ns/1ns:重覆盖仿真时间单位和精度;

-incr:增量优化;

-L library:指定提前编译好的库;

Simulation

命令:

vsim [options]

常用选项:

+notimingchecks:不进行时序检查;

-lib libray_name:指定包含编译目标的库文件;

-solvefaildebug=value:使能随机化失败调试,如果value省略,则使能基本调试功能;

-do "<command_string>" | do_file_name:传入并执行tcl命令或者脚本文件;

-f filename:传入带有仿真选项的文件,可在仿真过程中解析并采用这些仿真选项;

-batch/-c/-gui/-i/:采用不同的工作模式;

-batch:后台模式,-c:命令行模式,-gui:用户界面模式,-i:交互模式。

-sv_seed <integer>| random:用于指定仿真时的随机种子

-wlf <file_name>:指定保存的保存文件,默认输出vsim.wlf;

-coverage:使能覆盖率收集,但要求编译时添加+cover选项;

Questa生成波形文件

QuestaSim使用的wlf文件

Testbench中加入:

initial begin $wlfdumpvars(); end打开波形文件: vsim vsim.wlf

Makefile及tcl文件

#Makefile #!/bin/sh .PHONY: default default: all SIM_TOOL=$(shell echo $(tool)) VCS_VHDL_COMP_OPTS = -full64 VCS_VHDL_COMP_OPTS += -no_opt VCS_VHDL_COMP_OPTS += -kdb VCS_VHDL_COMP_OPTS += -vhdl08 VCS_VHDL_COMP_OPTS += -smart_order VCS_VERILOG_COMP_OPTS = -full64 VCS_VERILOG_COMP_OPTS += -timescale=1ns/1ps VCS_VERILOG_COMP_OPTS += -kdb VCS_ELAB_OPTS = -full64 VCS_ELAB_OPTS += -override_timescale=1ns/1ps VCS_ELAB_OPTS += +vcs+vcdpluson VCS_ELAB_OPTS += -debug_access+all VCS_ELAB_OPTS += +vcs+lic+wait VCS_ELAB_OPTS += -kdb VCS_ELAB_OPTS += -fsdb VCS_ELAB_OPTS += -lca VCS_RUN_OPTS = +ntb_random_seed=1 VCS_RUN_OPTS += +time_out=500 VCS_RUN_OPTS += -reportstats #VCS_RUN_OPTS += -ucli -do dump_vpd.tcl #VCS_RUN_OPTS += -ucli -do dump_fsdb.tcl VCS_RUN_OPTS += +vpdfile+simulation.vpd #VCS_RUN_OPTS += +fsdbfile+sim.fsdb QUESTA_VHDL_COMP_OPTS = -64 QUESTA_VHDL_COMP_OPTS += -2008 QUESTA_VHDL_COMP_OPTS += -work work QUESTA_VHDL_COMP_OPTS += +cover #QUESTA_VHDL_COMP_OPTS += -novopt #QUESTA_VHDL_COMP_OPTS += -lint #QUESTA_VHDL_COMP_OPTS += -quiet QUESTA_VERILOG_COMP_OPTS = -incr QUESTA_VERILOG_COMP_OPTS += -work work #QUESTA_VERILOG_COMP_OPTS += -novopt #QUESTA_VERILOG_COMP_OPTS += -lint #QUESTA_VERILOG_COMP_OPTS += -quiet #QUESTA_VERILOG_COMP_OPTS += +cover QUESTA_VOPT_OPTS = -incr QUESTA_VOPT_OPTS += -L work QUESTA_VOPT_OPTS += -work work QUESTA_VOPT_OPTS += -override_timescale=1ns/1ns QUESTA_VOPT_OPTS += +acc QUESTA_VOPT_OPTS += -novopt QUESTA_RUN_OPTS = -lib work QUESTA_RUN_OPTS += -solvefaildebug QUESTA_RUN_OPTS += -sv_seed 1 QUESTA_RUN_OPTS += -c #QUESTA_RUN_OPTS += -wlf sim.wlf QUESTA_RUN_OPTS += -do questa.tcl QUESTA_RUN_OPTS += +time_out=500 QUESTA_RUN_OPTS += -coverage COMP_LOG_DIR = comp_log ELAB_LOG_DIR = elab_log RUN_LOG_DIR = sim_log ifeq ($(SIM_TOOL), vcs) COMP_VHDL_CMD = vhdlan COMP_SV_CMD = vlogan -sverilog COMP_VHDL_OPTS = $(VCS_VHDL_COMP_OPTS) COMP_VERILOG_OPTS = $(VCS_VERILOG_COMP_OPTS) ELAB_OPTS = $(VCS_ELAB_OPTS) ELAB_CMD = vcs RUN_OPTS = $(VCS_RUN_OPTS) RUN_CMD = simv else COMP_VHDL_CMD = vcom COMP_SV_CMD = vlog COMP_VHDL_OPTS = $(QUESTA_VHDL_COMP_OPTS) COMP_VERILOG_OPTS = $(QUESTA_VERILOG_COMP_OPTS) ELAB_OPTS = $(QUESTA_VOPT_OPTS) ELAB_CMD = vopt RUN_OPTS = $(QUESTA_RUN_OPTS) RUN_CMD = vsim simv endif .PHONY: init init: mkdir -p $(COMP_LOG_DIR) mkdir -p $(ELAB_LOG_DIR) mkdir -p $(RUN_LOG_DIR) .PHONY: comp comp: @$(COMP_VHDL_CMD) $(COMP_VHDL_OPTS) -f tb_dsp_vhd.f -l $(COMP_LOG_DIR)/comp_dut.log @$(COMP_SV_CMD) $(COMP_VERILOG_OPTS) -f tb_sv.f -l $(COMP_LOG_DIR)/comp_tb.log .PHONY: elab elab: $(ELAB_CMD) $(ELAB_OPTS) tb_top -o simv -l $(ELAB_LOG_DIR)/elab.log .PHONY: sim sim: $(RUN_CMD) $(RUN_OPTS) -l $(RUN_LOG_DIR)/sim.log .PHONY: all all: clean init comp elab sim .PHONY: clean clean: -rm -r $(COMP_LOG_DIR) $(ELAB_LOG_DIR) $(RUN_LOG_DIR) -rm *.log *.rc *.conf *.sdb *.dump -rm *.wlf *.fsdb *.vpd -rm simv -rm -r 64 AN.DB DVEfiles simv.daidir work work.lib++ vhdlanLog ucli.key -rm -r csrc verdiLog fontconfigdump_vpd.tcl:

dump -file tb_top.vpd -type VPD dump -add tb_top -depth 0 -aggregates -fid VPD0 rundump_fsdb.tcl:

dump -file tb_top.fsdb -type FSDB dump -add tb_top -aggregates -fid FSDB0 run执行命令:make all tool=vcs %使用VCS

make all tool=questa %使用Questa

Testbench:tb_top.sv

`timescale 1ns/1ps

module tb_top;

logic clk;

logic reset;

logic [3:0] a;

logic [2:0] b;

logic [2:0] c;

initial begin

clk = 0;

reset = 1;

#100;

reset = 0;

#50;

@(posedge clk)

a = 6;

@(posedge clk);

end

always #5 clk = ~clk;

//initial begin

//$vcdplusfile("sim.vpd");

//$vcdpluson;

//end

//initial begin

// $wlfdumpvars();

//end

//initial begin

// $fsdbDumpfile("tb_top.fsdb");

// $fsdbDumpvars(0,tb_top);

//end

Saturate_top inst_Saturate_top(

.clk (clk),

.reset (reset),

.dataIn (a),

.dataOut_f1 (b),

.dataOut_f2 (c)

);

initial begin

integer time_out;

if(!$value$plusargs("time_out=%d",time_out)) begin

time_out=200;

$display("Info: Simulation timeout is %0d seconds", time_out);

end else begin

$display("Info: Simulation timeout is %0d seconds", time_out);

end

repeat (time_out) @ (posedge clk);

$display("Info: Simulation timeout");

$display("*********************************************************************");

$display("**************************SIMULATION FINISH**************************");

$display("*********************************************************************");

$finish;

end

endmodule;RTL:Saturate_top .vhd

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

LIBRARY work;

--------------------------------------------------------------------------------

--

-- Entity : Saturate_top

--

--------------------------------------------------------------------------------

ENTITY Saturate_top IS

PORT (

------------------------------------------------------------------------

-- Chip Inputs clock, reset

------------------------------------------------------------------------

clk : IN std_logic;

reset : IN std_logic;

dataIn : IN std_logic_vector(3 DOWNTO 0);

dataOut_f1 : BUFFER std_logic_vector(2 DOWNTO 0);

dataOut_f2 : BUFFER std_logic_vector(2 DOWNTO 0)

);

END ENTITY Saturate_top;

--------------------------------------------------------------------------------

--

-- Architecture : rtl

-- of Entity : Saturate_top

--

--------------------------------------------------------------------------------

ARCHITECTURE rtl OF Saturate_top IS

CONSTANT Outwidth : natural := 3;

CONSTANT Inwidth : natural := 4;

BEGIN

----------------------------------------------------------------------------

-- Synchronous process

----------------------------------------------------------------------------

clk_reg: PROCESS (clk) IS

BEGIN

------------------------------------------------------------------------

-- Clock section

------------------------------------------------------------------------

clk_if: IF (clk'EVENT AND clk = '1') THEN

IF ( dataIn(Inwidth - 1 downto Outwidth - 1) = "11" ) or (dataIn(Inwidth - 1 downto Outwidth - 1) = "00") THEN

dataOut_f1 <= dataIn(Inwidth-1) & dataIn(Outwidth-2 downto 0);

ELSE

dataOut_f1 <= dataIn(Inwidth-1) & not dataIn(Inwidth-1) & not dataIn(Inwidth-1);

END IF;

------------------------------------------------------------------------

-- Reset section

------------------------------------------------------------------------

i_reset_if: IF (reset = '1') THEN

-- Outputs are reset

dataOut_f1 <= (OTHERS => '0');

dataOut_f2 <= (OTHERS => '0');

END IF i_reset_if;

END IF clk_if;

END PROCESS clk_reg;

END ARCHITECTURE rtl;