《IPcore-SoC设计》

作者:AlphawaveIP:TonyPialis,ClintWalker

本文摘要:

简要介绍高速接口基础知识,以及推动200Gbps连接需求的行业动机。

回顾在将速率提升到200Gbps时所面临的挑战,以及实现这一壮举所需的不同调制方案。

描述用于实现200Gbps接收机的各种方法,以及用于提高相关误码率的纠错和编码方法。

回顾一些实际的200Gbps信道和仿真结果。

给出在200Gbps串行链路上的结论、发现和预测。

高速接口基础介绍

图1展示了任何连接接口的基本组成模块。

图1:通信系统图

在电子系统中,连接功能无处不在,并应用在一个芯片必须与另一个芯片建立连接的任何地方。连接长度可以从跨越数千英里的距离(传统上由高速光网络解决),到用于将芯片直接相互连接的短距chip-to-chip链接。由于每个芯片内部都使用电信号工作,因此电气连接接口是半导体设计的一个重要功能块。

所有计算机芯片都使用数字数据。它们以字节和字的形式出现。一个字节最多包含8位数据,而一个字包含1到16个字节。串行器/解串器(SerDes)在集成电路中被用作与其他芯片的接口,通过将集成电路中使用的并行数据流转换为串行数据流,用于芯片外部和芯片之间的长距离传输,反之亦然。通常,由于时序、同步和占用空间的优势,串行传输在更长的距离上效率更高,复杂性更低,而并行传输对于实现吞吐量和性能的芯片内部至关重要。由于这一关键差异,每个需要快速可靠外部连接的集成电路都需要SerDes。

SerDes由发送器和接收器组成。发送器接收并行数据字,将其串行化并为信道预处理。预处理将数字字转换为真实世界的模拟波形,发送器根据该波形驱动信道上的信号。信道可以是铜缆、光缆、电子板等。

最终,接收器从信道接受真实世界的数据。然后对其进行调节、均衡和重新采样,以补偿信道引入的噪声和干扰。最终,接收器将真实世界的信号转换回数字1和0、数据字节和数据字。

行业需要200G连接!

图2:推动采用224Gbps标准的行业趋势

在过去十年中,新技术、应用、基于云服务和互联网连接设备的激增导致数据流量和拥塞水平的增加,从而推动了对更大带宽的需求。全球数据领域或创建、捕获、复制和消费的数据将从2019年的40兆字节增长到2025年的175兆字节,复合年增长率(CAGR)为28%。这些数据的很大一部分必须使用有线网络基础设施进行传输。以下因素推动了数据的快速创建和使用,包括:

云服务和超大规模数据中心的激增。企业越来越多地采用云服务来降低IT成本并按需扩展计算、网络和存储需求。消费者越来越依赖云服务来满足带宽密集型需求,如高清和4K点播视频观看、音频流和照片共享。全球云服务市场预计将从2020年的5520亿美元增长到2025年的1万亿美元。

先进无线技术的发展,如5G。移动设备上数据和视频密集型内容和应用的消费正在推动移动数据和视频流量的显着增长,并导致了先进的无线通信技术的采用,如5G。到2023年,支持5G设备的平均移动速度预计将达到每秒575兆位,或比今天平均移动连接速度高13倍。为了支持如此巨大的蜂窝速度,有线连接接口必须与此性能相匹配,尤其是在无线信号在路由到核心有线网络之前在接入层聚集。

“物联网”设备的激增。消费者、企业和政府大量采用嵌入电子、软件和传感器的互联网连接设备,预计将进一步增加网络容量并增加对带宽的需求,同时产生大量数据需要处理。到2023年,预计将有大约290亿台设备和物体连接到互联网,而2018年为180亿台。

人工智能的发展。超大规模数据中心的激增、硬件和半导体技术的改进以及软件框架的成熟推动了人工智能应用的显着增长。例如微处理器(“CPU”)、图形处理单元(“GPU”)、现场可编程门阵列(“FPGA”)和专用集成电路(“ASIC”)”)等计算设备现在可以配置为训练和应用复杂的机器学习模型,并做出十年前无法实现的准确预测。随着这些模型变得更加多层和复杂,它们需要在许多相互连接的计算核心上进行处理,这给有线连接和接口技术带来了巨大压力。

因此,为了实现所有这些带宽的增加,以太网速率正在从100Gbps链接快速扩展到800Gbps链接。目前领先的以太网是400Gbps以太网。不过,下一代800Gbps以太网预计2025年将达到2500万台的出货量,远远超过400Gbps以太网的部署量。最初,800Gbps链路将由8条以100Gbps运行的数据通道组成。但绝大多数800Gbps部署将使用以200Gbps运行的四个通道。市场预计,到2024年,将有100多个设计开始集成200Gbps SerDes IPs1.

将符号速率扩展到224Gbps的挑战

图3:将PAM4扩展到224Gbps的权衡

图3中的曲线显示了当前用于光接口的100Gbps IEEE802.3ck“芯片到模块”规范。该标准假设采用30毫米封装,在28GHz下具有大约6.5dB的损耗。因此,在总共16dB的损耗预算中,大约三分之一的损耗分配给发送和接收包,这导致大约12dB的损耗分配给板级损耗。

在28GHz时,12dB的板级损耗导致Meg6材料有大约为5英寸的覆盖范围,而较新的Meg7材料的范围约为10英寸。实际上,这意味着您可以在大型交换SOC和光学模块之间驱动近一英尺的电路板。

通过使用PAM4调制将符号速率扩展到200Gbps,同样的30毫米封装在112GBd符号速率下将消耗大约12dB的损耗。这为电路板留下了大约三分之一的损耗预算。假设将相同的均衡水平应用于224G“芯片到模块”,将导致交换和光模块之间可用的Meg6材料不到1英寸。更新、更昂贵的Meg7材料在两个设备之间实现了整整1.2英寸的距离。显然,从在112Gbps时可以容忍一英尺的间隔,到224Gbps时仅为一英寸。使用光学器件构建系统显然会因这些类型的路由限制而变得笨拙。

这是业界成功将设计扩展到224Gbps必须克服的挑战。

大容量调制方案

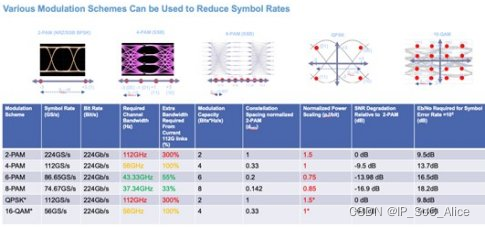

图4:各种调制方案的比较

考虑到预期在封装、电路板基板和高速电缆方面的材料进步,系统设计人员还必须开发提高现有通道数据吞吐量的方案,以实现数据速率的持续扩展。

回顾可用的不同类型的调制方案,例如PAM和NRZ信号,NRZ只是PAM信号的一类(也称为PAM2)。如果您驱动1V峰峰电压,无论调制方案如何,两个星座点之间的间隔都可以(逻辑上)在电气上分类为正三至负三。所以这两个星座点之间的间隔是6。

当您查看PAM4时,假设相同的最大摆幅适用于所有信号方案,那么现在的电气水平为-3-1+1+3。也就是说,任意两个星座点之间的间隔现在只有两个单位,比NRZ减少了三个。

星座点间距的减少是系统设计人员通常表明在实施PAM4与NRZ时信噪比(SNR)降低9dB的原因。这是因为对于相同的最大发射,星座点之间的间隔减少了9dB,这反过来可能会使这两种方案之间的设计对噪声和损耗更敏感9dB。

在考虑更高阶调制(例如PAM8)时,需要增加33%的带宽才能以224Gbps的速率传输,因为现在系统为每个符号传输三个比特。因此,相对于当前PAM4系统的带宽只需要增加33%,而用于224Gbps系统的PAM4需要将其所需的信道带宽增加一倍,这在短期内看来不可能实现。

同样,要使用NRZ,相对于当前可用的112Gbps系统需要增加三倍,这显然是不可行的。

然而,对于PAM8,相对于NRZ,相邻星座点之间的间距从两个单位减少到大约0.86。相对于当前的PAM4系统,这大约是7dBSNR的退化。因此,PAM8使信道容量适度增加了33%,但与当前构建的系统相比,SNR进一步降低了约7dB。

除了PAM之外,还有正交调幅(QAM),其中信号被分成两个正交向量:同相和正交。对于QAM系统,部分信号使用信号的同相部分进行编码,而另一部分使用正交相位进行编码。然后可以用载波调制这些信号各部分,并且两个正交信号可以由载波承载或通过时域复用来避免完全需要载波。QAM调制的好处是,通过将信号传输到正交矢量上,与PAM相比,SNR退化要小得多,因为我们可以将星座点在二个维度上的空间拉得更远,而PAM仅在一个维度上将它们间隔开。然而,QAM的一个缺点是要使用载波或时分复用来实现调制,系统设计人员必须将带宽相对于PAM增加一倍。这种带宽增加是不可行的,并且使得QAM不太受欢迎。因此,没有简单的调制选择。更高阶的PAM需要更少的信道带宽,但SNR继续下降。反过来,由于SNR限制,覆盖范围会缩小,除非系统设计人员可以实施新的均衡方法来恢复损失的性能。

高级DSP检测器

传统的FFE/DFE架构基于单个数据符号做出切片决策。Maximum Likelihood Sequence Detectors(MLSD)使用维特比检测根据数据符号序列做出切片决策。这意味着MLSD:

最小化符号序列中的错误。

使用符号间串扰做出更好的决策。

将SNR提高约1到3dB

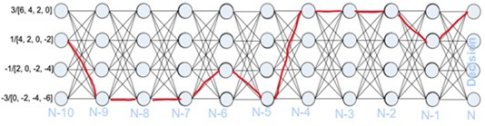

图5:MLSD决策网格示例

使用更高级的DSP方法(例如MLSD)有助于提高SNR。尽管过渡到PAM8会使SNR降低7dB,但系统设计人员可以通过使用更稳健的方法(如MLSD)恢复信号来抵消部分SNR损失。这些检测器类似于DFE,因为您不会放大包含噪声的恢复信号。

MLSD的概念是基于已知的信道响应和重构信号之间的最小均方误差使理想矢量通过FIR滤波器。当信号通过决策网格时,它显示了理想信号在与通道匹配的FIR滤波器的输出端的样子。最后,将来自决策网格输出的预计信号响应与恢复的实际信号进行比较,以确定传输的原始数据。

MLSD的真正威力在于它不基于单个数据位做出决定。决策是在决策网格的输出端做出的,使用匹配的信道滤波器,基于多个数据符号,以帮助实现更可靠的选择。

基于符号序列的切片可以将SNR提高1到3dB。因此,如果转换到PAM8会使SNR降低7dB,则可以使用MLSD检测器来增加高达3dB的SNR增益。现在只剩下4dB的间隙,可以通过一些替代方法恢复。

2m布线硅结果

图6:测得的112Gbps 2m电缆响应

如图6所示,使用MLSD可将BER提高1.5个数量级。

图6中的图是一个例子,说明MLSD检测器在实际系统中使用时可以有多么强大。在该图中,有大量反射落在主脉冲的前80个符号内。这些通常可以使用FFE和DFE进行纠正。然而,在100个符号之外仍然有大量的能量。通常,这些反射无法被均衡,接收器将其视为噪声并最终降低性能。

然而,通过使用MLSD接收器,这种噪声的影响可以被最小化,因为在做出决策之前,噪声会在多个符号上进行平均。在上面的例子中,使用MLSD检测器实现了几乎两个数量级的BER改进。

高性能纠错

级联码只需在延迟和功率上增加一点,就可以扩展性能。因此,前向纠错(FEC)是一种已广泛用于RF读取通道、VDSL和电缆调制解调器的方案,作为使系统在以较低SNR运行时更加稳健的手段。

图7:FEC的SNR优势

图7显示了原始PAM信号的估计BER与SNR(EBNO)的关系图。红色曲线是PAM4的符号错误率与SNR的关系图,蓝色曲线是相同的曲线,但针对NRZ。对于PAM4信号,在1E-15 BER下,需要大约19dB的SNR,而NRZ信号仅需要15dB SNR。这是NRZ提供的明显优势,它允许它在具有同等BER的同时容忍较低的SNR。

参考图7,假设PAM4信号的原始SNR为12dB,相应的BER约为1E-4。如果使用Reed-Solomon KR4 FEC,原始BER会降低到1E-15。因此,对于相同的SNR,FEC产生的错误率几乎提高了12倍。

FEC的一些缺点是它在符号中插入了额外的信息,从而降低了信息吞吐量(这可能会消耗10%到20%的数据吞吐量)。第二代FEC可提供高达10dB的编码增益,而基于“软决策”和迭代解码FEC(例如块Turbo码)仍可实现更高的编码增益。

224Gbps调制仿真结果

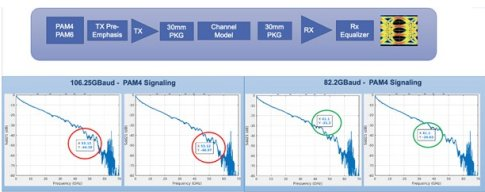

图8分析和比较了PAM4和PAM6信号在两组信道上的性能。两组通道都在链路两侧使用具有代表性的30毫米封装S参数模型,以及通道的内部派生的信道传输线模型。该图比较了PAM4和PAM6信号在Nyquist处的损失:

PAM6具有较低的Nyquist速率,因此与PAM4相比,它在Nyquist(41.1GHz)处仅表现出31至34dB的损耗,后者在53.12GHz处表现出44至47dB的损耗。

与PAM6调制相比,PAM4的这种波特率差异在Nyquist处引入了额外的12dB损耗(即,衰减增加了四倍)。

显然,FEC越复杂,涉及的硬件和延迟就越多。但如果系统可以容忍它,这确实为系统设计人员提供了另一个重要的工具,用于平衡速率、SNR和损耗之间的权衡。

图8:224Gbps示例通道

Matlab仿真结果

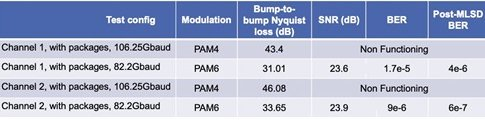

表1显示了在224Gbps的较长通道上较低调制速率的好处。尽管PAM4系统由于插入损耗极大(即CDR无法锁定)而无法正常工作,但PAM6系统能够以可使用标准以太网KP4和KR4 FEC方案恢复的BER运行。

从表1可以看出,对于高损耗信道,PAM6能够恢复具有现有FEC容易纠正的误码率的信号,而PAM4受到过多的符号间干扰,从而无法恢复原始信号。

结论、发现和预测

综上所述:

224Gbps长距离电传输是可以实现的。

PAM4更可取,但不支持更长的通道。

PAM6是物理较长通道的不错选择。

PAM4和PAM6之间的细节仍然需要根据实际信道和应用场景进行审视。

调调制方案可能因形式因素而异。

业界理想的发展道路是继续将PAM4信号用于C2M以及CR和KR应用。然而,虽然这种方法可能适用于C2M信道,但鉴于前面显示的示例,它可能不适用于长距离信道。

作为替代方案,PAM6或PAM8调制可能是一个可行的选择,以减少更高速率/更长距离下的信号损失。使用PAM6,在较低的Nyquist下,更高调制的SNR下降被ISI的改善所抵消。这表明224Gbps可能会导致调制速率分叉,C2M等短距离应用仍使用PAM4,而长距离应用可能转向更高阶调制,如PAM6或PAM8。