导言

之前给大家介绍过alexforencich的开源项目,现在开始陆续出教程,本期主要介绍最常见的AXIS,关于AXI-Stream的概念性教程,请参阅“AXI4/AXI5-Stream协议介绍”一文,开源文章介绍请参阅“FPGA/IC优质开源项目(三)AXI“一文。

AXIS异步FIFO

本期主要介绍AXI-Stream项目中的异步FIFO,其他项目基本大同小异,读者可以直接使用。涉及的文件如下,主要实现了AXIS接口的异步FIFO,可以实现输入输出位宽调整,以及可以实现Frame模式。

axis_adapter.v : Parametrizable bus width adapter

axis_async_fifo.v : Parametrizable asynchronous FIFO

axis_async_fifo_adapter.v : FIFO/width adapter wrapper

testbech代码参数配置如下:

parameter DEPTH = 4096;// FIFO深度

parameter S_DATA_WIDTH = 32;// S接口位宽

parameter S_KEEP_ENABLE = (S_DATA_WIDTH>8);// KEEP信号使能

parameter S_KEEP_WIDTH = (S_DATA_WIDTH/8);

parameter M_DATA_WIDTH = 8;// M接口位宽

parameter M_KEEP_ENABLE = (M_DATA_WIDTH>8);// KEEP接口使能

parameter M_KEEP_WIDTH = (M_DATA_WIDTH/8);

parameter PIPELINE_OUTPUT = 2;// 输出信号寄存器数

parameter FRAME_FIFO = 0;// 是否开启Frame模式

parameter USER_BAD_FRAME_VALUE = 1'b1;

parameter USER_BAD_FRAME_MASK = 1'b1;

parameter DROP_BAD_FRAME = 0;

parameter DROP_WHEN_FULL = 0;

时钟配置:

always #20 s_clk = ~s_clk;// 25M

always #5 m_clk = ~m_clk;// 100M

简单的数据传输:

integer i;

parameter len = 64;// 传输数据长度为64

initial begin

wait (s_rst == 0);

#40;

for (i = 0; i < len; i=i+1 ) begin

wait(s_axis_tready == 1);

s_axis_tvalid <= 1;

s_axis_tdata <= s_axis_tdata +1;

#40;

end

s_axis_tlast <= 1;// 传输结束拉高s_axis_tlast

#40;

s_axis_tlast <= 0;

s_axis_tvalid <= 0;

end

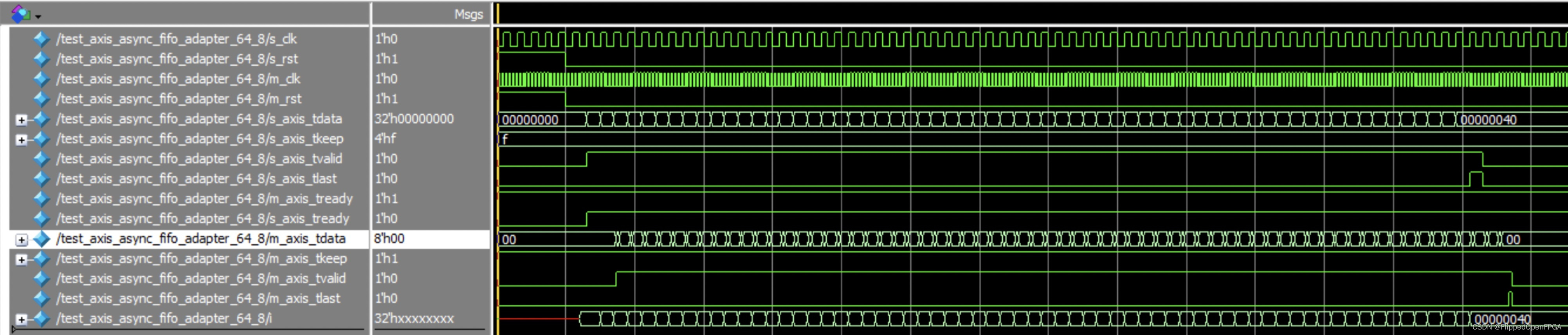

使用modeslsim仿真:

25M时钟域输入,100M时钟域采样,输入32bit位宽,输出8bit位宽,仿真和预期一致。

FIFO的FRAME模式

我们把异步FIFO修改为FRAME模式,即一直到一帧数据传输完成(last拉高),FIFO才继续开始输出数据,配置如下:

parameter FRAME_FIFO = 1;// 是否开启Frame模式

parameter USER_BAD_FRAME_VALUE = 1'b1;

parameter USER_BAD_FRAME_MASK = 1'b1;

parameter DROP_BAD_FRAME = 1;

parameter DROP_WHEN_FULL = 1;

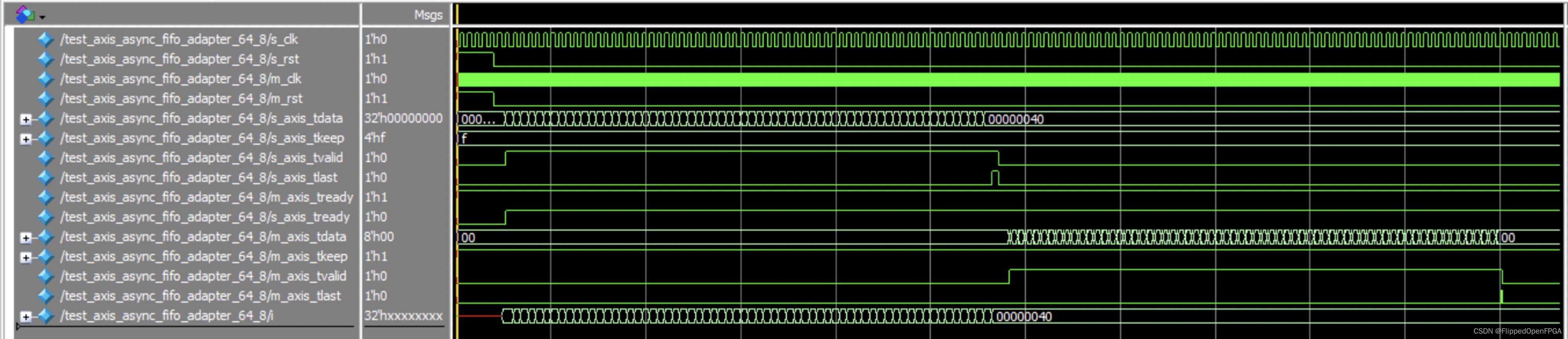

使用modeslsim仿真:

上图可见,直到last拉起前,FIFO才开始传输。

总结

亦安只是简单的测试这个项目,之前对于AXIS概念性的东西都已经讲过了,这里也不多赘述,后续的以太网,AXI等项目也会陆续出,我们下期见。

版权声明:本文为qq_38902665原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。