1)check PG ploc

ERROR(NET-145) NET<xx> in top cell <xx> is not driven b any PAD.

## power source 没有正确标记在对应net 的层次上,找到adsRpt/PG.ploc对照读入的ploc 检查版图。。

ERROR (NET-150) NET <xxx> will not by extracted due to no current sources on this net.

WARNING(CON-196)In following nets xx(xx%) nodes and xx(xx%) resistors are unable to be traversed from their pins/pads they may cause incomplete simulation results for these nets VDD_TOP VDD_1

## VDD_1是VDD_TOP经power switch输出的次一级电源,需要检查前一级power source,如果没有问题,那么就检查switch cell所在的pmk库和switch table有没有加错。

WARNING(PIN-017)Pad pin xx is touched wires of one net xx, but is not connected to the net.

WARNING(PIN-011)Pin xx is not connected to any net and may cause some nets resistor network to be disconnected!

接到net但没有接到cell,可能是cell没接power,也可能接的power wire floating。

WARNING(NET-450)(1) wires in net xx are not connected to power sources or pins.

floating的问题,根据adsRpt/xx.wire.unconnect报告检查版图。

2) missing pg arc

ERROR(ITG-016)Missing PG-arc definitions for cell.

WARNING(SLB-123)For the cell xx,power pin xx is not associated with any PG arc .

ERROR(SLB-091)Pgarc derived from upf lib of cell is not complete.

可能的原因是没有读相应的lib,也有可能是lib没有定义pg arc,前者可以在adsRpt/apache.refCell.noLib和apache.refCell.noPwr中check。后者可以在LIB_FILES {...}先定义一个custom的pgarc.lib

LIB_FILES {

pgarc.lib custom

xxx.lib

}

pgarc.lib需要定义成对的pg关系:

cell xx {

pgarc {

VDD VSS

VBP VBN

}

}

3) PG short

ERROR(CCL-054) ploc:Pad pin <VDD> (type:POWER) at (XX XX)is shorted with (type:GROUND) wire [(XX XX) (XX XX)].

ERROR(PIS-604)PinInst <xx:VDD> (POWER) has inconsistent type with its connect net <VDD> (GROUND).

pg short先检查指定位置的物理连接,然后检查def里关于pg net的POWER/GROUND属性定义。

4) missing Lib

ERROR(ITG-001)xx referenced cells are not defined in Lib.

WARNNING(ITG-4)xx referenced cells dont have internal power defined in lib.

lib 缺失可以查看adsRpt/apache.refCell.noLib和apache.refCell.noPwr中check。

5)VCD

ERROR(VCD-321)For block xx ,net coverage (xx%) is lesser than coverage threshold 5%.

这个问题大概率是VCD的FRONT PATH给错了。仿真的同事没有给front path的时候,如果用VCD文件,可以打开VCD找到如下定义:

$scope module xx $end

$scope module yy $end

$scope module u_block_name $end

如果redhawk分析u_block_name这一层那front path就是/xx/yy/u_block_name

如果用的fsdb文件,那就用verdi打开fsdb文件具体操作就是:

菜单栏选择FILE-Open Waveform Files

然后波形上面的菜单栏选择Signal-Get Signals

在Scope里输入关键字看数字设计里port所在层次来确定,front path,比如搜索*block_name*结果中有/xx/yy/u_block_name/Port_name,Port_name就是数字的一个port那front path就是/xx/yy/u_block_name

6)switch table

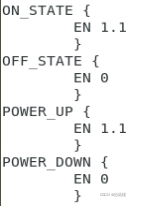

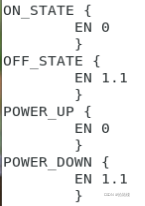

产生switch table的config文件对state和power up的定义错误会导致switch cell变成一块大电阻。错误使用如图1所示。

图1.swich table config 文件state部分截图

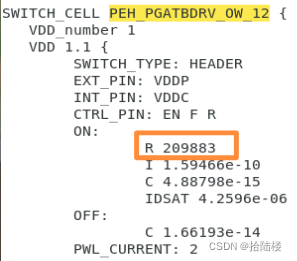

switch table里电阻会很大,如图2。

图2 switch table 电阻部分截图

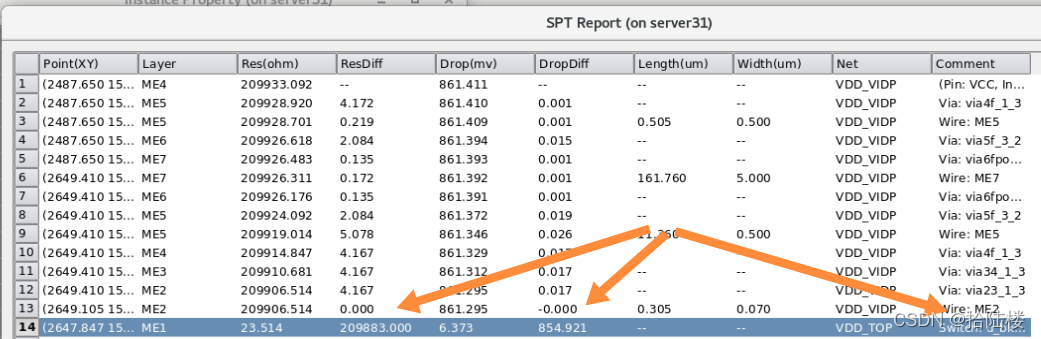

做ir drop分析的时候,switch cell的会分产生很大的压降。如图3:

图3.min res path switch cell的压降示例

正确的config定义应该是: