1.analysis

仿真的第一步是analysis.在这步当中,用vhdlan/vlogan分析VHDL、verilog、system verilog等文件,检查设计的语法错误.

a.分析vhdl

vhdlan [vhdlan_options] file1.vhd file2.vhd

b.分析verilog

vlogan [vlogan_options] file1.vhd file2.vhd

c.分析system verilog

vlogan -sverilog [vlogan_options] file1.sv file2.sv file3.v

c.分析OpenVera

vlogan -ntb [vlogan_options] file1.vr file2.vr file3.v

d.分析SystemVerilog and OpenVera files

vlogan -sverilog -ntb [vlogan_options] file1.sv file2.vr file3.v

e.work

通过-work告诉vcs mx保存中间文件.在分析设计之前,确保在synopsys_sim.setup中定义了需要生成的中间文件的名字.-work创建的是逻辑库的名字,逻辑库存放的位置即物理库的位置由synopsys_sim.setup所确定.在makefile中使用的时候,用的是其逻辑库的名字.

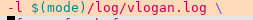

e.-l output_file

用来设置存储analysis message文件,可以设置文件相对应的路径.

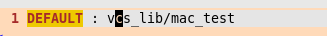

f.default

synopsys_sim.setup如果用default的话,那么在vlogan中也需要将work后面的参数改为DEFAULT.

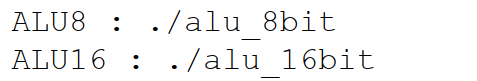

h.multi work

出现多个中间文件时,个人理解是调用多次vlogan/vhdlan,每次调用对应一个中间文件.

i.other setup files

OTHERS=[filename]

在添加时找到对应文件所在的路径,以便能够正常的读取文件.

j.synopsys_sim.setup

可以通过setenv SYNOPSYS_SIM_SETUP my_setup对SYNOPSYS_SIM_SETUP做override.这样做之后setup文件便可以用自定义的.

k.analysis生成log

2>&1 | tee -a vlogan.log

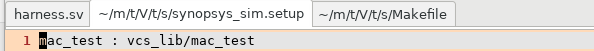

l.编译

通过work生成逻辑库文件之后,在编译时需要将需要使用的module显式调用出来.

例如:DEFAULT.mac_test

2.UVM相关的参数

a.+incdir+${UVM_HOME}/src —添加UVM相关的源文件

b.${UVM_HOME}/src/dpi/uvm_dpi.cc --添加dpi相关的文件

c.${UVM_HOME}/src/uvm_pkg.sv–添加package文件

d.-P ${VERDI_HOME}/novas.tab

e.${VERDI_HOME}/pli.a

f.-ntb_opts uvm–设置使用的UVM版本

g.${VCS_HOME}/bin/vlogan–调用vlogan命令

3.常见错误

a.Cannot find VCS compiler VCS compiler ‘VCS_HOME’ not found

出现这样的问题是因为装的VCS版本是64,在使用的时候要添加-full64

b.No TopModule/Entity supplied

出现这个问题是在elaborate时,需要将使用vlogan生成的中间文件关联过来.而且需要将设计代码中verilog/vhdl的顶层moudle名字添加进来,不是例化的名字.

如果在环境中有多个module,需要将所有的module都添加进来.

通过-work指定中间层的名字,在elaborate时,通过中间层的名字和设计的module名字将二者关联起来,从而方便后续使用.

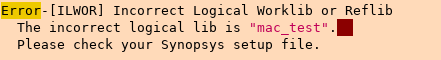

c.Incorrect Logical Worklib or Reflib

在仿真目录下需要创建synopsys_sim.setup文件.

d.harness cross-module reference error

验证环境中一般会通过module将设计的代码包含进来,module内部会生成对应的时钟和复位信号.添加用例时有时候需要对设计内部的信号进行force,在force的时候只有在elaborate中定义的设计顶层才可以看到.

vcs three-step flow学习记录

版权声明:本文为weixin_39662684原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。