FPGA Verilog 相当于“Hello world"的一段入门代码:

module test(clk,a);

input clk;

output a;

reg [8:0]a;

always@(posedge clk)

begin

a <= a +1'b1;

end

endmodule

仿真TestBench 代码:

`timescale 1 ns/ 1 ps

module test_vlg_vec_tst();

reg clk;

wire [8:0] a;

always #10 clk=~clk;

initial

begin

clk = 0;

#120 $stop;

end

test i1 (

.clk(clk),

.a(a)

);

endmodule

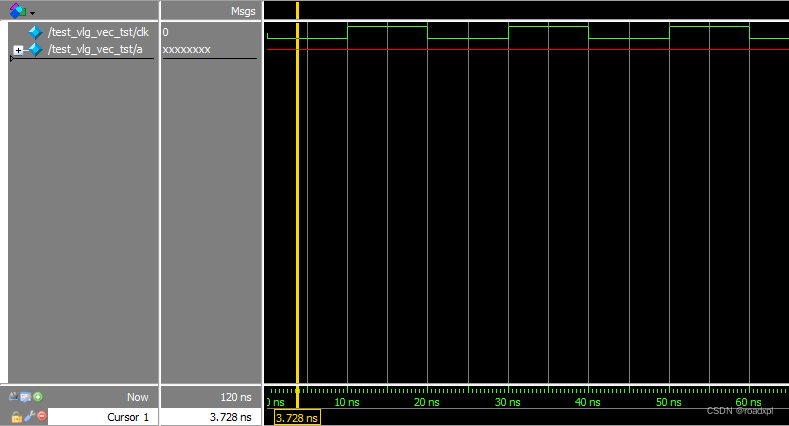

仿真界面, output a 是没有数据的,显示一串xxxxx.

原因是变量a在初始化时没有被赋值,代码修改为:

module test(clk,rst,a);

input clk;

input rst;

output a;

reg [8:0]a;

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

a <= 9'b0;

end

else

begin

a <= a +1'b1;

end

end

endmodule

testbench 修改为:

`timescale 1 ns/ 1 ps

module test_vlg_vec_tst();

reg clk;

reg rst;

wire [8:0] a;

always #10 clk=~clk;

initial

begin

clk = 0;

rst = 0;

#10 rst = 1;

#120 $stop;

end

test i1 (

.clk(clk),

.a(a)

.rst(rst)

);

endmodule

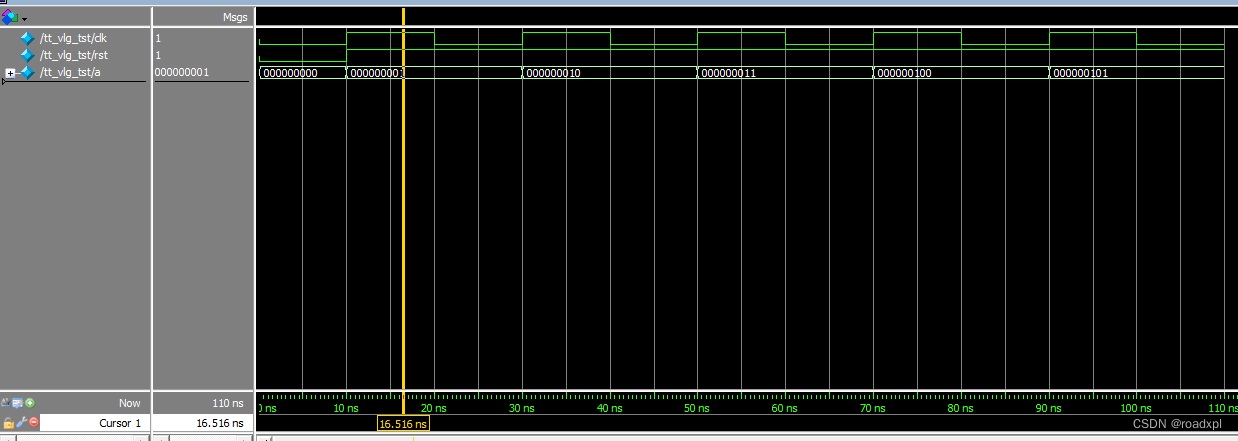

仿真时,正确出现output a 变量的数值。

分析:

1. 其它编程语言如C++,在头文件声明了变量,有时不用初始化赋值,在后面做运算时,如a =a+1不会出错,计算过程和结果为1=0+1, 可见程序会自动将该变量初始化赋值为0. 但FPGA是面向硬件的编程,要求严谨,否则就会出现如上的问题。

其它注意点:

1.testbench 文件里面的端口连接部分,如缺少.rst(rst),变量 output a 也无数据,因为相当于rst端口在仿真时没有被使能,.v文件内的语句negedge rst、if(!rst) 将无作用,于是也不能对变量 output a 进行初始化赋值。

2. 对于always@(posedge clk or negedge rst)、if(!rst) 的理解: 仿真过程,观察发现0时刻,rst是高电平状态,即为1,(0时刻的线是一条从1到0的垂直线)于是可以实现0时刻,在rst的下降沿,如rst是0,则后面的对变量 output a 的赋值过程可以实施。

3.可否在testbench里面对Output a 进行初始化赋值?modelsim 直接报错,个人理解,FPGA 里的output a 不同于其它编程语言里面数值类型,其是真实对应于内部门电路的物理级输出。形象的理解,就如同一个三级管,输出端(集电极)的电流变化是基于输入(基级)电流的变化的。于是可以理解为必须要通过门电路的输入来控制输出,而不是直接给输出端直接赋值我们想要的结果

由于习惯于C,python等编程,以上分析可能有纰漏、错误之处,敬请指正。