- 说在前面

开发环境:Vivado

语言:Verilog

cpu框架:Mips

计算机组成原理课程终于结束了,由于以下均为课程学习过程中的内容,所以难免存在各种错误,各位大佬轻喷

- 相关软件

- vivado

Xilinx公司的集成环境,笔者用的是下面这个:

http://china.xilinx.com/support/download.html

版本的话应该都可以吧,安装教程可以看下面这个:

license相关可以看下面这个

其他支持Verilog开发的开发环境应该也可以使用,比如Quartus(没用过)

其他:

- modelsim

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

话是这么说,但是在cpu仿真的时候还不如用vivado自带的仿真工具,方便很多,而且节省时间(虽然说modelsim可以找到一些深层次的错误)

modelsim获取安装可以看下面这个(付费软件真烦啊):

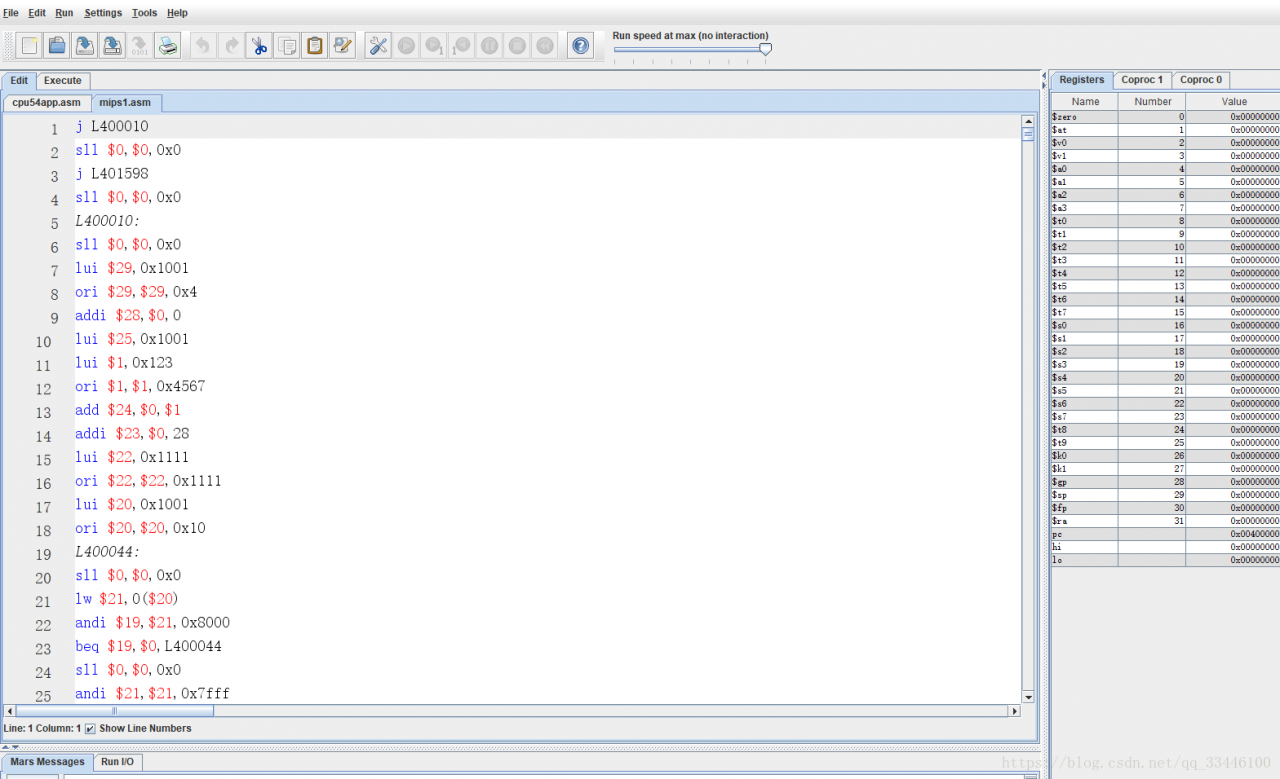

- mars

Mips框架下的轻量级IDE

这个相当于是给我们验证cpu相关指令结果是否正确的,我们设计的cpu是以这个里面的结构为基础的,各种指令的结果也是以它为准进行验证(课程要求,无奈)

界面如下,功能还是挺全的

下载

- 画图

processon:https://www.processon.com/

免费,但是有数量限制

diagrams:https://app.diagrams.net/

免费,并且有离线版本

版权声明:本文为qq_33446100原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。