scan chain compress/decompress

一.Why scan chain compress ?

- 芯片设计规模愈来愈大,受到管脚数目的限制,scan chain变得越来越长

- 在DFT上的tese time就长,而test time是影响整个芯片成本的一个关键因素

二.How to do scan chain compress ?

- 外部测试pin并不增加,里面会分成并行的多条链

- 每条链的长度得以减小,测试时间取决于最长的那条链,测试向量也是经算法压缩的

三.DFT中内部扫描

- 一般使用DFT Complier+ TetraMAX工具组合

- DFT Complier负责对综合之后或者综合过程中的门级网表插入扫描链寄存器

- TetraMAX根据DFT Complier产生的测试文件进行测试

工具:

DFT MAX :synopsys的DFT Complier

ATPG:synopsys的TetraMAX

四.DFT MAX

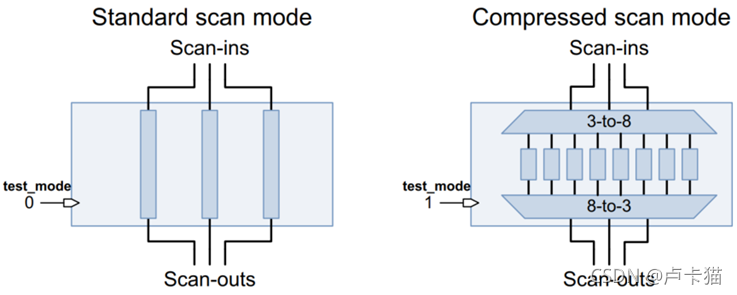

DFT MAX运行中,当启用扫描压缩时,insert_dft命令将压缩扫描逻辑插入到设计中,并定义以下两种测试模式:

compressed scan mode

这种模式将扫描元素配置为由decompressors驱动的短链standard scan mode

这种模式将压缩后的短扫描链重新配置为较长的标准扫描链

五.DFTMAX

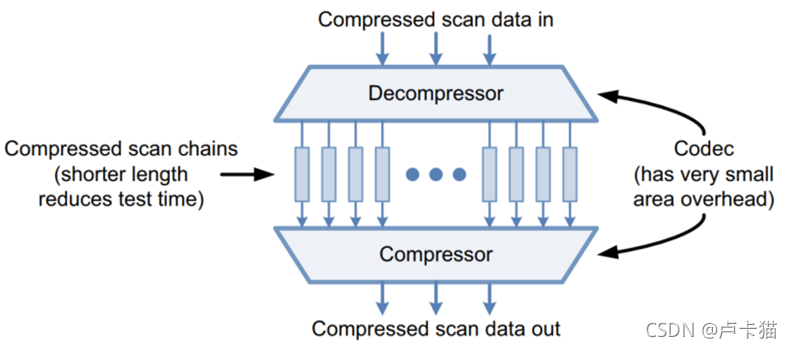

DFTMAX压缩扫描与标准扫描类似,但它包含组合压缩逻辑,并在芯片核心内使用更多更短长度的扫描链。

DFTMAX压缩将标准扫描链划分为更多更短的链,称为compressed scan chains ,这减少了测试时间。

Decompressor operation

当扫描输入值移位时,decompressor 将它们分布到多个扫描链中。decompressor 输出宽度等于compressed scan chains的数量。

Compressor operation

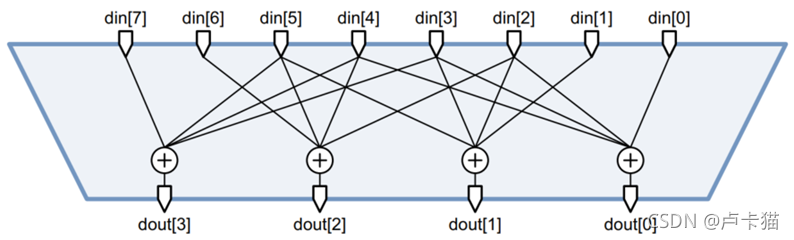

compressor输入宽度等于compressed scan chains 的个数。compressor 的输出输出由不同的compressed scan chains组合驱动,组合使用异或逻辑。compressor减少从大量compressed scan chains捕获的数据,使其可以通过scan-out ports 观察。

六.DFT MAX Ultra

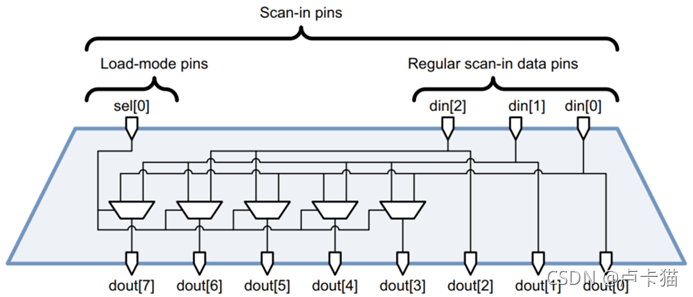

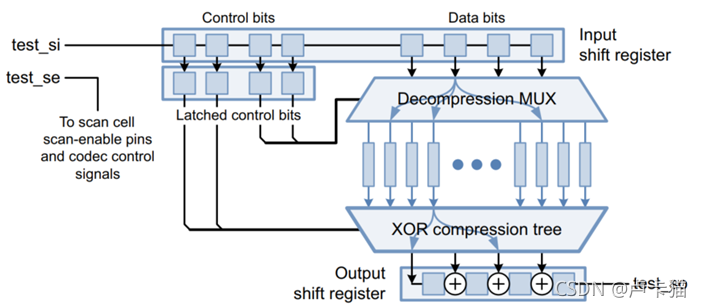

DFT MAX Ultra 该技术提供非常高的压缩,即使很少扫描I/O引脚。DFTMAX超压缩架构允许测试数据通过单个输入端口流入,并使用正常的移位时钟通过单个输出端口读出。同时,输入和输出移位寄存器允许高水平的压缩,以实现非常好的故障覆盖。

- 扫描数据端口提供一个输入移位寄存器。移位寄存器中的一些位用作控制位,而另一些位用作数据位

- 数据位向解压缩多路复用器(MUX)提供流数据,MUX是一个组合逻辑块,将数据分发到压缩扫描链

- 在扫描链输出时,一个组合异或压缩树和一个顺序异或输出移位寄存器将数据压缩到单个流中