一、概述

在前端设计完成逻辑综合得到门级网表,并在后端完成 数据设置后,需要进行布图规划(floorplanning)。后续的布局、时钟树综合CTS、布线等步骤都是在设计布图的基础上进行。

芯片级布图定义的芯片信息包括:芯片核心(core,即芯片内部逻辑功能区)设置,包括 核心的尺寸、形状、布局的行(标准单元布局按横条排列);外设,包括IO、电源、拐角管脚(corner pad)以及填充单元的位置;宏块的布局;标准单元的布局约束,用于定义禁止布局的区域; 电源的网格,包括电源环、条带和电源轨道。

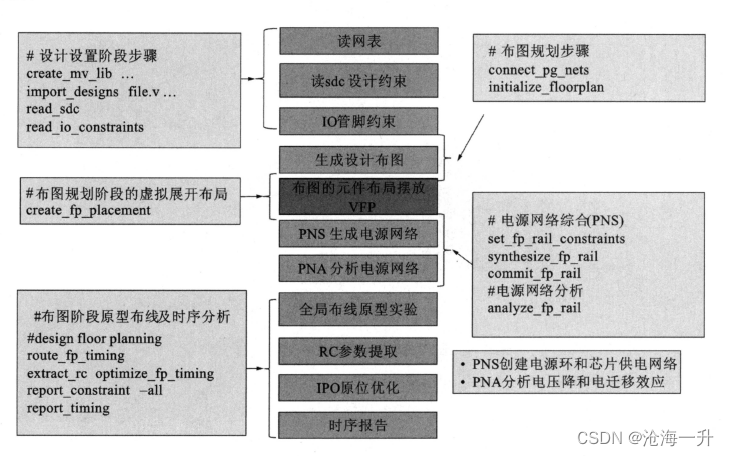

布图规划流程及主要命令示意图,主要包括设计的设置阶段、布图规划阶段、虚拟展开布局VFP、电源网络综合与分析、布图阶段原型布线(全局布线)及时序分析5个阶段。

在完成虚拟展开布局VFP后,需要根据拥塞情况进行宏块位置的优化调整,以尽可能改善布线阶段的拥塞状态。原型布线和原位优化IPO主要用于对布图规划的设计时序结果进行较准确的评估和优化。

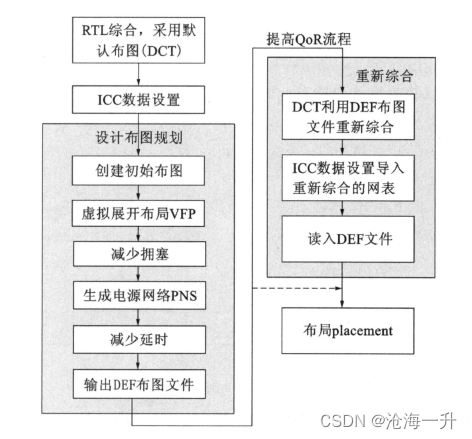

布图规划输出的DEF布图文件可供综合工具DCT参考,流程分为设计布图和重新综合两步。设计布图规划结合重新综合流程的分步流程图如图所示。

ICC布图与综合DCT的联合优化利用了布图的拓扑(topology)信息,二次综合结 果与后端设计电路结构的拟合度更好。二次综合流程中DCT利用布图规划导出的DEF布图文件重新综合完成后,综合网表再次导入ICC完成数据设置步骤,读入DEF文件,完成了设计规划工作。下一步标准单元布局将基于性能改进的门级网表进行。

模块级布图规划的初始化步骤如下:

对于直角多边形的布图区域设置可以调用预定义的模板,实现较典型的复杂形状。

芯片级的初始布图规划步骤如下:

- 创建仅在物理设计使用的管脚(pad cells);

- 指定管脚单元的位置;

- 初始化设计布图;

- 在管脚之间添加管脚填充单元(pad filler cells);

- 创建管脚的电源/地环(P/G pad rings);

- 指定忽略的走线层;

- 定义已知(确定)的宏块和标准单元布局(placement);

- 指定已知的电源网络结构;

- 定义已知的布局禁止区域(placement blockage)。

二、初始化布图规划

初始化布图规划这一步的工作完成了后端设计芯片基本形态定义,主要完成以下设置:

- 创建芯片核心区域和外设(外围)区域,核心区用于放置宏块、标准单元等,而外设区域主要摆放芯片的管脚;

- 定义核心区域的标准单元布局行属性、芯片的边界或外围区域设置,如核心利用率、长宽比、核心到管脚的距离等;

- 按照物理约束,例如设置的tdf文件或者管脚约束tcl文件放置io管脚,包括网表定义的管脚和物理设计创建的管脚。

1、设置管脚约束

1)创建芯片管脚单元(pad cell)

在DC综合得到的门级网表没有定义的电源、地管脚以及芯片外围边沿4个拐角的管脚 单元。这些仅用于物理设计的管脚需要在指定信号管脚单元的位置前定义。仅用于物理设计的管脚的定义采用命令create_cell,举例如下:

create_cell {vss_l vss_r vss_t vss_b} pvOi

create_cell (vdd_l vdd_r vdd_t vdd_b} pvdi

create_cell (CornerLL CornerLR CornerTR CornerTL} pfrelr

上述示例脚本创建了上下左右4边各一个电源管脚和一个地管脚,并且创建了芯片4个拐角单元。管脚的添加一般按照电源、拐角、信号脚的顺序。

2)基于tdf文件设置芯片管脚顺序

设计中添加完仅用于物理设计的管脚后,下一步需要导入tdf文件,即Top Design File顶层设计文件。tdf主要的作用是定义管脚位置,可以用来配置芯片管脚的名称、位置对应关系。

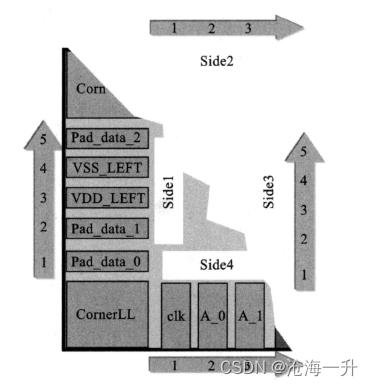

拐角管脚 的定义格式如下:

pad padName padSide [padOrder] [padOffset] ["reflect"]管脚定义中,padName指定管脚的名称,padSide指定管脚所在边,数值padOrder指定管脚在所在边的序号。拐角管脚在所在边的顶角,因此不标序号。非拐角管脚的tdf定义格式为与拐角管脚格式相同,但管脚所在边序号padOrder需要标出。padOffset指的是管脚相对于参考边的绝对偏移量,单位是微米,该偏移量设置是可选的。如果没有加padOffset偏移距离控制,管脚默认在每一边是均匀排列。

;tdf文件

;放置管脚单元

pad "cornerLL" "bottom"

pad "cornerLR" "right"

pad "cornerTR" "top"

pad "cornerTL" "left"

;放置io和电源管脚

;左右边的管脚编号从下往上顺序编号(除了拐角的管脚)

pad "pad_data_0" "left" 1

pad "pad_data_1" "left" 2

pad "VDD_LEFT" "left" 3

pad "VSS_LEFT" "left" 4

pad "pad_data_2" "left" 5

;下边和上边的管脚编号从左往右顺序编号(除了拐角的管脚)

pad "Clk" "bottom" 1

pad "A_0" "bottom" 2

pad "A_1" "bottom" 3

上面脚本定义的芯片管脚如下:

完成芯片级布图规划的管脚顺序定义文件tdf后,可采用如下tcl命令将管脚顺序读 入ICC:

read_io_constraints [-append] [-cel_namel [-child_cell] < TDF_file>3)基于tcl命令设置芯片管脚顺序

在新版本ICC中,pad管脚位置设置可采用tcl命令实现,代替单独的tdf文件设置。采用的命令是set_pad_physical_constraints,命令格式如下:

set_pad_physical constraints [-pad_name][-side][-order]芯片的四边side l.side 2.side 3.side 4分别对应的是左、上、右、下四边;左上、右上、右下、左下四个拐角管脚分别属于side1.side 2.side 3.side 4。

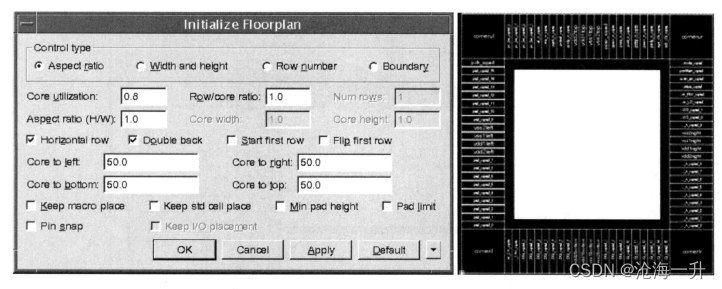

2、布图创建

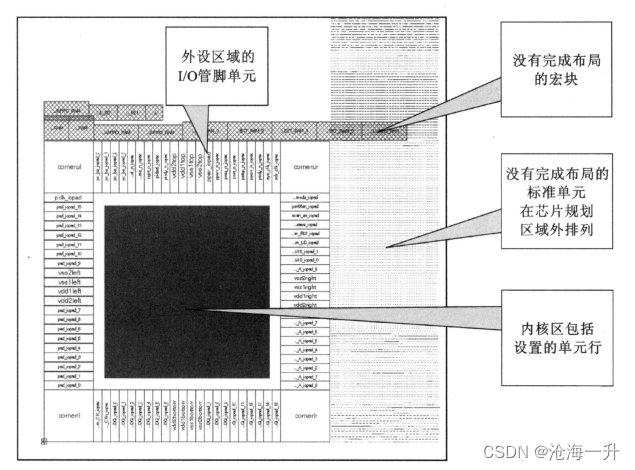

布图创建的命令是initialize_floorplan或采用命令initialize_rectilinear_block创建直角多 边形的规划区域。initialize_floorplan的图形化界面设置以及创建后的版图示例如所示。

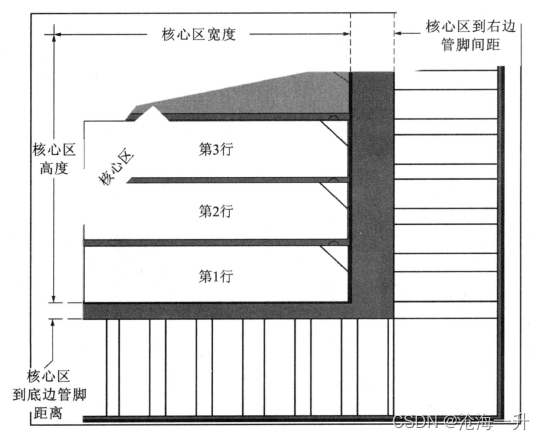

初始化布图完成后,芯片的管脚按照指定顺序排列在芯片的4边,而内部核心区域与管脚之间留有间距,如这里设置的50。在设置选项中的Horizontal rows指的是标准单元行的方向是否是水平方向;Double back指的是相邻两行标准单选的方向是否是翻转一行,背靠背放置。

1)芯片核心(core)区域参数设置

控制的参数包括两种可选的配置。

(1)通过比例控制

- 设置核心区的利用率(根据网表的宏块和单元总面积及利用率可估算核心区面积);

- 设置高/宽比(控制芯片外形);

- 设置标准单元行(row)/核心区面积比(体现标准单元的芯片利用率);

(2)通过指定高度和宽度控制

- 包括芯片核心的宽度和高度具体尺寸;

- 核心到各边管脚的距离。

布图在初始化完成后,可以看到外围的IO管脚已经按约束排列,还没有摆放的宏块排列在芯片上方,还未布局的标准单元排列在芯片区域外右侧,核心区域内可以看到标准单元行的site rows的位置定义。

2)插入管脚填充单元(filler cell)

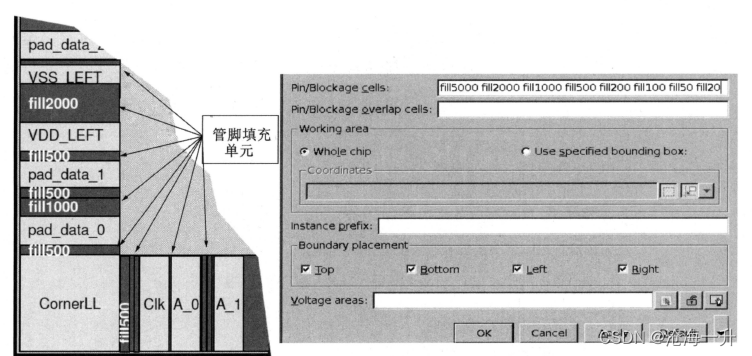

管脚填充单元的作用为:由于管脚之间可能存在间隙,管脚填充单元使管脚之间的N阱、P阱和P/G电源环保持连接的连续性,使得信号管脚功能正常,并获得供电。

插入管脚填充单元采用的insert_pad_filler命令应用如下,其中-cell选项指定填充单元 的可选单元名称列表,例如fill5000、fill2000等。管脚填充单元的名称中数字指明了单元宽度,命令在指定填充单元时按照宽度从大到小排列,插入单元时先尽可能选择宽度大的单元, 这样可以使填充单元数量最少。

insert_pad_filler -cell "fill5000 fill2000 fill1000 ..."插入管脚填充单元的示意效果图如下图所示,管脚之间插入的填充单元数量和类型不尽相同。右图显示插入管脚填充单元的用户设置界面。用户可填入插入单元名称、插入的区域以及选择在哪一边插入填充单元。

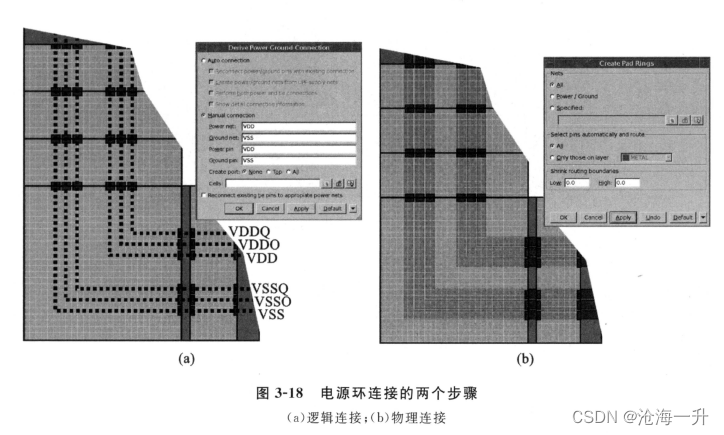

3)创建管脚的电源与地(P/G)电源环

创建分两步:先创建pad的电源脚(电源和地脚各3个)到电源网络(net)的逻辑连接(虚 线);再采用create_pad_rings命令物理连接电源环,即完成电源环布线。

derive_pg_connection -power_net VDD -power_pin VDD -ground_net VSS\

-ground_pin VSS

derive_pg_connection -power_net VDDO -power_pin VDDO -ground_net VSSO\

-ground_pin VSSO

derive_pg_connection -power_net VDDQ -power_pin VDDQ -ground_net VSSQ\

-ground_pin VSSQ

derive pg connection -power_net PWR -ground_net GND -tie

create_pad_rings

4)VFP(Virtual flat placement)前的准备

虚拟展开布局是在布图规划阶段通过create_fp_placement命令实现对设计的所有单元 的尝试性布局,主要用于判断布图规划是否存在潜在布线拥塞(congestion)风险。

在虚拟展开布局前可以先明确非默认的约束设置,包括:

- 可以先指定不用的布线层;

- 提前定义宏块与标准单元的位置;

- 设置已知的禁止布局区域。

(1)忽略不用的走线层

ICC默认使用所用金属走线层。但如果计划使用更少的层走线(减少使用高层金属层,降低制造成本),但没有指明,结果会造成走线前阶段的估算利用了更多金属层,对于拥塞的分析 过于乐观;RC寄生参数不准,造成走线时延的计算偏差较大。因此需要使用set_ignored_layers命令向ICC指定哪些层不能走线,提高走线之前对拥塞和时序分析的精度。如下设置命令,只允许使用最高到M7层的金属层用于布线:

set_ignored_layers -max_routing_layer M7此外,可以通过以下命令查看和去除忽略的布线层。

report_ignored_layers

remove_ignored_layers

(2)限制宏块(macro)

虚拟展开布局create_fp_placement执行后,宏块放置的位置可能不合理,造成电源网络 结构复杂,或者需要更多的总线布线资源。因此在虚拟展开布局前,可以手动在GUI界面对宏块布局,并且可以设置约束指导布局。命令如下:

set_fp_macro_options ... #设置宏块布局选项

set_fp_macro_array ... #设置宏块阵列,集中排列关联密切的宏块

#设置关联布局,指定一个单元相对于锚点anchor的相对位置

set_fp_relative_location ...

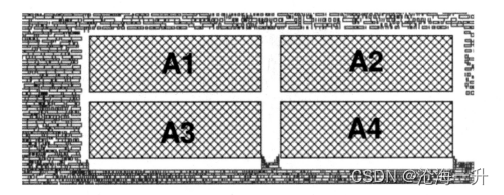

这个阶段宏块的布局约束是软性(soft)约束,后续设计中尽可能遵守约束,但并不是必须遵守。set_fp_macro_array设置多个宏块按阵列形式排列的脚本如下:

set_fp_macro_array -name A_array -elements \

[list [get_cells Al A2] [get_cells A3 A4]] \

-x_offset 15 -y_offset 110

如图所示为布图阶段设置宏块阵列Ao以上命令指定了有A1、A2、A3、A4组成的二维阵列A_array,并设置宏块的水平和垂直方向的偏移量。在布图阶段的VFP虚拟展开布局操作中,宏块阵列被认为是单元对象,因此VFP不会在宏块之间插入标准单元。

另一个宏块控制命令set_fp_macro_options对宏块布局的控制包括:

- 通过legal_orientations选项控制宏块的布局方向;

- 通过anchor_bound选项控制宏块限定在核心区指定的1/2或者1/4区域布局;

- 通过side channel选项指定宏块或宏块组到核心区四边的距离。

(3)禁止布局区域(placement blockage)设置

1、全局(global)的禁止布局设置

通过set_app_ var变量设置实现,硬性禁止布局设置变量physopt_hard_keepout_distance,变量名中physopt可以理解为物理综合优化,即布局。

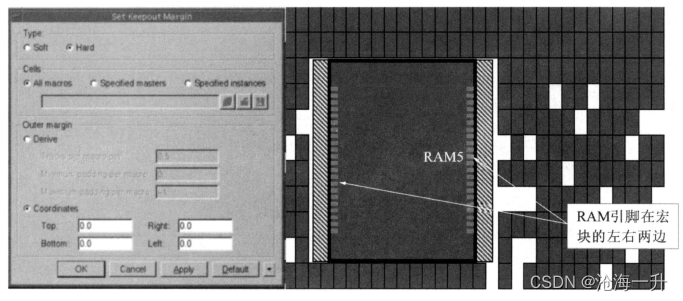

图中RAM宏块周边的条纹框区域是硬性禁止区,在宏块的四边创建。作为全局 设置,所有固定宏块的四周会设置硬性禁止区,设置命令如下,在距离宏块四边10的距离 内禁止布局摆放其他单元。命令设置如下:

set_app_var physopt_hard_keepout_distance 10图中浅白色条带是软性禁止布局区,用于设置宏块之间或者宏块到芯片核心区边缘 的狭窄通道内禁止布线,通过placer_soft_keepout_channel_width变量设置。

set_app_var placer_soft_keepout_channel_width 25这两条全局设置可添加到.synopsys_dc. setup文件,便于ICC软件开启自动加载。

2、宏块具体(specific)的禁止布局设置

可以采用set_keepout_margin命令指定特定的禁止布局区。例如软性或者硬性,以及到宏块的各边距离。

上中RAM的管脚引出的左右两边进行限制禁止区宽度10。对应的命令如下:

set_keepout_margin -type hard -outer {10 0 10 0} RAM5其中type选项可选soft或者hard,决定是软性还是硬性规定,-outer选项的{}内数值对应了左下右上四边的区域空白宽度。要查看或者去除设置的禁止布局空白区,可以使用如下命令:

report_keepout_margin # 报告

remove_keepout_margin # 去除

3、小结

创建初始布图规划的流程图和对应命令设置:

布图规划初始化阶段的tcl脚本流程如下:

open_mw_cel DESIGN_data_setup # 打开前一阶段设计

create_cell . . . #创建仅用于物理设计的管脚单元

read_io_constraints < TDF_file> # 或 set_pad_physical_constraints … initialize_floorplan ... # 初始化设计布图

insert_pad_filler ... #在管脚之间添加管脚填充单元

derive_pg_connection ... #

create_pad_rings ... #创建管脚的电源/地环

set_ignored_layers - max M7 # 指定忽略的走线层

#手动放置需要设定手动定位的宏块

set_dont_touch_placement [all_macro_cells] # 固定宏块的位置

set_fp_macro_options ... #设定宏块摆放的3个命令:选项、阵列、相对位置

set_fp_macro_array . . .

set_fp_relative_location …

set app var physopt_hard_keepout_distance < # > # 宏块全局硬性禁止布局区设置

set app var placer_soft_keepout_channel_width < # > # 宏块全局软性禁止布局区设置

set keepout margin… #宏块具体的禁止布局区设置