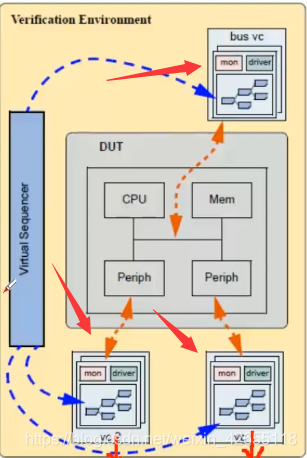

virtual sequence 即虚seq,用于管理多个实sequence的执行顺序。

下面有三个sequence,此时需要virtual sequence去管理这三个的顺序。

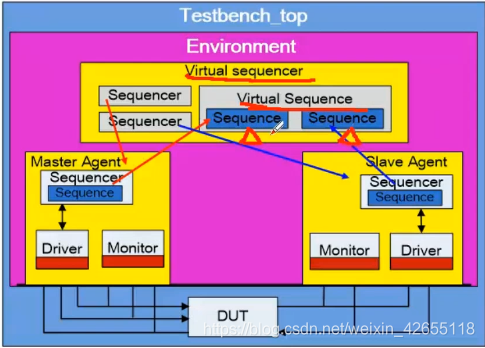

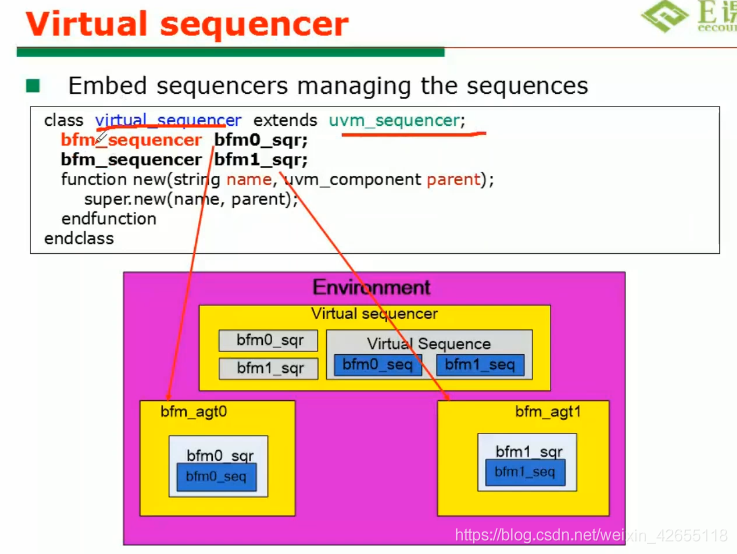

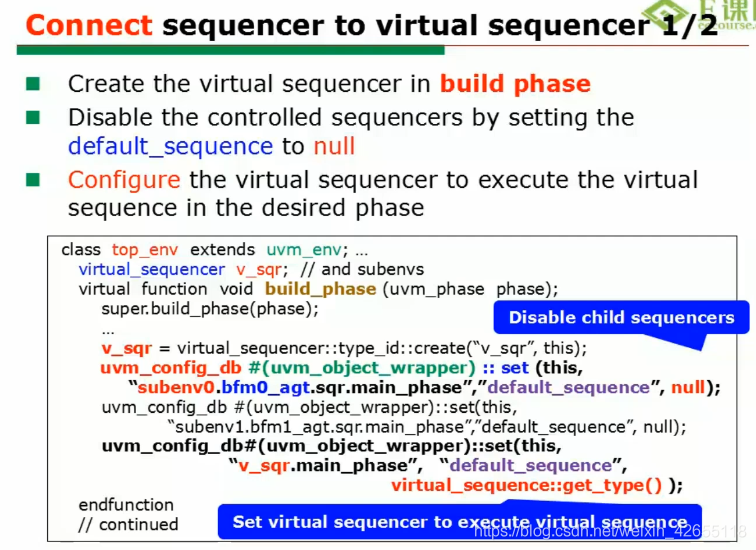

先写两个文件,virtual sequence和virtual sequencer,例化实sequence和实sequencer:

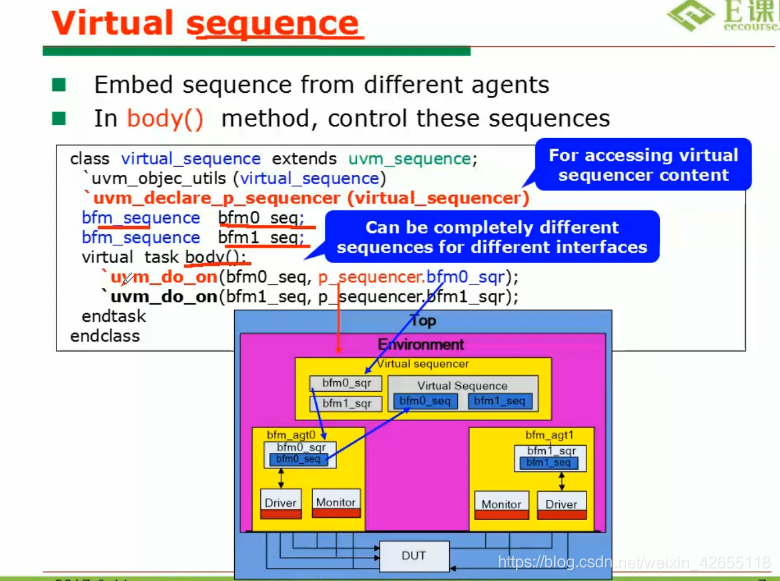

此时在virtual sequence里面启动程序,而不是之前在test.sv(用default或start函数)启动。

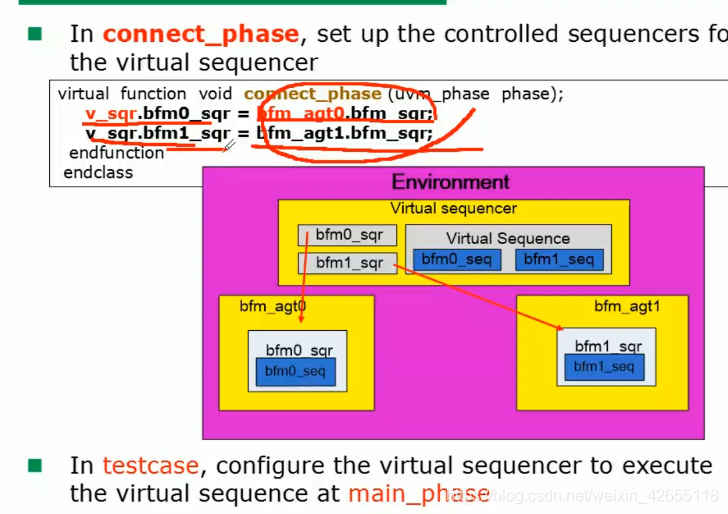

virtual sequence的使用如下:

1、例化sequencer,

2、例化sequence,

用 `uvm_do_on启动

实sequence用的是 `uvm_do

bfm0_seq这个sequence用uvm_do_on

p_sequence.bfm0_sqr这sequencer来启动。

这俩是串行的。

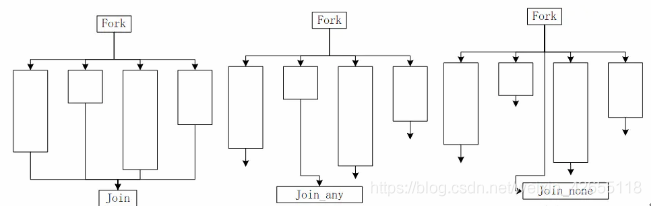

插播一组fork join:

3、将原来的sequence设置为null,再default virtual_sequence。

4、接下来写connect文件,连接virtual sequencer和实sequencer。

virtual function void connect_phase,写在env里或testcase里。

5、在build_phase里注销掉原来的default_sequence并启动virtual_sequence。

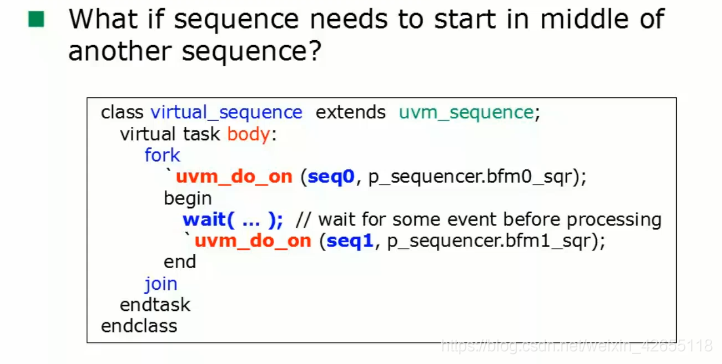

补充:在已启动的sequence里面插入sequence

总结:使用virtual_sequence用来排序sequence的运行顺序,需要写virtual_sequence.sv和virtual_sequencer.sv两个文件,并在env.sv或testcase.sv里面进行connect,最后再env.sv里面注销掉原来的default_sequence,启动virtual_sequence。

版权声明:本文为weixin_42655118原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。