从零开始 verilog 以太网交换机(一)架构分析

前言

马上要去新公司入职,也将步入我再三思考的网络IC行业

在入职前,准备完成一个简单的以太网交换机的项目

以下所有内容均参考于乔庐峰教授的《Verilog HDL数字系统设计与验证——以太网交换机案例分析》

一、ethernet switch作用

在开始工程前,先讨论以下为什么要有以太网交换机。

简单来说,当越来越多的设备接入网络后,点对点的通信需要某一设备来集中处理数据的转发

以太网交换机就是为了完成这一任务,当然随着时代发展,其内部对网络包的处理变得更为多样,但本工程仅仅完成最基本的交换机功能

二、ethernet switch架构

首先我们明确一下,ethernet switch作用在ISO模型的传输层,物理层将由外置的PHY完成,更上层的网络层、链路层也可以进一步融入设计中。

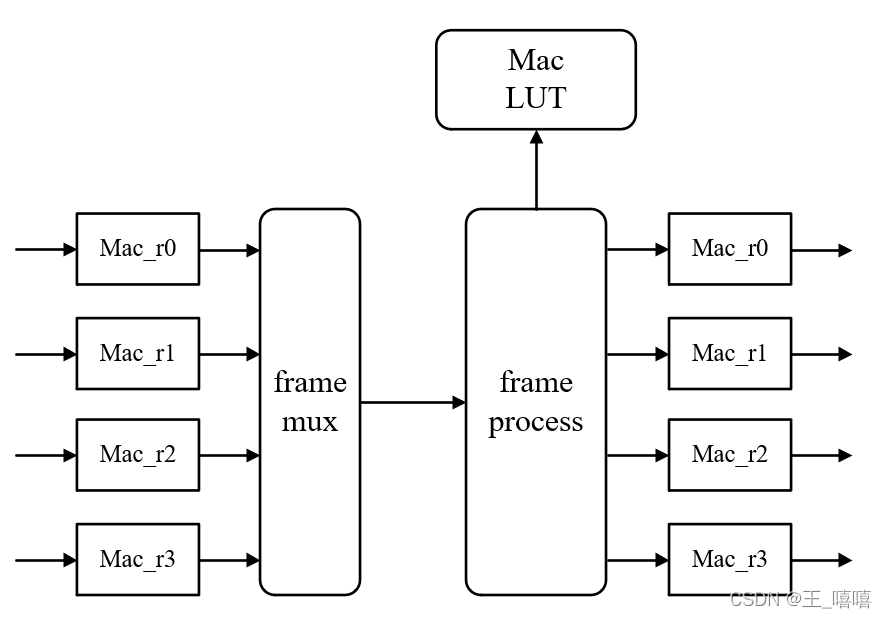

ethernet switch的整体架构如下,主要由MAC的收发控制器、帧合并、帧处理单元和MAC地址查找表组成。支持4 port输入输出。

基本功能如下:

- 接受PHY上传的MAC帧,并检测是否出错

- Mac address查找,地址逆向学习,发送与广播frame

- CRC校验码计算、帧格式添加并下发PHY

具体功能细节将在每个子模块设计中进行详细介绍与分析

接下去将分为MAC控制、帧合并,处理单元、Mac地址LUT以及队列管理四部分进行设计

搜索关注我的微信公众号【IC墨鱼仔】,获取我的更多IC干货分享!

版权声明:本文为sz_woshishazi原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明。