文章目录

写在前面:最近在实习中学习数字验证,每天学习的内容会整理记录下来。首先是对功能验证的理解。本文参考资料为维基百科-Functional Verification词条与文章《The ABCs of functional verification techniques》。如有任何理解有误之处,请务必在评论区指出,感谢!

功能验证是验证一个电路设计是否与预期的设计规范 (Design Specification) 相符合的过程。在功能验证中,有个前提假设是设计规范是正确的(在此不去讨论设计规范的正确性)。这是IC设计流程里较有挑战难度的一步,也是可能导致IC返工的重要原因。

功能验证的目的

- 验证各个IP的功能正确性

- 验证内部模块的通信

- 验证外部模块的通信

- 验证端到端的功能路径

- 验证焊盘Pad的连接

- 验证时钟CLK与复位RST电路

- 验证上电和掉电序列

- 验证所有IP集成的完整性

五大验证技术

功能验证技术有静态验证、功能仿真、FPGA原型验证、硬件仿真、与UVM等。

1 静态验证 (Static Verification)

静态验证不进行电路仿真,输入激励,而是直接通过辅助工具来验证一些预定义的规则,如语法检查、语义检查等。它能够在IC设计流程的早期(RTL代码刚完成时),对设计进行一个初步验证,不需要波形激励或完备验证环境的搭建。在静态验证中,也不对时序进行检查。

- 目的

静态验证的目的是在RTL层减少验证成本。 - 静态验证的方法

静态验证 { 跨复位域检查 R e s e t D o m a i n C r o s s i n g ( R D C ) 跨时钟域检查 C l o c k D o m a i n C r o s s i n g ( C D C ) 语法语义检查 L i n t 形式验证 F o r m a l V e r i f i c a t i o n 静态检查 S t a t i c C h e c k s \text{静态验证} \begin{cases} \text{跨复位域检查 }Reset Domain Crossing(RDC) \\ \text{跨时钟域检查 }Clock Domain Crossing(CDC) \\ \text{语法语义检查 }Lint \\ \text{形式验证 }Formal Verification \\ \text{静态检查 }Static Checks \end{cases}静态验证⎩⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎧跨复位域检查 ResetDomainCrossing(RDC)跨时钟域检查 ClockDomainCrossing(CDC)语法语义检查 Lint形式验证 FormalVerification静态检查 StaticChecks - 静态验证的优点

(1)在IC设计早期发现bug

(2)减少时间成本

(3)能够对设计整体进行静态验证,较为稳定可靠,迅速,详尽

(4)对大型设计的验证也较为容易

Mentor提供了许多用于静态与形式验证的解决方案与应用,如Questa形式验证, Questa跨时钟域检查(CDC),Questa跨复位域检查(RDC)等。

2 功能仿真 (Functional Simulation)

功能仿真是指通过软件仿真,来验证电路设计的功能行为(functional behavior)。它不考虑电路内部逻辑与互连的延时。

目的

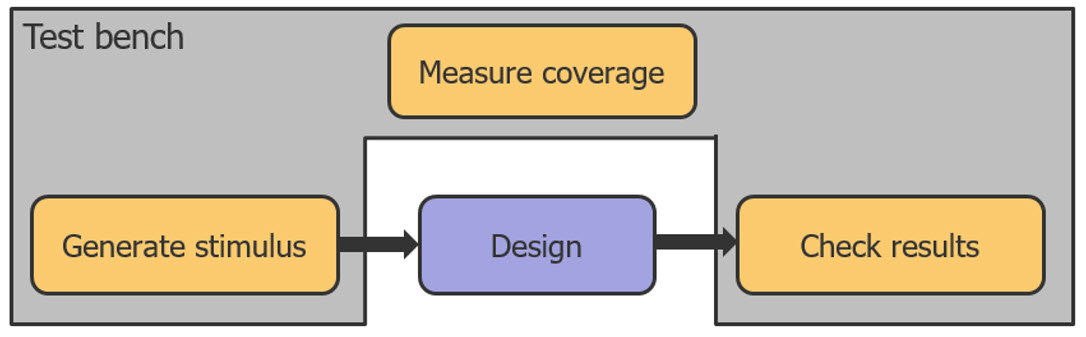

仿真的目的是进行各个IP或IC模块层次的验证。系统层次的验证无法通过功能仿真实现。仿真的搭建Simulation Setup

步骤流程

创建一个testbench -> 在testbench中对DUT实例化 -> 提供激励stimuli -> 在仿真器simulator中编译testbench与DUT -> 运行仿真器 -> 观测输出 -> 验证DUT的逻辑是否与预期相同优点

(1)能够较快速地搭建一个仿真

(2)对DUT的结果可视化较好(输出波形可直接观测)

(3)能够在早期找出DUT的bugs

(4)能够验证DUT的边界情况corner cases

(5)成本不昂贵缺点

(1)需要跑仿真,速度很慢,耗时较长

(2)复杂的设计不容易仿真

(3)难以对整个IC进行验证

(4)无法全部覆盖所有可能的情况scenarios与状态states

(5)无法验证是否存在软件上的问题

(6)缺少对时序相关问题的验证

对于功能仿真,Mentor QuestaSim工具目前是较为主流的,它支持Verilog, System Verilog, VHDL, SystemC, SVA, UPF, UVM等,能够实现高性能、高容量的仿真以及统一的高级调试debug和功能覆盖functional coverage功能。

3 FPGA原型验证 (FPGA Prototyping)

FPGA的原型验证是在FPGA上对IC系统进行功能上的验证。近年来随着IC复杂性的提高与市场的需求增大,FPGA原型验证始终是重要的验证方式。

- 目的

FPGA原型验证的目的是通过对电路设计进行实时的数据信号驱动,验证其是否还能如期运行,且外部接口能否正确工作。 - 步骤流程

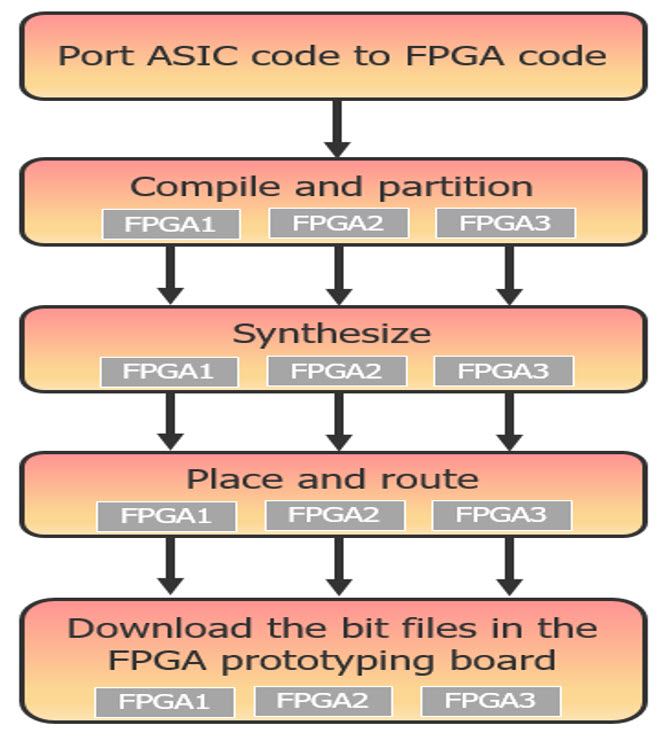

将ASIC代码转换成FPGA代码 -> 编译与对设计拆分 -> 综合 -> 布局布线 -> 从FPGA上下载比特流文件bit files

- 优点

(1)速度快,减少了设计->产品->市场的时间

(2)能够在设计早期进行软件开发与检验

(3)对于航空、军事、医疗等重要IP的验证很有用

(4)能够对整个IC进行验证

(5)降低了IC返工的风险 - 缺点

(1)相对硬件仿真器emulator而言,编译较慢

(2)对设计进行拆分时容易出错

(3)ASIC到FPGA的时钟转换较复杂

(4)FPGA与FPGA之间的连接比较受限

(5)FPGA的debug能力很有限

(6)将ASIC代码转换为FPGA代码的过程很耗时

(7)搭建FPGA的验证环境昂贵且耗时

4 硬件仿真 (Emulation)

硬件仿真Emulation,也叫硅前验证,是在硬件仿真器上对系统进行功能性验证的过程。硬件仿真器能够处理系统层次的设计(如C, C++, SystemC代码),也能够处理RTL设计(如Verilog, VHDL代码)。硬件仿真器emulators比软件仿真simulators快很多,一个需要花几天时间进行软件仿真的设计,用硬件仿真只需要几个小时。

- 目的

硬件仿真是为了通过给实时的数据输入,从系统层面来发现问题,进而验证系统的完整性,也可用于嵌入式软件的开发。 - 步骤流程

硬件仿真的过程与FPGA原型验证的过程类似,把FPGA换成硬件仿真工具即可。 - 优点

(1)比软件仿真快很多

(2)比FPGA原型验证的结果可行性更好,因此具有更好的debug能力

(3)能够对多个设计进行并行验证

(4)类似软件仿真,硬件仿真能够人为暂停,并之后从暂停处继续运行/仿真

(5)能够验证嵌入式软件 - 缺点

(1)比软件仿真的编译速度更慢

(2)很昂贵

(3)建立时间很长,需要花费很多时间来搭建环境

(4)无法覆盖所有的功能路径functional paths

Mentor的Veloce Strato硬件仿真平台是主流的高性能、高容量硬件辅助解决方案,能够用于嵌入式系统与SoC的验证。

5 UVM通用验证方法学 (Universal Verification Methodology)

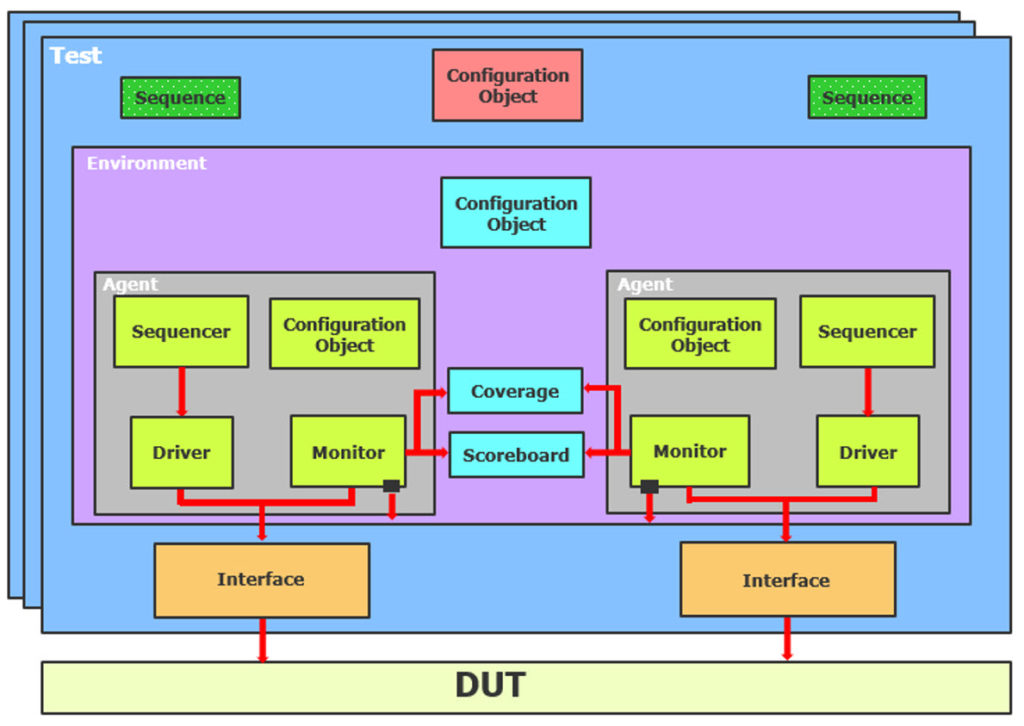

UVM是已经定义好testbench结构的代码规范集合。它用System Verilog进行编写,并提供了System Verilog的一些类库(SV base class libary, BCL),能够搭建高级可复用的验证组件。

- 目的

许多IP都是非常复杂的,验证过程十分耗时。标准的testbench是难以复用的,对于新的IP,验证工程师需要重头开始编写testbench。因此一个系统性的验证方法学呼之欲出。UVM具有固定的testbench结构,使其高度可复用,进而节省大量时间。 - UVM架构

UVM架构包含以下组件:

(1)配置对象Configuration Object:用于配置环境、代理agent与测试test

(2)Sequencer:向driver发送序列sequences

(3)Driver:将序列sequences转换成pin wiggles

(4)接口Interface:帮助testbench与DUT进行数据通信

(5)监视器Monitor:检测接口interface上的转换(通信)transistion

(6)Coverage:从监视器monitor收集覆盖率coverage信息

- 优点

(1)减少代码编写的人力成本,具有高度可复用性

(2)支持有约束条件的随机验证方法学

(3)能够大量产生激励

(4)缩短了验证的周期

(5)主流的仿真软件与硬件仿真器都支持 - 缺点

(1)基本来说没有缺点,除了需要额外学习UVM技术知识

总结

功能验证是IC设计周期中非常重要的一环。电路设计必须在早期进行功能验证以消除任何潜在的bug。随着设计技术的发展,验证工程师应该要尽量迅速适应最新的验证方法学。