主要参考正点原子的Linux驱动开发篇

文章目录

前言

一般 Cortex-A 片自带的 RAM 很小,比如 I.MX6U 只有 128KB 的 OCRAM。如果要运行 Linux 的话完全不够用的,所以必须要外接一片 RAM 芯片,I.MX6U 支持 LPDDR2、LPDDR3/DDR3。

I.MX6U-ALPHA开发板上选择的是 DDR3,本章就来学习如何驱动 I.MX6U-ALPHA 开发板上的这片 DDR3。

DDR内存简介

RAM和ROM

RAM-随机存储器

可以随时进行读写操作,速度很快,掉电以后数据会丢失。比如内存条、SRAM、SDRAM、DDR 等都是 RAM。RAM 一般用来保存程序数据、中间结果。

ROM-只读存储器

相比于RAM,向 ROM 或者 Flash 写入数据要复杂很多,因此意味着速度就会变慢(相比 RAM),但是

ROM 和 Flash 可以将容量做的很大,而且掉电以后数据不会丢失,适合用来存储资料,比如音乐、图片、视频等信息。(现在一部分的ROM也可以写入数据)。

Flash EEPROM

电可擦除可编程只读存储器(EEPROM),在最基础的ROM-可擦除可编程只读存储器(EPROM)基础上发展而来,集成度不高、价格较贵。

Flash EEPROM,后面发展出的一种EEPROM,可擦可写断电不丢失数据,集成度高、成本低,因此成为主流的程序ROM存储器。

区别

RAM 速度快,可以直接和 CPU 进行通信,但是掉电以后数据会丢失,容量不容易做大(和同价格的 Flash 相比)。ROM(目前来说,更适合叫做 Flash)速度虽然慢,但是容量大、适合存储数据。

SRAM-静态随机存储器

(Static Random-Access Memory)

“静态”指的是只要 SRAM 上电,那么 SRAM 里面的数据就会一直保存着,直到 SRAM 掉电。

SRAM 价格高,容量小,但是读写无需刷新,读写速度快!所以 SRAM通常作为 SOC 的内部 RAM 使用或 Cache 使用。比如 STM32 内存的 RAM 或 I.MX6U 内部的OCRAM 都是 SRAM。

SDRAM-同步动态随机存储器

(Synchronous Dynamic Random Access Memory)

“同步”的意思是 SDRAM 工作需要时钟线,“动态”的意思是 SDRAM 中的数据需要不断的刷新来保证数据不会丢失,“随机”的意思就是可以读写任意地址的数据。

与 SRAM 相比,SDRAM 集成度高、功耗低、成本低、适合做大容量存储,但是需要定时刷新来保证数据不会丢失。因此 SDRAM 适合用来做内存条,SRAM 适合做高速缓存或 MCU内部的 RAM。

SDRAM 目前已经发展到了第五代,分别为:

SDRAM、

DDR SDRAM、

DDR2 SDRAM、

DDR3 SDRAM、

DDR4 SDRAM、

DDR5 SDRAM。

DDR简介

DDR简介

DDR的全称其实是DDR SDRAM(Double Data Rate SDRAM),SDRAM(同步动态随机存取内存)可以看作一种特殊的DRAM(动态随机存取内存)。一般的DRAM只有一个异步接口,采用异步传输的方式,异步传输技术简单,也比较稳定,但是数据的传输速率相对较慢。SDRAM除了异步接口,还多了一个同步接口。同步接口需要数据发送方和接收方有一个统一的时钟信号,技术相对复杂,相应的传输速率和并发度都更高。

DDR其实就是具有双倍数据传输率的SDRAM,在DRAM的基础上快上加快.

DDR控制器-MMDC

MMDC 就是 I.MX6U的内存控制器,用于连接控制DDR。

MMDC 是一个多模的 DDR 控制器,可以连接 16 位宽的 DDR3/DDR3L、16 位宽的 LPDDR2,MMDC 外设包含一个内核(MMDC_CORE)和 PHY(MMDC_PHY)。

DDR3初始化与测试

利用NXP官方提供的ddr_stress_tester软件对DDR进行测试。

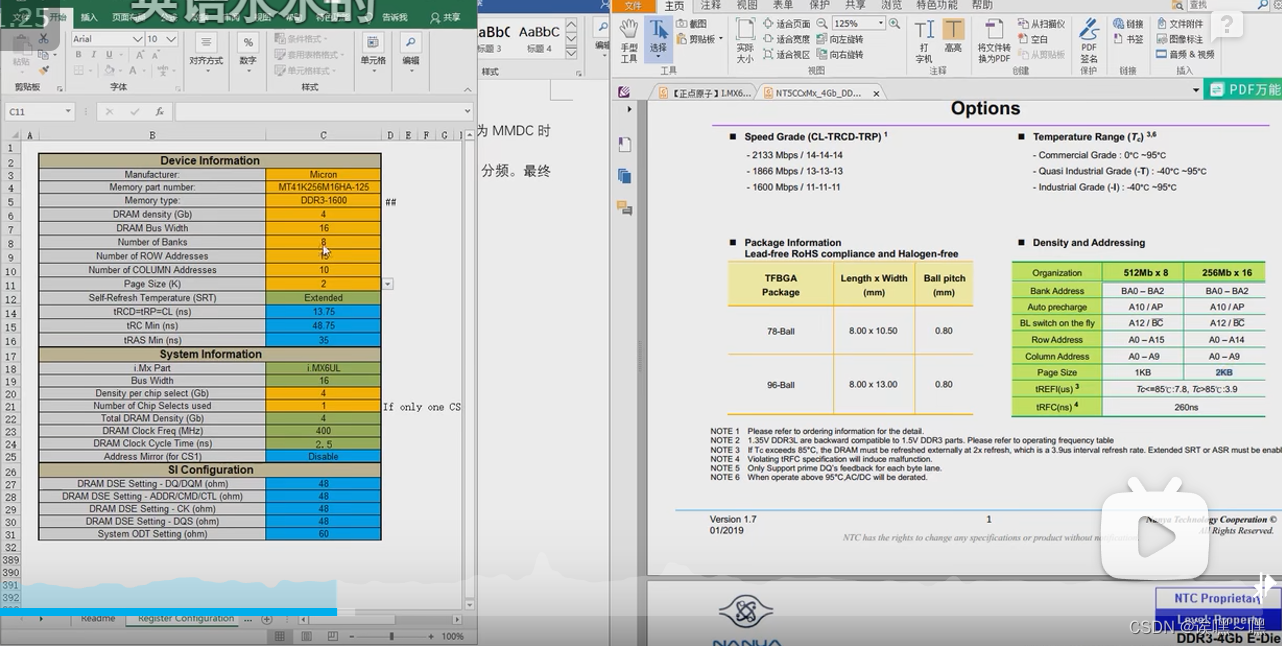

根据NXP官方提供的配置Excel文件初始化

修改Register Configuration内容,RealView.inc会同步更新。

校准值

Write leveling calibration

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00000000

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00050005

Read DQS Gating calibration

MPDGCTRL0 PHY0 (0x021b083c) = 0x0140013C

MPDGCTRL1 PHY0 (0x021b0840) = 0x00000000

Read calibration

MPRDDLCTL PHY0 (0x021b0848) = 0x40403034

Write calibration

MPWRDLCTL PHY0 (0x021b0850) = 0x40403A30

校准后进行超频测试。