相关概念

半加:只考虑两个加数本身,而没有考虑低位进位的加法运算。

半加器:实现半加运算的逻辑电路。

全加器:能进行被加数,加数和来自低位的进位信号相加,并根据求和结果给出该位的进位信号

串行进位:将低位的进位输出信号接到高位的进位输入端,任一位的加法运算必须在低一位的运算完成后进行。

加法运算

1. 半加器

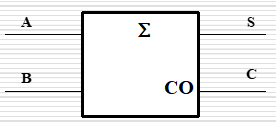

(1)逻辑符号

- A,B:两个一位二进制加数。

- S:和数。

- C:进位数。

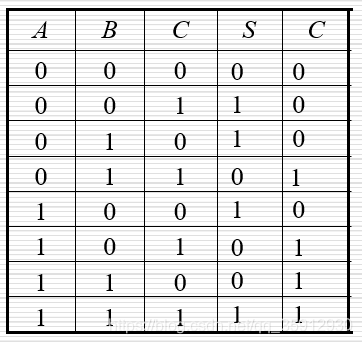

(2)真值表

2. 全加器

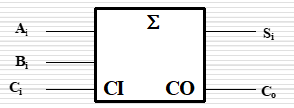

(1)逻辑符号

- A i :被加数。

- B i :加数。

- C i :低位进位数。

- S i :本位和数。

- C i :向高位进位数。

(2)真值表

3. 多位数加法器

多位数加法器只能由 全加器 构成

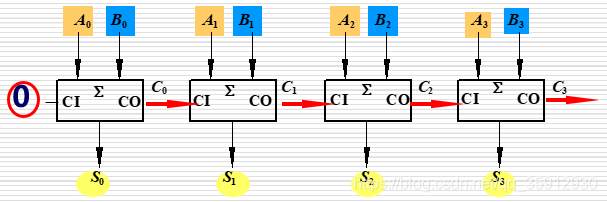

(1) 串行进位加法器

-

工作原理:第一个全加器根据A 0 、B 0 和CI中的进位信号,输出最低位和数S 0 ,把进位信号输出给下一个的全加器,这个全加器根据拿到的进位信号和A、B的输入信号重复上述操作。

-

优点:电路结构简单。

-

缺点:运算速度慢。

(2) 并行(超前)进位加法器

-

工作原理,电路设计时就完成了进位信号的运算,多个全加器同时拿到进位信号和A、B输入信号,一起计算,一起输出。

-

优点:运算速度快。

-

缺点:电路结构复杂。

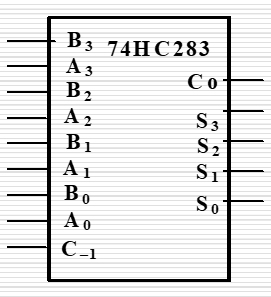

4. 集成4位超前进位加法器【74HC283】

(1)逻辑符号:

片的内部是并行进位的。

- A 3 A 2 A 1 A 0 :四位二进制加数。

- B 3 B 2 B 1 B 0 :四位二进制加数。

- S 3 S 2 S 1 S 0 :和数。

- C -1 :低位来的给A 0 的进位信号。

- C 0 :A 3 B 3 向高位的进位信号。

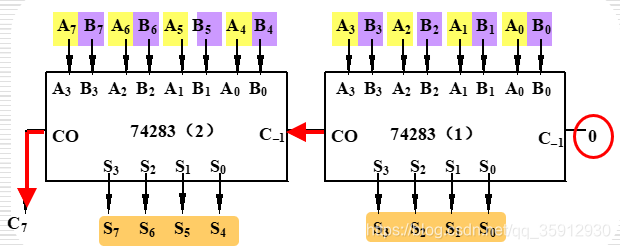

(2)位数拓展: (串联)8位二进制数加法器

两芯片之间是串行进位的。

减法运算

转换成补码的加法运算。

版权声明:本文为qq_35912930原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。